antial only

# SPCA554A

SUMPTER

# **Advanced Mobile Imaging Controller**

## Preliminary

APR. 08, 2004

Version 0.2

SUNPLUS TECHNOLOGY CO. reserves the right to change this documentation without prior notice. Information provided by SUNPLUS TECHNOLOGY CO. is believed to be accurate and reliable. However, SUNPLUS TECHNOLOGY CO. makes no warranty for any errors which may appear in this document. Contact SUNPLUS TECHNOLOGY CO. to obtain the latest version of device specifications before placing your order. No responsibility is assumed by SUNPLUS TECHNOLOGY CO. for any infringement of patent or other rights of third parties which may result from its use. In addition, SUNPLUS products are not authorized for use as critical components in life support devices/ systems or aviation devices/systems, where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user, without the express written approval of Sunplus.

## **Table of Contents**

#### **PAGE**

| 1. | . OVERVIEW                           | 5  |

|----|--------------------------------------|----|

|    | 1.1. INTRODUCTION                    | 5  |

|    | 1.2. TERMINOLOGY                     | 5  |

| 2. | . INTERFACE DESCRIPTION              | 6  |

|    | 2.1. HOST INTERFACE                  | 6  |

|    | 2.1.1. Pin description               | 6  |

|    | 2.1.2. Parallel Interface            | 8  |

|    | 2.1.3. I2C Interface                 | 10 |

|    | 2.1.4. SPI Interface                 |    |

|    | 2.1.5. RS232 Interface               |    |

|    | 2.2. SENSOR INTERFACE                | 14 |

|    | 2.2.1. Pin Description               | 14 |

|    | 2.2.2 I2C master port                |    |

|    | 2.2.3 Three-wired master serial port | 18 |

|    | 2.2.4 Data transfer timing           | 20 |

|    | 2.3. STORAGE INTERFACE.              |    |

|    | 2.4. USB INTERFACE                   |    |

|    | 2.5. Audio Interface                 |    |

|    | 2.6. DISPLAY INTERFACE               |    |

|    | 2.6.1. 18-bit RGB interface          |    |

|    | 2.6.2. 18-bit Memory interface       |    |

|    | 2.6.3. 9-bit Memory interface        |    |

|    | 2.6.4. 16-bit Memory interface       |    |

|    | 2.6.5. 8-bit Memory interface        |    |

|    | 2.6.6. YUV data output               |    |

| 3. | . RESET AND IO-TRAP                  | 37 |

| 4. | . BOOT SEQUENCE                      |    |

|    | 4.1. BOOT FROM INTERNAL BOOT ROM     |    |

|    | 4.2. BOOT FROM THE HOST PROCESSOR    |    |

| 5. | . POWER MANAGEMENT                   | 40 |

|    | 5.1. INTERNAL CLOCK CONTROL          | 40 |

|    | 5.2. DEEP POWER DOWN MODE            | 41 |

| 6. | . FUNCTION DESCRIPTION               | 42 |

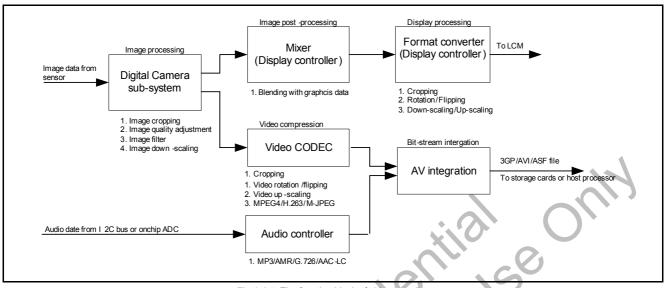

|    | 6.1. OPERATION OVERVIEW              | 42 |

|    | 6.1.1. Camera preview                | 43 |

|    | 6.1.2. Still image capture           |    |

|    | 6.1.3. Still image playback          | 46 |

|    | 6.1.4. Video recoding                | 46 |

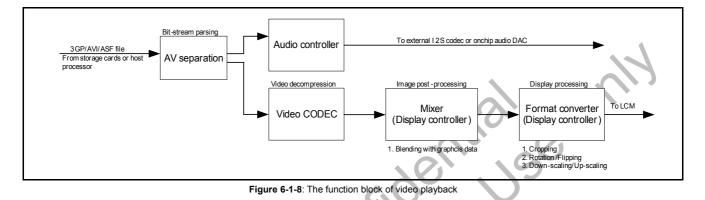

|    | 6.1.5. Video playback                | 48 |

|    | 6.1.6. Screen saver                  | 48 |

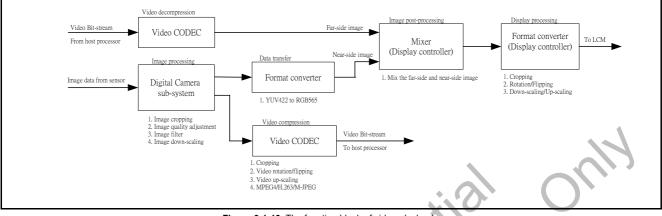

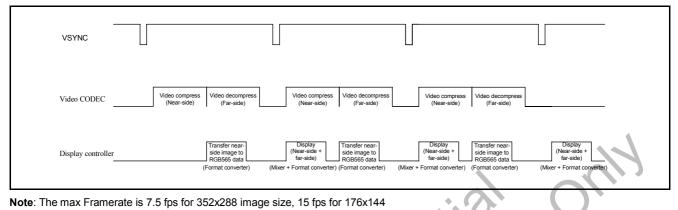

|    | 6.1.7. Video conference              | 49 |

|    | 6.2. Host Bridge                     | 50 |

|      | 6.2.1. Host bridge control registers               | 51  |

|------|----------------------------------------------------|-----|

|      | 6.2.2. Main Page Register and Mirror Page Register | 57  |

|      | 6.2.3. Vendor command communication flow           | 58  |

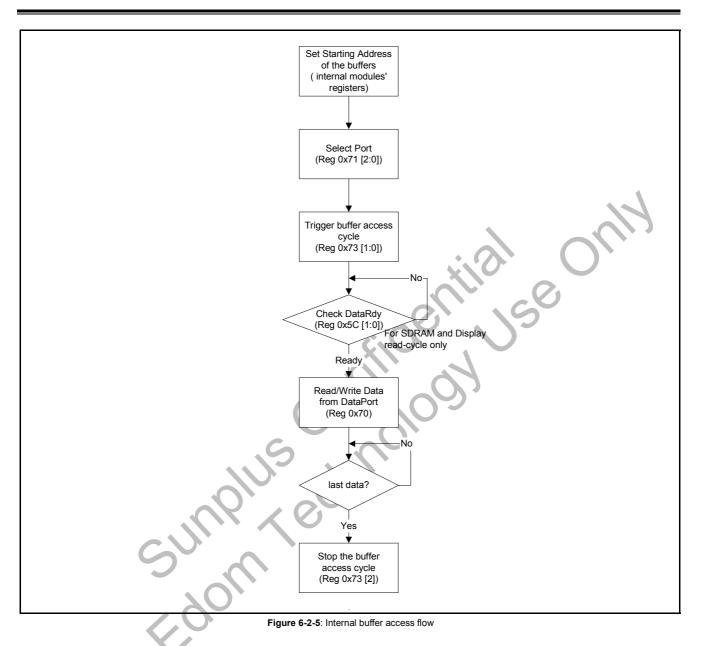

|      | 6.2.4. Internal buffer access                      | 59  |

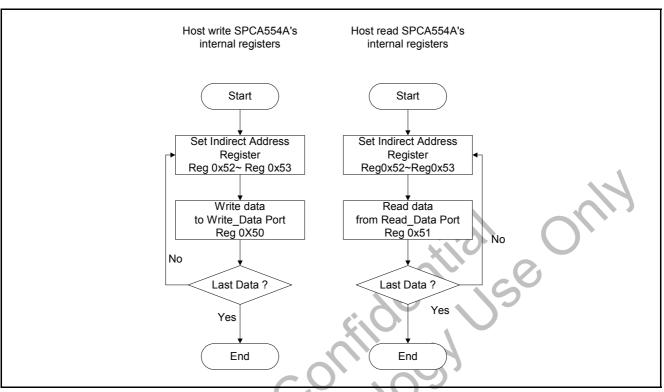

|      | 6.2.5. Internal register access                    | 60  |

| 6.3. | EMBEDDED CPU                                       | 61  |

|      | 6.3.1. Addressing space partition                  | 62  |

|      | 6.3.2. Priority interrupt controller               | 64  |

| 6.4. | SENSOR CONTROL                                     |     |

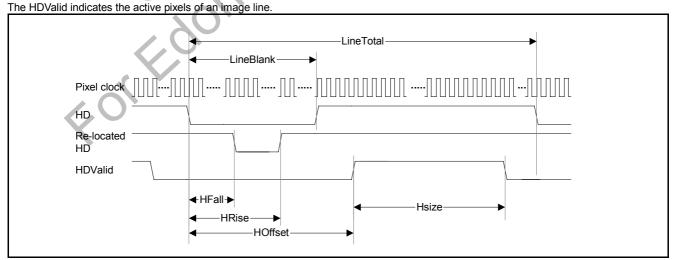

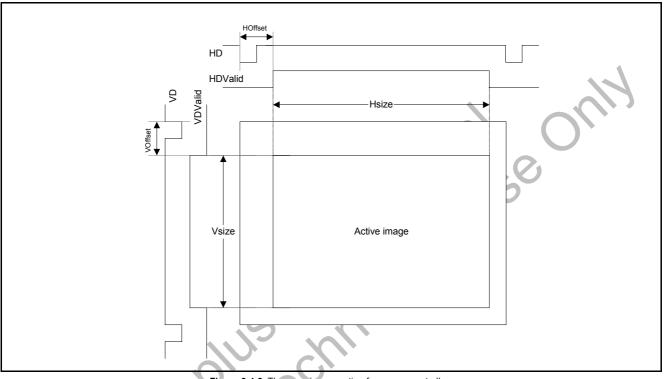

|      | 6.4.1. Synchronization/ Valid signals generation   |     |

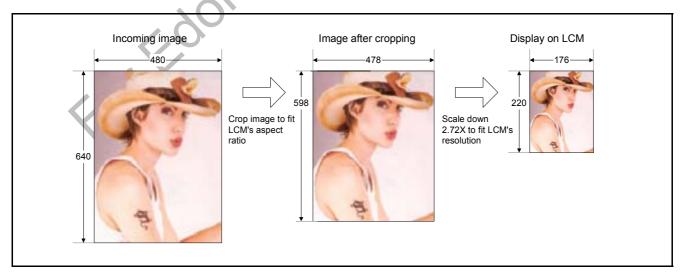

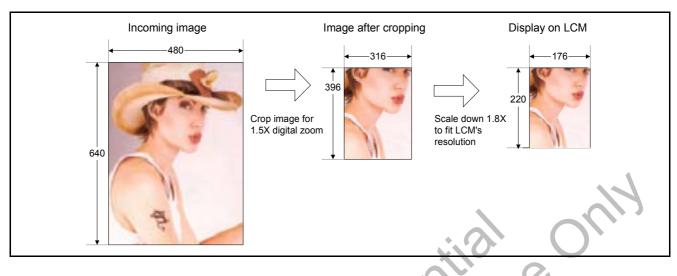

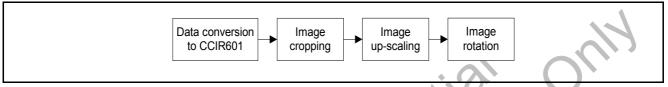

|      | 6.4.2. Image cropping                              |     |

|      | 6.4.3. Exposure Time and Flash Light Control       |     |

| 6.5. | COLOR DSP                                          | 69  |

| 6.6. | JPEG AND VIDEO CODEC                               | 71  |

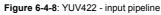

|      | 6.6.1. Pre-Processing                              | 71  |

|      | 6.6.2. JPEG engine                                 |     |

|      | 6.6.3. Video engine                                | 73  |

| 6.7. | Memory Controller                                  | 74  |

|      | 6.7.1. Camera Image of YUV422 format               |     |

|      | 6.7.2. Camera image of YUV420 format               |     |

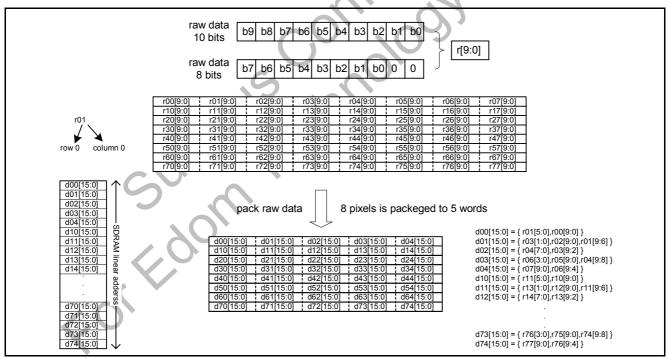

|      | 6.7.3. Camera image of Raw data format             | 77  |

| 6.8. | CAMERA IMAGE CONTROLLER                            | 77  |

|      | 6.8.1. Scaling                                     |     |

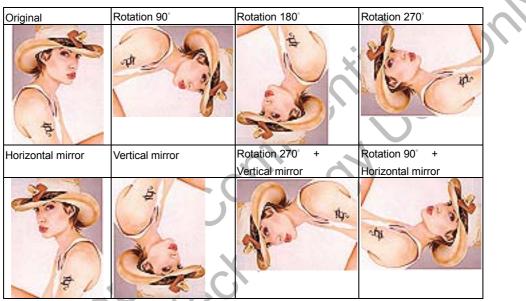

|      | 6.8.2. Rotation and mirror                         |     |

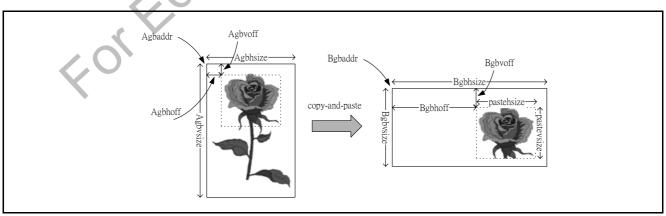

|      | 6.8.3. BitBlt of camera image data                 | 78  |

|      | 6.8.4. Bad Pixel Concealment                       | 79  |

|      | 6.8.5. YUV420-to-YUV422 conversion                 | 79  |

|      | STORAGE MEDIA CONTROLLER                           |     |

| 6.10 | USB Controller                                     | 80  |

| 6.11 | AUDIO CONTROLLER                                   | 81  |

| 6.12 | DMA Controller                                     | 82  |

|      | 6.12.1. General purpose DMA channel                | 84  |

|      | 6.12.2. Secondary DMA channel                      | 84  |

|      | 6.12.3. DRAM-to-DRAM DMA channel                   | 85  |

|      | 6.12.4. FAT acceleration                           | 85  |

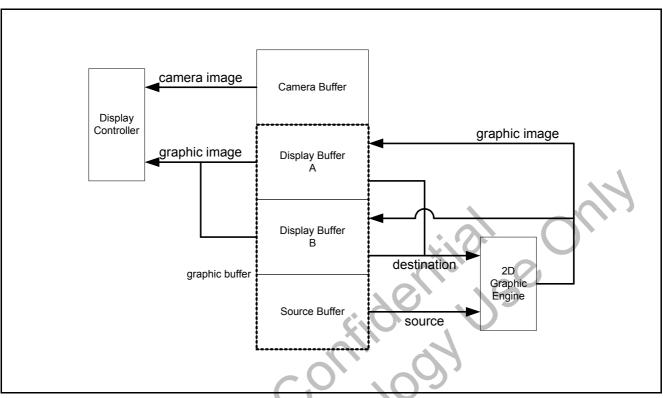

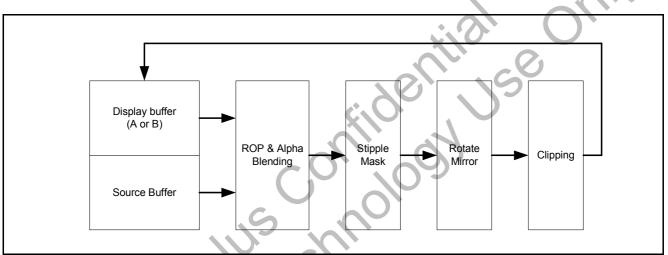

| 6.13 | 2D GRAPHICS ENGINE                                 | 85  |

|      | 6.13.1. Resolution and color system                | 86  |

|      | 6.13.2. BitBLT                                     | 88  |

|      | 6.13.3. Sprite                                     | 93  |

|      | 6.13.4. Line drawing                               | 95  |

|      | 6.13.5. Gradient Fill                              | 96  |

| 6.14 | Display Controller                                 | 98  |

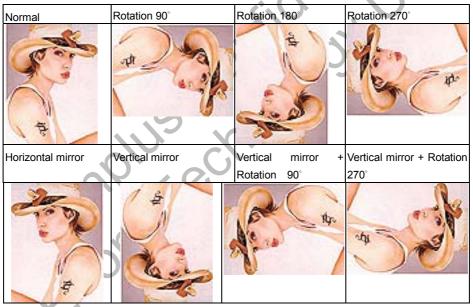

|      | 6.14.1. Geometrical Transformation                 | 98  |

|      | 6.14.2. Color Adjust of Camera Image               | 100 |

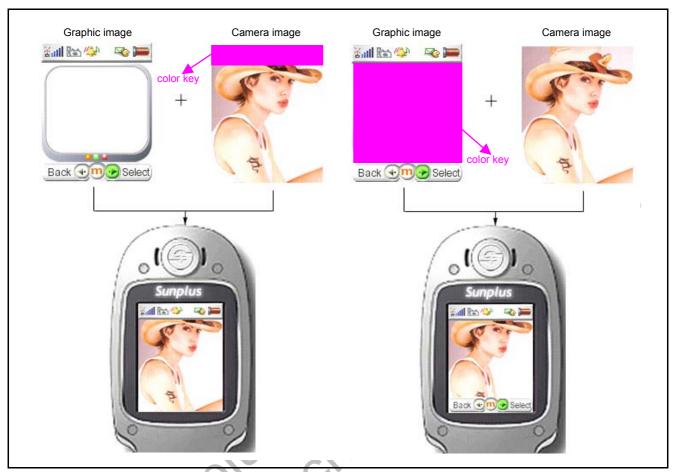

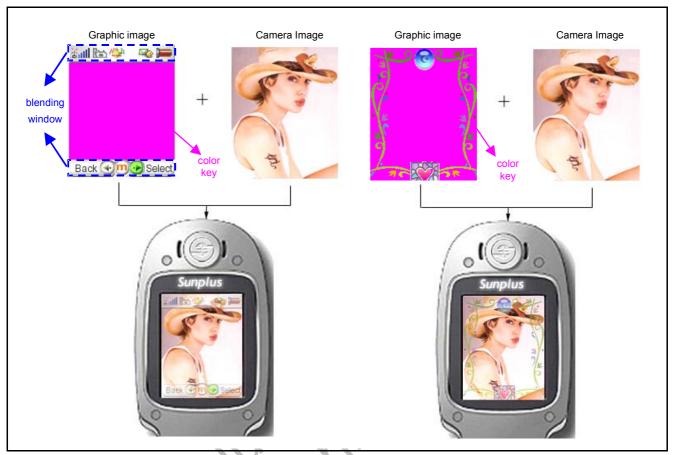

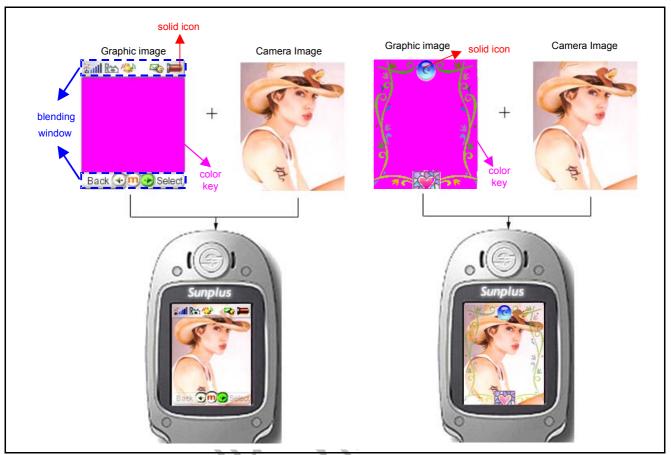

|      | 6.14.3. Mixer                                      | 101 |

|      |                                                    |     |

| 110 |

|-----|

|     |

|     |

|     |

|     |

|     |

For Food on the control of the contr

### ADVANCED MOBILE IMAGING CONTROLLER

#### **1.OVERVIEW**

#### 1.1. Introduction

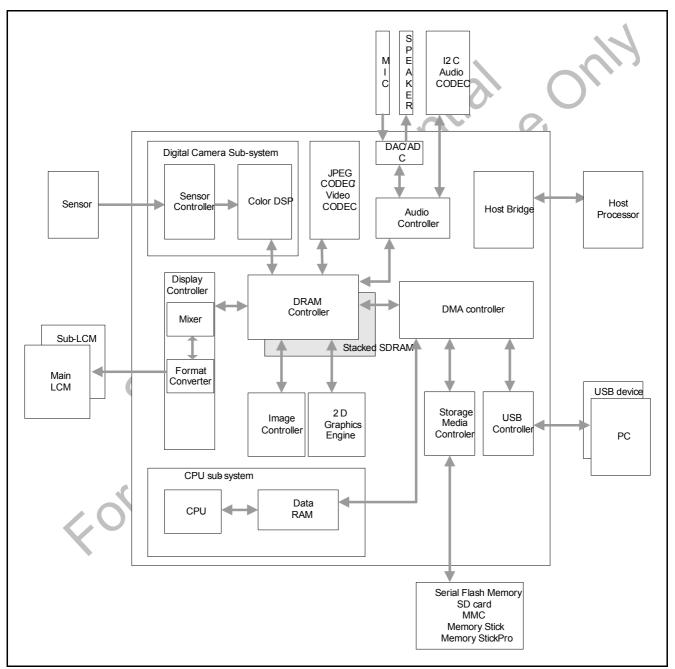

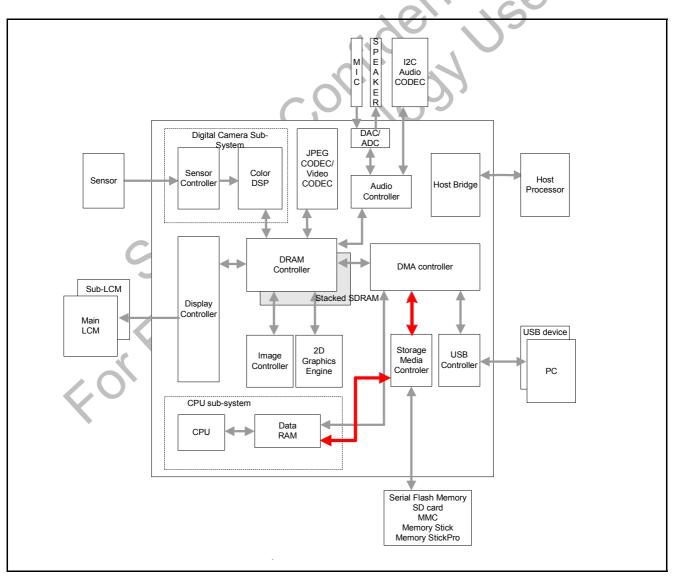

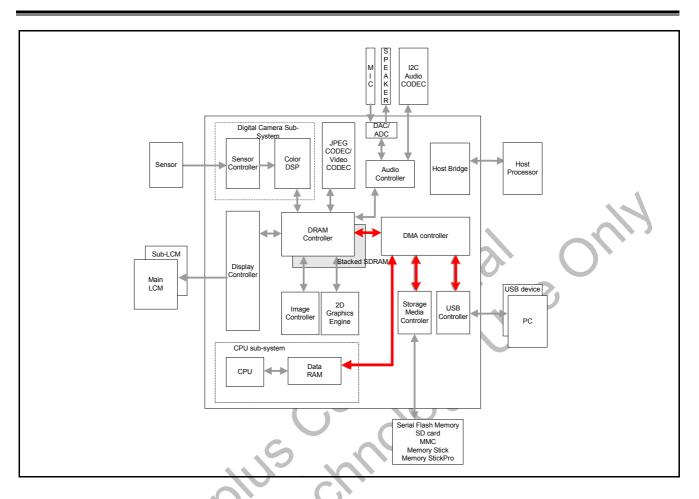

The SPCA554A is a multimedia processor targeting high-end mobile applications. The SPCA554A serves as a co-processor of the host (base-band) processor in a mobile phone. It handles all the multimedia functions required in a high-end mobile phone, such as digital camera functions, video camera functions, MP3 playback functions, JAVA functions, as well as rich OSD (on screen display) functions. Internal engines of the SPCA554A include a digital camera processor, MPEG4/H.263 CODEC, JPEG CODEC, 2D graphics engine and a powerful 32-bit RISC processor. The powerful all-in-one functions of the SPCA554A make the implementation of multimedia mobile applications a straightforward task.

Chapter 2 describes all the interfaces of the SPCA554A in terms of their corresponding functionalities, options and interconnections to other modules in a mobile phone system. Chapter 3 describes reset timing requirements and the power-on IO-TRAP mechanism. In Chapter 4 the internal clock distribution and power management of the SPCA554A will be discussed. Next, chapter 5 will explain SPCA554A boot flow and options. Finally, chapter 6 has detailed information about the function of individual internal modules.

#### 1.2. Terminology

|   | ADC:     | Analog to digital converter                                       |

|---|----------|-------------------------------------------------------------------|

|   | AE:      | Auto exposure control                                             |

|   | AWB:     | Auto white balance control                                        |

|   | BitBLT : | Bit Block Transfer                                                |

|   | CODEC:   | Encoder and decoder                                               |

|   | DAC:     | Digital to analog converter                                       |

|   | 180:     | Intel 80xx CPU protocols                                          |

|   | I2C:     | Inter IC Bus. I <sup>2</sup> C bus is usually used to control the |

|   |          | CMOS sensor. The SPCA554A can also be                             |

|   |          | controlled through a separate I2C bus                             |

|   | 12S:     | Inter IC Sound. The I <sup>2</sup> S serial bus is used in        |

|   | <b>C</b> | SPCA554A to transfer to/from the external audio                   |

|   |          | CODEC                                                             |

| l | IO-TRAP: | In the reset period, SPCA554A latches IO-pin values               |

| Ì |          | for configuration settings                                        |

|   | LCM:     | Liquid crystal display module                                     |

|   | M68:     | Motorola 68000 CPU data protocols                                 |

| 4 | ROPs:    | Raster operations                                                 |

|   | SPI:     | serial peripheral interface                                       |

|   | VLC:     | Variable length coding. VLC is used in JPEG, MPEG                 |

|   |          | and H.263 CODEC                                                   |

|   | VSYNC:   | Vertical synchronization signal                                   |

|   | VVALID:  | Vertical valid signal of image                                    |

|   | VOP:     | Video object plane                                                |

|   | GOP:     | Group of object plane                                             |

|   |          |                                                                   |

#### 2.INTERFACE DESCRIPTION

The SPCA554A has six interfaces to be connected to external modules. They include the following:

- Host interface: To communicate with the host processor

- Sensor interface: Connects the SPCA554A to a CMOS sensor, CCD sensor module or TV decoder to get image input

- Display interface: Connect to an LCM

- Audio interface: Allows the SPCA554A to get audio input.

- Storage media interface: Allows the SPCA554A to store image data, audio data and video data to external storage cards.

- USB interface: communicates with a PC or other USB devices.

| IO-buffer | Description                                                                      |

|-----------|----------------------------------------------------------------------------------|

| ID        | Input buffer with programmable internal pull-down                                |

| IS        | Schmitt trigger input buffer                                                     |

| В         | Bi-directional buffer                                                            |

| BD        | Bi-directional buffer with programmable internal pull-down                       |

| BDS       | Bi-directional buffer with limited slew rate and programmable internal pull-down |

| 0         | Output buffer                                                                    |

| XI        | Crystal input buffer                                                             |

| XO        | Crystal output buffer                                                            |

| Р         | Power                                                                            |

| G         | Ground                                                                           |

Table 2-1: IO-buffer types used in the SPCA554A

#### 2.1. Host Interface

The host interface can be serial or parallel, depending on the requirement of applications. It is used by host processor controls through the host interface. The host processor can access internal registers of the SPCA554A, send host commands and data to the SPCA554A, or get status and data from the SPCA554A. Instead of programming the internal registers, the operational flow of the SPCA554A is controlled by a set of host commands. The host commands are a complete set of APIs for multimedia applications executed by the on-chip 32-bit RISC CPU. The RISC CPU interprets the host commands and performs corresponding operations and then sends the status back to the host processor. The SPCA554A supports the following types of host interfaces:

- 12C

- SPI interface mode 0, 1, 2 and 3

- RS232

- 8/16-bit parallel interface M68 mode

- 8/16-bit parallel interface i80 mode

The configuration of the host interface is selected by IO-TRAP settings. IO-TRAP mapping can be found in the SPCA554A datasheet. The following table lists the signal names in the various modes of the host interface. A detailed description of signal functions and timing is given in sections 2.1.1 through 2.1.5 and is as follows:

#### 2.1.1. Pin description

The following table lists the host interface pin usage in different host types:

| Pin Name |     | Pin Allocation In Different Host Interface Types |      |   |      |   |                   |     |                      | 10 |                     |   |                 |     |     |

|----------|-----|--------------------------------------------------|------|---|------|---|-------------------|-----|----------------------|----|---------------------|---|-----------------|-----|-----|

|          | I2C |                                                  | SPI  |   | RS23 | 2 | 8/16-bit Parallel | bus | 8-bit bus a<br>RS232 | nd | 8-bit bus an<br>I2C |   | 8-bit bus and s | SPI |     |

| HGPIO0   | SCL | I                                                | Cs_n | I | Rxd  | Ι | Cs_n              | Ι   | Cs_n                 | Ι  | Cs_n                | I | Cs_n            | I   | BDS |

| Pin Name |     | Pin Allocation In Different Host Interface Types |     |   |     |   |           |   |           | 10 |                   |   |           |   |     |

|----------|-----|--------------------------------------------------|-----|---|-----|---|-----------|---|-----------|----|-------------------|---|-----------|---|-----|

| HGPIO1   | SDA | в                                                | SCK | Т | Txd | 0 | A0        | Т | A0        | Ι  | A0                | Ι | A0        | Ι | BDS |

| HGPIO2   |     |                                                  | SI  | Т |     |   | Rd_n / En | Ι | Rd_n / En | Ι  | Rd_n / En         | Ι | Rd_n / En | I | BDS |

| HGPIO3   |     |                                                  | SO  | 0 |     |   | Wr_n / RW | Т | Wr_n / RW | Ι  | Wr_n / RW         | Ι | Wr_n / RW | Ι | BDS |

| HGPIO4   |     |                                                  |     |   |     |   | D0        | в | D0        | В  | D0                | В | D0        | В | BDS |

| HGPIO5   |     |                                                  |     |   |     |   | D1        | в | D1        | В  | D1                | В | D1        | В | BDS |

| HGPIO6   |     |                                                  |     |   |     |   | D2        | в | D2        | В  | D2                | В | D2        | В | BDS |

| HGPI07   |     |                                                  |     |   |     |   | D3        | в | D3        | В  | D3                | В | D3        | В | BDS |

| HGPIO8   |     |                                                  |     |   |     |   | D4        | в | D4        | В  | D4                | В | D4        | в | BDS |

| HGPIO9   |     |                                                  |     |   |     |   | D5        | в | D5        | В  | D5                | в | D5        | в | BDS |

| HGPIO10  |     |                                                  |     |   |     |   | D6        | в | D6        | в  | D6                | в | D6        | В | BDS |

| HGPIO11  |     |                                                  |     |   |     |   | D7        | в | D7        | в  | D7                | в | D7        | В | BDS |

| HGPIO12  |     |                                                  |     |   |     |   | D8        | в | Rxd       |    | SCL               | 1 | Cs_n      | Ι | BDS |

| HGPIO13  |     |                                                  |     |   |     |   | D9        | в | Txd       | 0  | SDA               | в | SCK       | Ι | BDS |

| HGPIO14  |     |                                                  |     |   |     |   | D10       | В |           |    | $\langle \rangle$ |   | SI        | Ι | BDS |

| HGPIO15  |     |                                                  |     |   |     |   | D11       | в |           |    |                   |   | SO        | 0 | BDS |

| HGPIO16  |     |                                                  |     |   |     |   | D12       | В | , i       |    |                   |   |           |   | BDS |

| HGPIO17  |     |                                                  |     |   |     |   | D13       | в |           |    |                   |   |           |   | BDS |

| HGPIO18  |     |                                                  |     |   |     |   | D14       | в |           |    | ·                 |   |           |   | BDS |

| HGPIO19  |     |                                                  |     |   |     |   | D15       | в |           |    |                   |   |           |   | BDS |

| BYPASS   |     |                                                  |     |   |     |   | S         | • |           |    |                   |   |           |   | BDS |

Table 2-2: Pin list of host interface

Note: BYPASS pin is input only.

HGPIO[19:0] are shared between different types of host interfaces. The SPCA554A always acts as a slave device of the selected bus type. For example, if the I2C bus type is selected, the SPCA554A is a slave device on the I2C bus. The host interfaces allows the SPCA554A to be controlled by an 8-bit parallel bus and a serial bus at the same time.

Note that there are certain pins not used in a specific types of host interfaces. These pins are automatically set to the GPIO function once the host type is selected by the IO-TRAP configuration. For example, HGPIO[2:19] are not used in I2C type host interfaces.

They are automatically set to GPIO pins after IO-TRAP terminates.

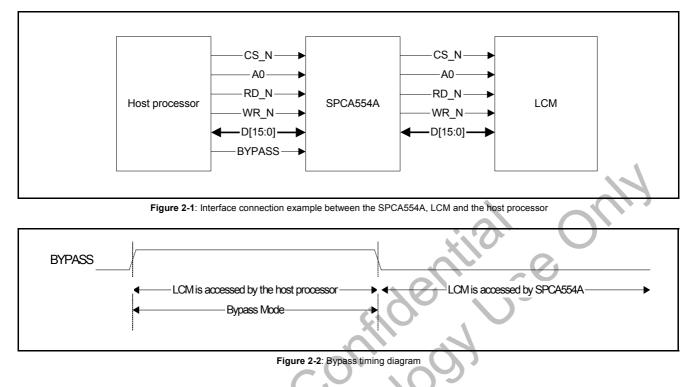

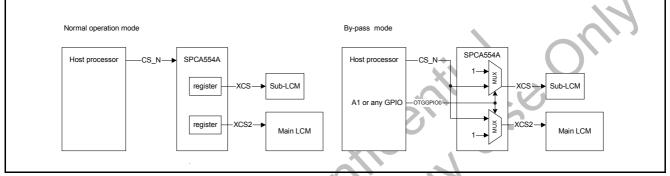

Pin 21 of the host interface is the bypass mode control signal. It is an active high signal. In the bypass mode, the LCM is accessed by the host processor. Otherwise, the LCM is accessed by the SPCA554A. The following diagram shows a typical interface connection between the SPCA554A, LCM and the host processor. Note that the SPCA554A is put into the suspend state in the bypass mode to reduce power consumption. Also note that internal modules do not respond to host commands in the bypass mode.

Preliminary

## SPCA554A

#### 2.1.2. Parallel Interface

Sections 2.1.2 to section 2.1.5 describe the host interface in terms of signal functions and hardware protocols.

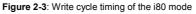

i80 Mode:

The signals of the i80 mode parallel interface are described below:

Cs\_n : Chip select to the SPCA554A. Can be active high or active low, depending on the configuration of IO-trap (Refer to Section 4.3).

- A0 : Address/data indicator. When low (logic 0), it indicates that the host is sending an address via the data bus. When High (logic 1), it means that the host is sending data.

- Wr\_n : write pulse.

Rd\_n : Read pulse.

D[15:0]: While the host is sending addresses to the SPCA554A, only D[6:0] are used as address bits. While transferring data, either from the host to the SPCA554A or from the SPCA554A to the host, both 8-bit data and 16-bit data are supported. If the 8-bit data bus is selected, data should be placed in low bytes; D[7:0].

| Write cycle timing |            |

|--------------------|------------|

| <u> </u>           |            |

|                    | CS_N       |

|                    | A0         |

|                    | WR_N       |

|                    | RD_N       |

| D[7:0              | D]/D[15:0] |

c.©

#### Read cycle timing

M68 Mode:

The signals of the m68 mode parallel interface are described below:

Cs\_n: Chip select to the SPCA554A. Its function is the same as in the i80 mode,

A0: Address /data indicator. The function is the same as in the i80mode.

RW: A read/write command indicator. Logic 0 indicates a write cycle, and logic 1 indicates a read cycle.

E: Enable signal. This signal is used in conjunction with the RW signal to generate the SPCA554 internal read/write pulse.

D[15:0]: Same as in the i80 mode.

Write cycle timing:

| CS_N<br>A0<br>RW<br>E<br>D[7:0]/D[15:0]<br>ADDR DATA0 DATA1 DATA2       |

|-------------------------------------------------------------------------|

|                                                                         |

| Figure 2-5: Write cycle timing of the M68 mode         ead cycle timing |

| CS_N                                                                    |

| A0                                                                      |

|                                                                         |

| RW                                                                      |

| E                                                                       |

| D[7:0]/D[15:0]                                                          |

|                                                                         |

Figure 2-6: Read cycle timing of the M68 mode

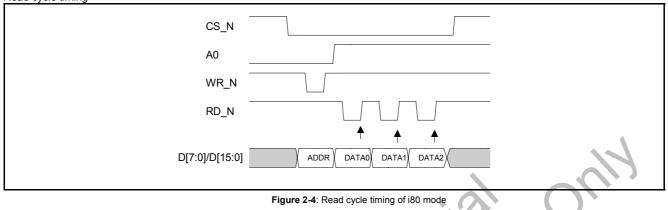

#### 2.1.3. I2C Interface

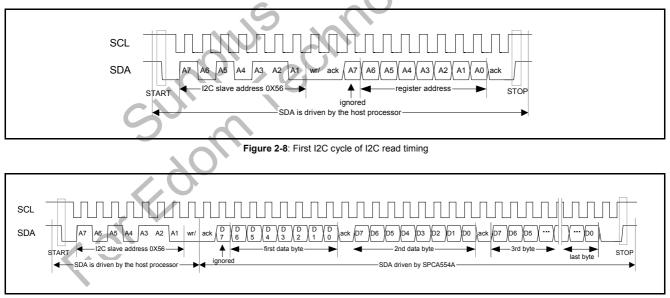

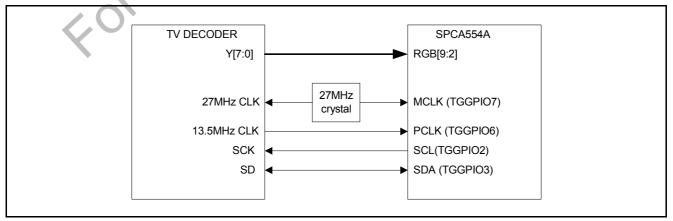

The host processor can also communicate with the SPCA554A through a I2C bus. In this case, the SPCA554A is a I2C slave from the host processor's point of view. As a I2C slave, the SPCA554A supports two alternative I2C slave addresses, depending on the IO-trap setting. The address can be 0X56 or 0X65. The address can be changed in case the mobile system has another I2C slave with a conflicting slave address. The following diagram shows the access timing. Note that the

register address field contains only 7 valid bits. Bit-7 of the address is ignored. The data field may contain multiple bytes when necessary. When multiple bytes follow the address byte, the data is written into (or read from) the same address. This is useful in some SPCA554A registers which are mapped to data ports of the internal memory. The multiple-byte data access enables burst access to the internal memory.

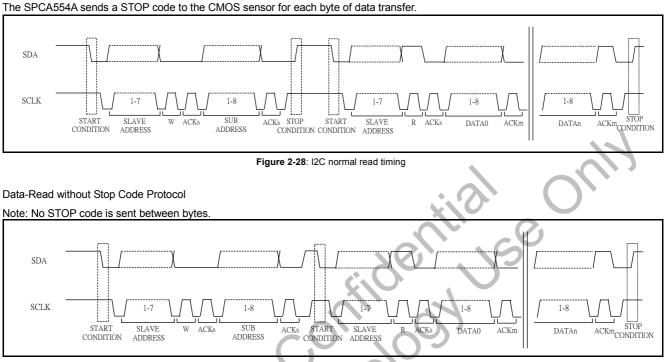

*Read timing*: To read a register value from the SPCA554A using a I2C bus, two I2C cycles are required. The first cycle sets the register address. The second cycle reads data from the register (or port) of the indicated address.

Figure 2-9: Second I2C cycle of I2C read timing

As long as the clocks are supplied to the SPCA554A, the data is written to the same address repeatedly. The SPCA554A automatically detects the stop condition of the I2C protocol and stops the burst read (or write) operation. Figure 2-7 ~Figure 2-9

shows when the SDA pin is driven by the host processor and when it is driven by the SPCA554A. Note that the "ACK" handshake is always driven by the I2C slave, i.e. by the SPCA554A.

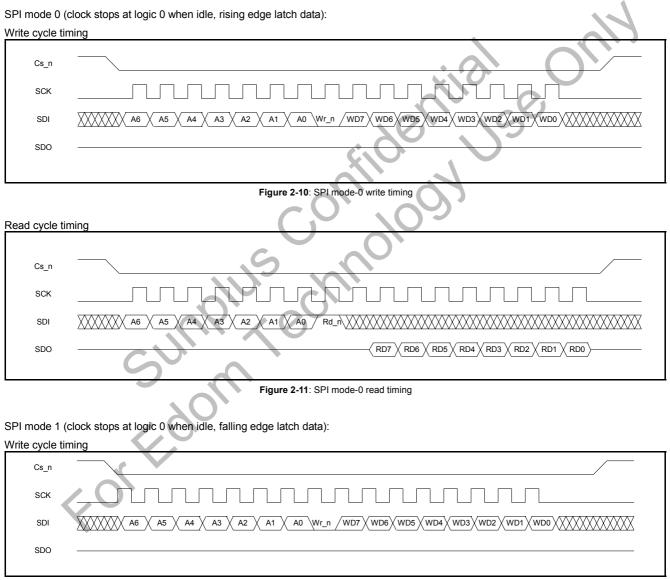

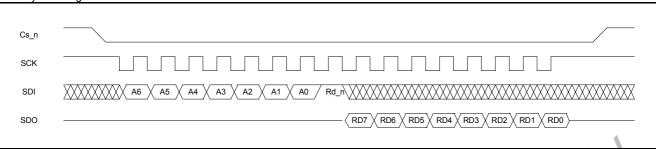

#### 2.1.4. SPI Interface

The following diagram shows the timing of SPCA554A internal register access via the SPI serial interface. The SPCA554A supports all SPI protocols, including mode-0, mode-1, mode-2 and mode-3.

A command transfer defines the access address and the access mode. The access mode can be read access or write access, depending on bit-7 of the transfer. Multiple data bytes can be transferred, following a command. For example, transferring a JFIF file to the SPCA554A requires all the data bytes to be written to the same image data port.

#### Figure 2-12: SPI mode-1 write timing

Read cycle timing

| Read cycle                |                                                                                                                                                                                                         |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cs_n                      |                                                                                                                                                                                                         |

| SCK                       |                                                                                                                                                                                                         |

| SDI                       | XXXXXX A6 X A5 X A4 X A3 X A2 A1 X A0 / Rd_n XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX                                                                                                                       |

| SDO                       | $\left( \frac{\text{RD7}}{\text{RD6}} \right) \left( \frac{\text{RD5}}{\text{RD4}} \right) \left( \frac{\text{RD3}}{\text{RD2}} \right) \left( \frac{\text{RD1}}{\text{RD0}} \right)$                   |

|                           | Figure 2-13: SPI mode-1 read timing                                                                                                                                                                     |

|                           |                                                                                                                                                                                                         |

| SPI mode 2<br>Write cycle | (clock stops at high when idle, falling edge latch data):<br>timing                                                                                                                                     |

| Cs_n                      |                                                                                                                                                                                                         |

| SCK                       |                                                                                                                                                                                                         |

| SDI                       | XXXXXX         A6         A5         A4         X         A2         X         A0         Wr_n         WD6         WD5         WD2         WD1         WD0         XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX |

| SDO                       |                                                                                                                                                                                                         |

|                           | Fig 2-14: SPI mode-2 writes timing                                                                                                                                                                      |

|                           | C                                                                                                                                                                                                       |

| Read cycle                | timing                                                                                                                                                                                                  |

| Cs_n                      |                                                                                                                                                                                                         |

| SCK                       |                                                                                                                                                                                                         |

| SDI                       | XXXXXX A6 A5 A4 A3 A2 A1 A0 Rd_n XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX                                                                                                                                   |

| SDO                       |                                                                                                                                                                                                         |

|                           | Figure 2-15: SPI mode-2 read timing                                                                                                                                                                     |

|                           | Figure 2-15. SF1 mode-2 lead unling                                                                                                                                                                     |

| SPI mode 3                | (clock stops at logic 1 when idle, rising edge latch data):                                                                                                                                             |

| Write cycle               | timing                                                                                                                                                                                                  |

| Cs_n                      |                                                                                                                                                                                                         |

| SCK                       |                                                                                                                                                                                                         |

| SDI                       | XXXXXXX A6 X A5 X A4 X A3 X A2 X A1 X A0 Wr_n /WD7 X WD6 X WD5 X WD4 X WD3 X WD2 X WD1 X WD0 X X X X X X X X X X X X X X X X X X X                                                                      |

| SDO                       |                                                                                                                                                                                                         |

| 1                         |                                                                                                                                                                                                         |

#### Figure 2-16: SPI mode-3 write timing

Read cycle timing

Figure 2-17: SPI mode-3 read timing

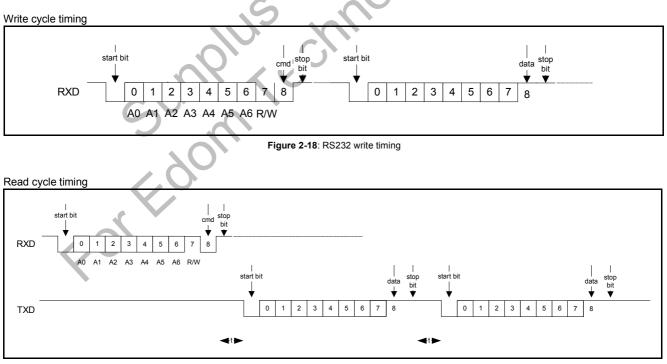

#### 2.1.5. RS232 Interface

The following diagram shows the timing of SPCA554A internal register access via the RS232 serial interface. Nine-bit data transfer protocol is adopted by the SPCA554A. Bit-8 defines whether the transfer is a command transfer or a data transfer. A command transfer defines the access address and the access mode. The access mode can be read access or write access, depending on bit-7 of the transfer. Multiple data bytes can be transferred, following a command. The baud rates are programmable from 1.2 Kb/s to 115.2 Kb/s. The default baud

rate is 9600 bit/sec after power on. The time interval between each read data transfer is also programmable from 0 to 255 bits, which can also be programmed by the SPCA554A internal register.

The following diagrams show the timing. The read transfer command is sent from the host to the SPCA554A. After SPCA554A receives the read command, it transfers data back to the host.

Figure 2-19: RS232 read timing

Note: The symbol "t" represents the time internal between each read data transfer.

#### 2.2. Sensor interface

The sensor interface is used by the SPCA554A to acquire image input. Due to the wide range of data formats supported, the SPCA554A is able to obtain image data from a CMOS sensor, CCD sensor module or a TV decoder. The SPCA554A supports the following data types:

- Bayer pattern raw data: Usually used by CMOS sensors.

- CCIR601 YUV data: Usually used by CMOS sensors, CCD sensor modules and TV decoders.

- CCIR656 YUV data: Usually used by CMOS sensors, CCD sensor modules and TV decoders.

#### 2.2.1. Pin Description

The following table lists sensor interface pin usage in different types of image data inputs:

| Pin Name | Bayer Raw Data Input            |   | CCIR601        |   | CCIR656 | C | IO Buffer |

|----------|---------------------------------|---|----------------|---|---------|---|-----------|

| TGGPI00  | FLASHCTRL                       |   |                | 5 | 0       | 0 | BD        |

| TGGPIO1  | TGGPIO1                         |   | DVALID         | - | TGGPI01 | В | BD        |

| TGGPIO2  | SCL (I2C)                       |   |                |   |         | в | BD        |

| TGGPIO3  | SDA (I2C)                       |   | XO             |   |         | В | BD        |

| TGGPIO4  | HD (horizontal synchronization) | в | HD             |   | TGGPIO4 | В | BD        |

| TGGPIO5  | VD (vertical synchronization)   | В | VD             |   | TGGPIO5 | В | BD        |

| TGGPIO6  | Pixel clock                     |   |                |   |         | В | BD        |

| TGGPI07  | Master clock                    |   |                | 5 |         | В | BD        |

| TGGPIO8  | SEN                             |   |                |   |         | 0 | BD        |

| TGGPIO9  | SCK                             |   |                |   |         | 0 | BD        |

| TGGPIO10 | SD                              |   |                |   |         | 0 | BD        |

| RGB0     | Bayer raw data input, bit 0.    |   | VVALID         | I |         |   | ID        |

| RGB1     | Bayer raw data input, bit 1.    | 1 | HVALID         | I |         |   | ID        |

| RGB2     | Bayer raw data input, bit 2.    | I | YUV data bit 0 |   |         | - | ID        |

| RGB3     | Bayer raw data input, bit 3.    | I | YUV data bit 1 |   |         | - | ID        |

| RGB4     | Bayer raw data input, bit 4.    | I | YUV data bit 2 |   |         | - | ID        |

| RGB5     | Bayer raw data input, bit 5.    | I | YUV data bit 3 |   |         | - | ID        |

| RGB6     | Bayer raw data input, bit 6.    | Ι | YUV data bit 4 |   |         | Ι | ID        |

| RGB7     | Bayer raw data input, bit 7.    | 1 | YUV data bit 5 |   |         | Ι | ID        |

| RGB8     | Bayer raw data input, bit 8.    | Ι | YUV data bit 6 |   |         | Ι | ID        |

| RGB9     | Bayer raw data input, bit 9.    | Ι | YUV data bit 7 |   |         | Ι | ID        |

Table 2-3: Pins description for sensor interface

The typical function of TGGPIO0 is flash light strobe control. It can be used as a GPIO pin if the target system does not implement the flash light function. TGGPIO2 and TGGPIO3 constitute a I2C master. The control is used to program the registers in the CMOS sensor, the registers in the CCD module, or the registers in a TV decoder. TGGPIO8, TGGPIO9, and TGGPIO10 can operate in the three-wire mode. The three-wire control bus is normally used in a CCD module.

TGGPIO4 is a horizontal synchronization signal, which indicates the start of an image line. TGGPIO5 is the vertical synchronization signal, which indicates the start of a new image frame. Both GPIO4 and GPIO5 can be controlled by the SPCA554A or by the sensor, meaning that the SPCA554A CMOS sensor interface can be operated in the master mode or the slave mode.

TGGPIO6 is the pixel clock, which is usually driven by the sensor. The SPCA554A uses the pixel clock to sample input image data. TGGPIO7 is the master clock supplied to the sensor by the SPCA554A. The master clock serves as the clock input to the CMOS sensor. The frequency of the master clock is normally multiples of the pixel-clock frequency. The SPCA554A sets the master-clock frequency according to sensor specifications by default. However, in extremely low-light condition, the SPCA554A might reduce the frequency of the master clock to get longer exposure time.

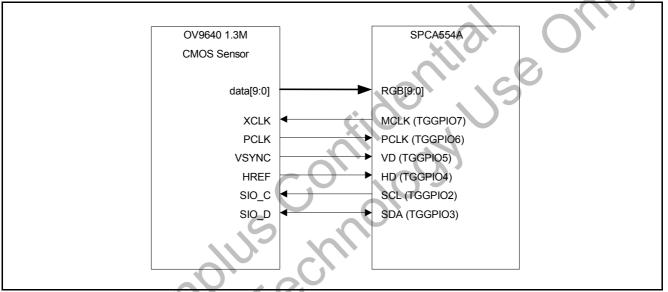

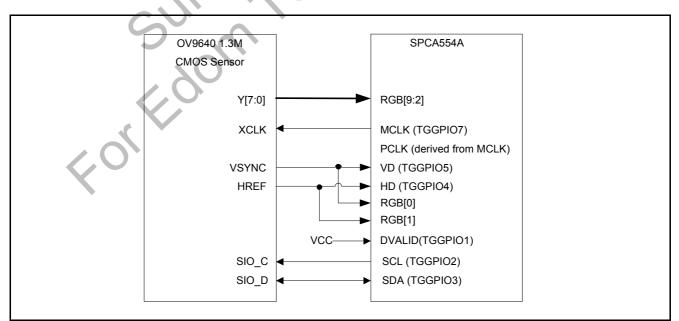

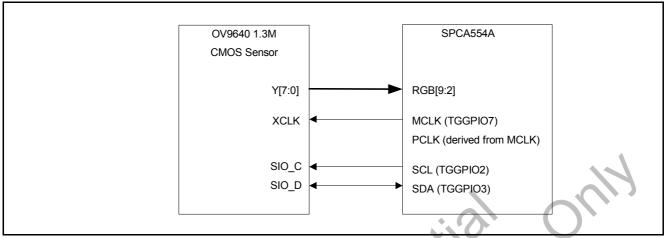

The SPCA554 supports 10-bit raw data input. The data bus is also used to input YUV data in CCIR601 and CCIR656 standards. The CCIR601 601 standard defines both the 8-bit and 16-bit data bus, however the SPCA554A only supports the 8-bit mode. The following figures are interconnection examples between the SPCA554A and Omnivison OV9640 CMOS sensors. OV9640 can output Bayer pattern raw data, CCIR656 YUV data, and CCIR601 YUV data.

Figure 2-20: Interface connection between the SPCA554A and the OV9640 CMOS sensor; raw data

Figure 2-21: Interface connection between the SPCA554A and the OV9640 CMOS sensor; CCIR601 YUV data

Figure 2-22: Interface connection between SPCA554A and OV9640 CMOS sensor; CCIR656 YUV data

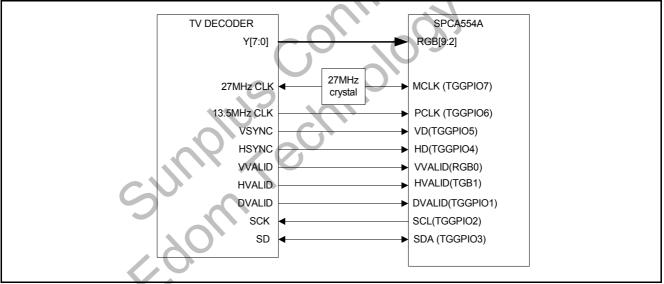

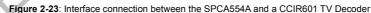

Figure 2-23 and Figure 2-24 shows the interconnection between the SPCA554A and a TV decoder using a digital TV standard interface. A 27MHz external clock source is required in TV-input applications.

Figure 2-24: Interface connection between the SPCA554A and a CCIR656 TV Decoder

#### 2.2.2 I2C master port

The SPCA554A has an internal I2C master controller; TGGPIO[3:2]. Eight bytes of internal buffer are integrated with the I2C master controller, so that up to 8-bytes of burst access to the CMOS sensor can be done by the I2C master controller. The fast mode data transfer of I2C specifications is also supported, which provides up to a 400K bits/sec date rate. According to I2C standards, there are a lot of variations in terms of timing. The SPCA554A supports the following timings (just which timing is appropriate depends on the requirement of the CMOS sensor):

- Normal-write timing

- Burst-write timing

- Normal-read timing

- Read-without-stop-code timing

- Read-without sub-address timing

The slave address in I2C specifications indicates which I2C device is to be accessed. The slave address of the CMOS sensor can

be found in CMOS sensor specifications. The SPCA554A supports a programmable I2C slave address. The sub-address indicates which internal register of the CMOS sensor is to be accessed. For example, the CMOS sensor gain register and the exposure register have different sub-addresses in the CMOS sensor.

Normal-write timing

The sub address is transmitted only once, where multiple bytes of data are written into the same CMOS sensor register.

Slave address: The I2C device address, i.e. the CMOS sensor I2C address.

W: 0 for write operation, 1 for read operation

ACKs: Acknowledge from CMOS sensor, 0 for acknowledge, 1 for non-acknowledge

ACKm: Acknowledge from the SPCA554A, 0 for acknowledge, 1 for non-acknowledge

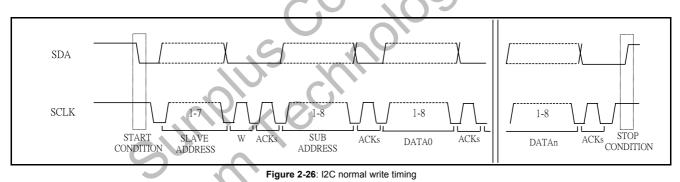

Burst-write timing:

Figure 2-27: I2C burst-write timing

#### The normal data read protocol:

Figure 2-29: I2C data read without stop code timing

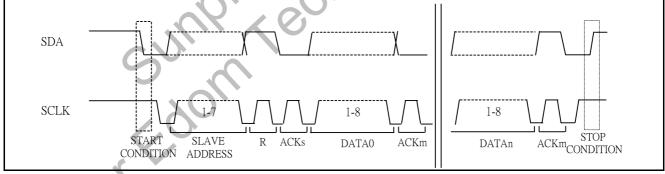

#### Data-Read without Sub-Address Protocol:

Some CMOS sensors allow the omission of sub-address transmission if the sub-address is the same as the previous I2C transfer.

Figure 2-30: I2C data read without sub-address timing

#### 2.2.3 Three-wired master serial port

CCD modules use a proprietary control bus for internal register programming. The SPCA554A supports a three-wire control bus with four different timing options. Using the three-wire control bus, the SPCA554A can transmit up to 64 bits of data to the CCD module, however, there is no read-back path. The bit clock frequency is programmable. The SPCA554A transmits low byte first and LSB (Least Significant Bit) first (Refer to the diagram below). Bit 0 of DATA0 is the first bit to be sent to the sensors. Figure 2-31 shows the data transfer sequence.

Figure 2-31: Three-wired control bus data transfer sequence

The SPCA554A supports 4 types of three-wire protocols as described below:

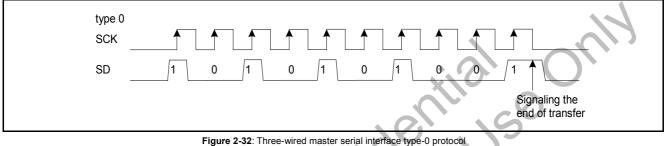

#### *Type-0 protocol :* (use only two signals)

In type-0 protocol, the SEN signal is not used. The serial data is latched at the rising edge of SCK by the CMOS sensor. The SD signal stays high at the last falling edge of SCK. The SPCA554A drives DS high at the falling edge of the last falling edge of SCK to signal the end of serial transfer. The example below illustrates a 10-bit data transfer. Note that the data is 10\_01010101b (LSB-first).

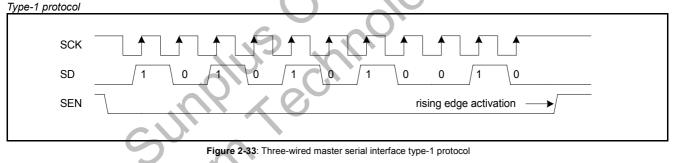

In Type-1 protocol, the data is latched at the rising edge of SCK. SEN is driven low at the start of entire data transfer cycle and a rising edge of SEN indicates the end of transfer. Figure 2-33 shows an example of an 11-bit data transfer, with data 010\_01010101b, using type-1 protocol.

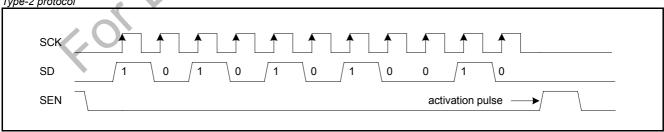

Figure 2-34: Three-wired master serial interface type-2 protocol

Type-2 protocol is similar to type-1 protocol, except for SEN signal behavior. A positive pulse on the SEN signal is used to indicate the end of data transfer in type-2 protocol. Figure 2-34 shows an 11-bit data transfer using type-2 protocol. The data is 010\_01010101b. *Type-3 protocol*

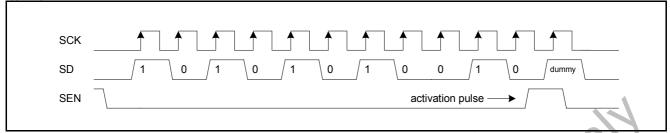

Figure 2-35: Three-wire master serial interface type 3 timing

Type-3 protocol is similar to type-2 protocol except that one dummy bit is attached at the end of the data transfer. Figure 2-35 shows an 11-bit data transfer using type-3 protocol. The data is 010\_010101b.

#### 2.2.4 Data transfer timing

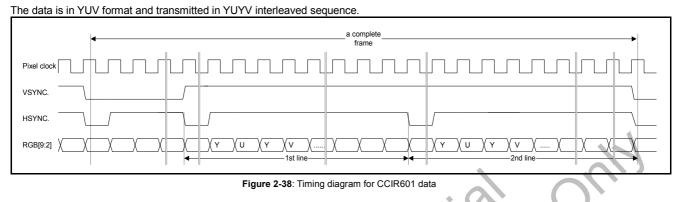

This sub-section describes the timings in raw data transfer, CCIR601 data transfer and CCIR656 data transfer.

#### Raw Data Transfer Timing

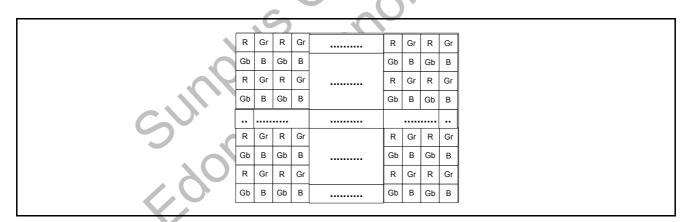

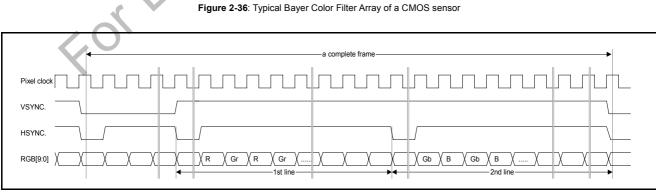

The SPCA554A requires HSYNC and VSYNC signals to construct the entire timing of an image frame. These signals can be generated by the SPCA554A internal counter or fed back from the sensors. Figure 2-36 illustrates the color filter array in a typical CMOS sensor.

Figure 2-37: Timing diagram for bayer pattern data

#### CCIR601 Data Transfer Timing

#### CCIR656 Data Transfer Timing

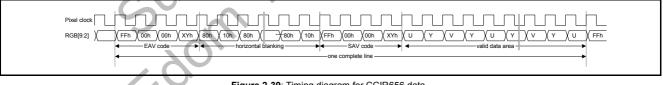

Synchronization signals are encoded and inserted into the video YUV data. The encoded synchronization signal (the marker) starts with an EAV code (FFh, 00h, 00h, XYh) and stops with an SAV code (FFh, 00h, 00h, XYh). The SPCA554A decodes the markers and generates internal synchronization signals to construct video frame timing. The fourth byte of the marker has the HSYNC, VSYNC, field, sriod. blanking information, and so on as described below:

| Bit 7 | fixed at 1. |

|-------|-------------|

|       | inted at 1. |

| Bit 6 | F   | , 0 : FIELD 0, 1: FIELD 1.                       |

|-------|-----|--------------------------------------------------|

| Bit 5 |     | V, 0: non-blanking period, 1: blanking period    |

| Bit 4 | Н,  | 0: start of active video, 1: end of active video |

| Bit 3 | P3, | V xor H                                          |

| Bit 2 | P2, | F xor H                                          |

| Bit 1 | P1, | F xor V                                          |

| Bit 0 | P0, | F xor V xor H                                    |

|       |     |                                                  |

Figure 2-39: Timing diagram for CCIR656 data

SAV: Start position of horizontal valid data.

EAV: End position of horizontal valid data.

The YUV data sequence is programmable inside SPCA554A, allowing the SPCA554A to adapt to different input sources.

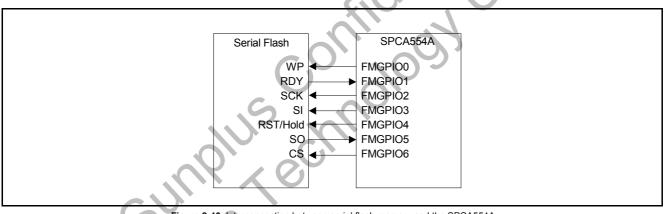

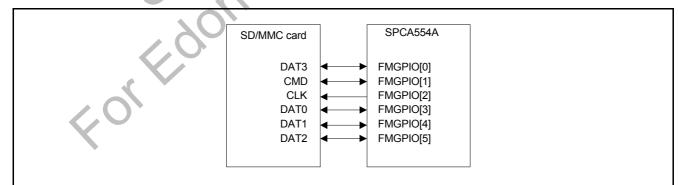

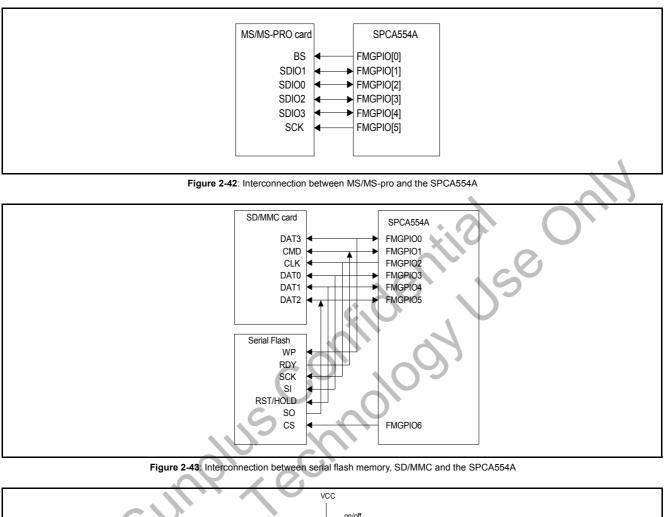

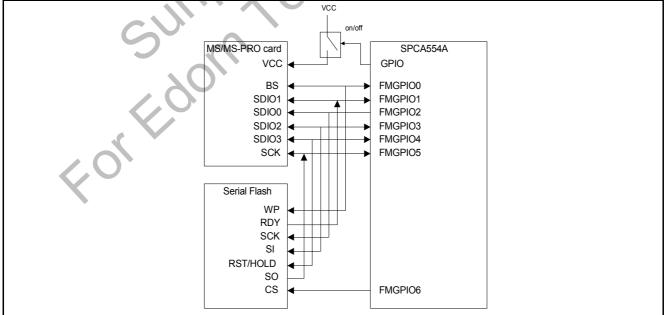

#### 2.3. Storage Interface

The storage media interface is used by the SPCA554A to access external storage media. The SPCA554A always acts as a master to these storage medias. It is not possible for another bus master to control the SPCA554A through the storage media interface. The SPCA554A supports three types of storage media;

- SPI-type serial flash: Supports mode0, mode1, mode2 and mode3.

- Security Digital card: Both 1-bit and 4-bit modes. As MMC can be accessed by the 1-bit SD mode, SPCA554A also supports MMC.

- Memory Stick Card: Supports 1-bit mode for Memory Stick cards and 4-bit mode for Memory Stick Pro cards.

| Table 2-4 lists pin functions according to dimerent storage media types. |                         |           |              |   |                      |                       |      |

|--------------------------------------------------------------------------|-------------------------|-----------|--------------|---|----------------------|-----------------------|------|

| Pin Name                                                                 | SD Card / MMC           |           | Memory Stick |   | SPI-Type Serial Flas | SPI-Type Serial Flash |      |

| FMGPIO0                                                                  | DAT3                    | В         | BS           | 0 | WP/                  | 0                     | BD   |

| FMGPIO1                                                                  | CMD                     | В         | SDIO1        | В | RDY                  | Ι                     | BD   |

| FMGPIO2                                                                  | CLK                     | 0         | SDIO0        | В | SCK                  | 0                     | BD   |

| FMGPIO3                                                                  | DAT0                    | В         | SDIO2        | В | SI                   | 0                     | BD   |

| FMGPIO4                                                                  | DAT1                    | В         | SDIO3        | В | RST/                 | 0                     | BD   |

| FMGPIO5                                                                  | DAT2                    | В         | SCK          | 0 | SO                   | I                     | BD 💊 |

| FMGPIO6                                                                  | FMGPIO6                 | В         | FMGPIO6      | В | CS/                  | 0                     | BD   |

| Table 2-4. Pins de                                                       | escriptions for storage | interface |              |   |                      |                       |      |

Table 2-4 lists nin functions according to different storage media types

Table 2-4: Pins descriptions for storage interface.

Most storage media interface pins are multi-functional pins, except for the CS/ (chip select) pin for serial flash memory. The SPCA554A has a dedicated pin for CS/ of serial flash memory, allowing serial flash memory to co-exist with an SD card or an MS

card. An SD card cannot co-exist with an MS card in an SPCA554A application. Five feasible interconnections with external storage media are shown in the following figures:

Figure 2-40: Interconnection between serial flash memory and the SPCA554A

Figure 2-41: Interconnection between SD/MMC and the SPCA554A

## SPCA554A

Figure 2-44: Interconnection between serial flash memory, MS/MS-pro and the SPCA554A

Note: To avoid bus conflict, MS power supply must be cut off before accessing serial flash memory. The power switch control can use any SPCA554A GPIO pin.

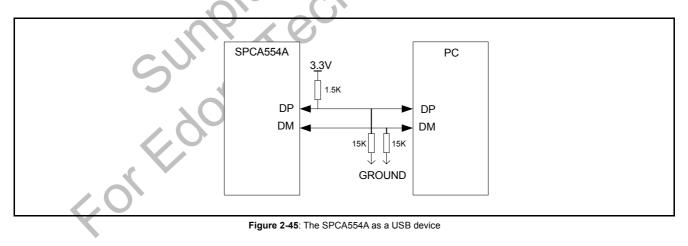

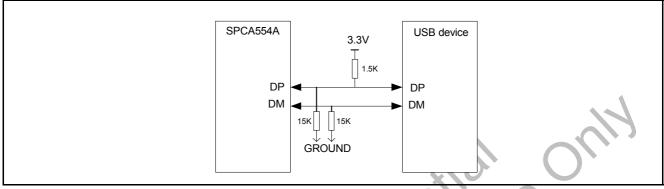

#### 2.4. USB interface

The USB interface enables the SPCA554A to communicate with PCs. Data can be uploaded to PCs or downloaded from PCs via the USB bus. The ISP (In-System-Programming) function can also take advantage of the USB bus, which allows new firmware codes to be downloaded to the SPCA554A and then programmed to external serial flash memory. Another benefit of the USB interface is allowing the SPCA554A to be used as a PC-camera. The sensor module calibration in the mass production stage can

also be done via a PC host.

By setting SPCA554A internal registers, the built-in USB controller can easily be configured to three different modes; USB function mode, USB host mode and OTG mode. The USB host mode and the USB function mode share an on-chip USB 1.1 full speed transceiver, while the USB OTG mode requires an external OTG transceiver. With the external OTG transceiver, the SPCA554A turns into a USB OTG dual-role device.

| Pin Name | USB Device |   | USB Device USB Host |   | USB OTG        |   | IO Buffer       |  |

|----------|------------|---|---------------------|---|----------------|---|-----------------|--|

| DP       | DATA D+    | В | DATA D+             | В | Not used       | - | USB transceiver |  |

| DM       | DATA D-    | В | DATA D-             | В | Not used       | - | USB transceiver |  |

| OTGGPI00 | OTGGPI00   | В | OTGGPI00            | В | OTG interrupt  |   | BD              |  |

| OTGGPI01 | OTGGPI01   | В | OTGGPIO1            | В | OTG data input | 7 | BD              |  |

| OTGGPIO2 | OTGGPIO2   | В | OTGGPIO2            | В | OTG DATA D+    | В | BD              |  |

| OTGGPIO3 | OTGGPIO3   | В | OTGGPIO3            | В | OTG DATA D-    | В | BD              |  |

| OTGGPIO4 | OTGGPIO4   | В | OTGGPIO4            | В | OTG DATA OE    | 0 | BD              |  |

Table 2-5: Pin descriptions for storage interface

Three feasible USB applications of the SPCA554A are illustrated below. SPCA554A as a USB device:

A 1.5K Ohm pull high resistor must be connected to DP pin to the SPCA554A as a USB full speed device.

#### SPCA554A as an USB host:

As a USB host, both DP and DM signals must be pulled-low by 15K Ohm resistors.

Figure 2-46: The SPCA554A as an USB host

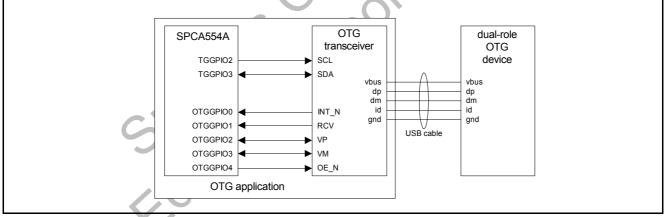

The SPCA554 as an OTG dual-role device:

An external OTG transceiver should be connected to the OTGGPIO bus to enable the SPCA554A to communicate with other OTG dual-role devices. The OTG transceiver is controlled by an  $I^2C$  bus. This  $I^2C$  bus can be shared with the  $1^2C$  bus

described in the sensor interface section because the  $I^2C$  standard allows multiple  $I^2C$  devices to be connected serially. The SPCA554A is able to grate different  $I^2C$  slave addresses for each  $I^2C$  devices.

Figure 2-47: The SPCA554A as a USB OTG device

#### 2.5. Audio Interface

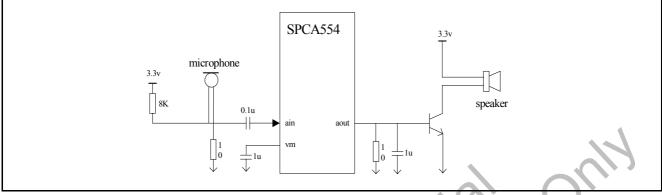

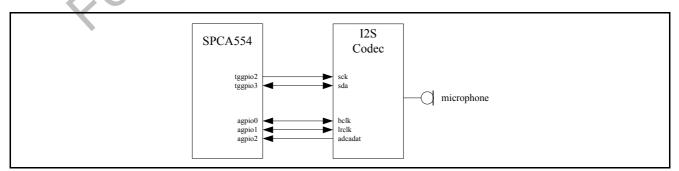

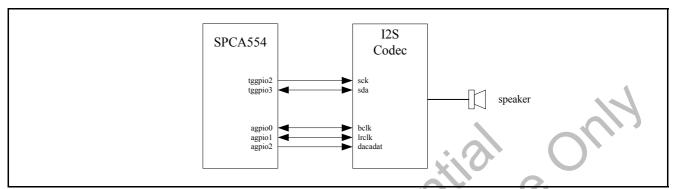

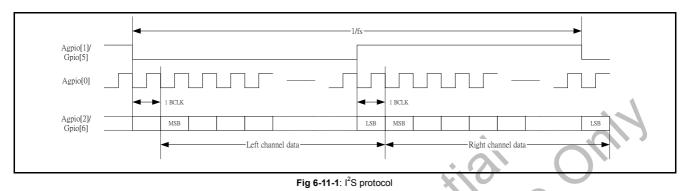

The SPCA554A has both an analog and a digital audio interface. The analog interface is connected to an on-chip audio ADC and DAC. The digital audio interface is a  $I^2S$  bus used to exchange data with external audio CODEC. The configuration of the audio interface is summarized below:

- Analog audio:

- I<sup>2</sup>S digital audio interface for audio record:

- I<sup>2</sup>S digital audio interface for audio playback:

On-chip 12-bit audio ADC and DAC.

The SPCA554A can be an  $\mathsf{I}^2\mathsf{S}$  mater or an  $\mathsf{I}^2\mathsf{S}$  slave.

- back: The SPCA554A can be an  $I^2S$  mater or an  $I^2S$  slave.

- I<sup>2</sup>S digital audio interface for audio record and playback: The SPCA554A is an I<sup>2</sup>S slave.

Figure 2-48 illustrates an analog audio application.

Figure 2-48: The reference circuit of the built-in ADC and DAC.

I<sup>2</sup>S-related pins and feasible modes are listed in Table 2-6 below:

| Pin Name | Audio Record Only | / | Audio Playback Only |   | Audio Record And Playback |   | IO Buffer |

|----------|-------------------|---|---------------------|---|---------------------------|---|-----------|

| AGPIO0   | I2S_BCLK          | В | I2S_BCLK            | в | I2S_BCLK                  | Ι | BD        |

| AGPIO1   | I2S_LRC           | В | I2S_LRC             | в | I2S_LRC                   | Ι | BD        |

| AGPIO2   | I2S_DI            | Ι | I2S_DO              | 0 | 12S_DO                    | 0 | BD        |

| GPIO5    | GPIO5             | В | GPIO5               | в | ADCLRC                    | Ι | BD        |

| GPIO6    | GPIO6             | В | GPIO6               | в | I2S_DI                    | I | BD        |

Table 2-6: Pin descriptions for audio input (I<sup>2</sup>S)

In uni-directional audio applications, either in the record-only or in the playback-only mode, the SPCA554A can act as an I<sup>2</sup>S slave or an I<sup>2</sup>S master. If the SPCA554A is used as an I<sup>2</sup>S master, both I2S\_BCLK and I2S\_LRC are driven by the SPCA554A. On the other hand, if the SPCA554A is used as an I<sup>2</sup>S slave, both signals are driven by external audio CODEC. Also, in uni-directional applications, GPIO5 and GPIO6 are not used for the audio function.

$\rm I^2S$  bi-directional applications require two extra pins; GPIO5 and GPIO6. With these two extra pins, the SPCA554A can record

and playback audio at the same time. In this type of application, the SPCA554A can only be an I<sup>2</sup>S slave. AGPIO2 is used to send audio data to the external audio CODEC. And GPIO6 is used to receive audio data from external audio CODEC.

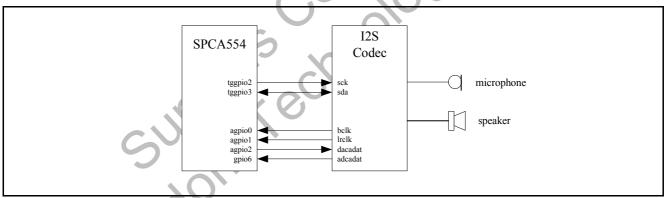

#### I2S Audio Record-Only

The following diagram shows the connection between the SPCA554A and an external  $I^2S$  audio CODEC in a record-only application. The SPCA554A uses its  $I^2C$  master port to control external audio CODEC. Audio data is sent from the external  $I^2S$  CODEC to the SPCA554A.

Figure 2-49: The connection between the SPCA554A and an external ADC in a record-only application

#### I2S Audio Playback-Only

The following diagram shows the connection between the SPCA554A and an external  $I^2S$  audio CODEC in a playback-only

application. Like in the record-only configuration, the SPCA554A controls the I<sup>2</sup>S via its master I<sup>2</sup>C port. Audio data is sent from the SPCA554A to the I<sup>2</sup>S CODEC.

Figure 2-50: The connection between the SPCA554A and an external ADC in a playback-only application

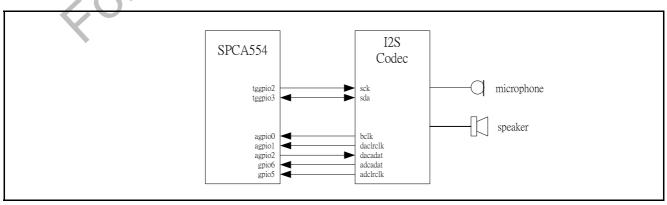

I2S as Audio Record and Playback at the Same Time The following diagram shows the connection between the SPCA554A and an external  $I^2S$  CODEC in a bi-directional application. In this application, audio record and playback are done at the same time. This example assumes that record and playback are operated at the same sample rate, which is controlled by LRCK. Both LRCK and BCLK signals are driven by external CODEC.

Figure 2-51: Interface connection for record and playback at the same time (same sample rate)

If audio record and playback are operated at different sample rates, then record sample rate is controlled by GPIO5 and

playback sample rate is controlled by AGPIO1. See the following illustration:

© Sunplus Technology Co., Ltd. Proprietary & Confidential

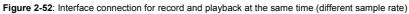

#### 2.6. Display interface

The SPCA554A supports a variety of LCM interface types as described below:

- 18-bit RGB interface RGB666

- 18-bit memory RGB666

- 16-bit memory protocol RGB666, RGB565, RGB444

- 9-bit memory interface RGB666

- 8-bit memory RGB666, RGB565, RGB444, RGB332

- YUV output

Besides the color depths described above, the SPCA554A supports a very flexible RGB data sequence. All possible feasible sequences are described in this section. The following table lists pin functions according to the interface type. Note that unused pins in a specific type of LCM interface are assigned as GPIO pins.

c type of LCM interface are assigned as GPIO pins.

| <b></b> |   |            |        |        |        |        |            |           |

|---------|---|------------|--------|--------|--------|--------|------------|-----------|

|         |   | 18-bit RGB | 18-bit | 16-bit | 9-bit  | 8-bit  | YUV Output | IO Buffer |

|         |   |            | Memory | Memory | Memory | Memory |            |           |

| LGPIO0  | 0 |            | XCS    | XCS    | XCS    | XCS    | 0          | BD        |

| LGPIO1  | 0 |            | XRD    | XRD    | XRD    | XRD    | , O        | BD        |

| LGPIO2  | 0 |            | XWR    | XWR    | XWR    | XWR    | 2          | BD        |

| LGPIO3  | В |            | A0     | A0     | A0     | A0     |            | BD        |

| LGPIO4  | В | R0         | D0     | D0     | D0     | D0     | YUV0       | BD        |

| LGPIO5  | В | R1         | D1     | D1     | D1     | D1     | YUV1       | BD        |

| LGPIO6  | В | R2         | D2     | D2     | D2     | D2     | YUV2       | BD        |

| LGPI07  | В | R3         | D3     | D3     | D3     | D3     | YUV3       | BD        |

| LGPIO8  | В | R4         | D4     | D4     | D4     | D4     | YUV4       | BD        |

| LGPIO9  | В | R5         | D5     | D5     | D5     | D5     | YUV5       | BD        |

| LGPIO10 | В | G0         | D6     | D6     | D6     | D6     | YUV6       | BD        |

| LGPIO11 | В | G1         | D7     | D7     | D7     | D7     | YUV7       | BD        |

| LGPIO12 | В | G2         | D8     | D8     | D8     |        | YUV8       | BD        |

| LGPIO13 | В | G3         | D9     | D9     |        |        | YUV9       | BD        |

| LGPIO14 | В | G4         | D10    | D10    |        |        | YUV10      | BD        |

| LGPIO15 | В | G5         | D11    | D11    |        |        | YUV11      | BD        |

| LGPIO16 | В | В0         | D12    | D12    |        |        | YUV12      | BD        |

| LGPIO17 | В | B1         | D13    | D13    |        |        | YUV13      | BD        |

| LGPIO18 | В | B2         | D14    | D14    |        |        | YUV14      | BD        |

| LGPIO19 | в | В3         | D15    | D15    |        |        | YUV15      | BD        |

| LGPIO20 | 0 | B4         | D16    |        |        |        |            | BD        |

| LGPIO21 | 0 | B5         | D17    |        |        |        |            | BD        |

| LGPIO22 | О | MCK        |        |        |        |        | YUVCK      | BD        |

| LGPIO23 | 0 | HS         |        |        |        |        | HREF       | BD        |

| LGPIO24 | 0 | VS         |        |        |        |        | VREF       | BD        |

| LGPIO25 | 0 | DE         | XCS2   | XCS2   | XCS2   | XCS2   |            | BD        |

Table 2-7: Pin descriptions for LCM interface

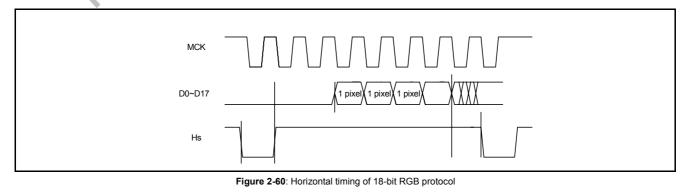

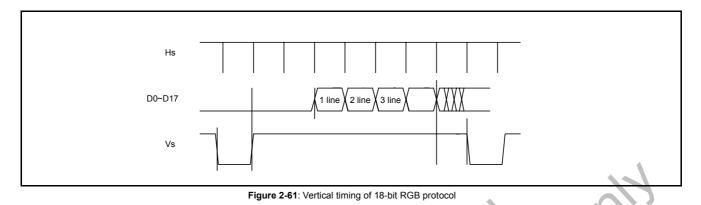

The 18-bit RGB protocol uses vertical and horizontal synchronization signals (VS and HS) to construct timing of a display frame. 18-bit RGB data is sent to the LCM per clock.

the LCM panel in the same way as a standard SRAM interface. The SPCA554A supports dual-panel applications. LCMGPIO0 is used as the chip select signal of the main LCM panel and LCMGPIO25] is used as the chip select signal of the sub-LCM panel.

All memory protocols have READ/WRITE pulses, which access

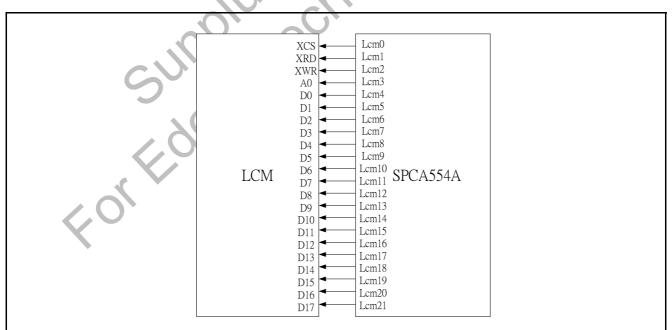

Figure 2-54: 18-bit memory interface connection

## Preliminary

# SPCA554A

Figure 2-57: 8-bit memory interface connection

Preliminary

## SPCA554A

#### 2.6.1. 18-bit RGB interface

The 18-bit RGB interface transfers data by parallel data bus D0~D17 (R0 ~ R5, G0 ~ G5, B0 ~ B5), VS, HS, and MCK. The

data sequence of D0~D17 is programmable. Waveform and data sequence are shown in the following figures:

| Color Format         | Data Sequence Option   |

|----------------------|------------------------|

| 18 bit RGB interface | {B[5:0],G[5:0],R[5:0]} |

|                      | {R[5:0],G[5:0],B[5:0]} |

Table 2-8: Data sequence of the 18 bit RGB interface

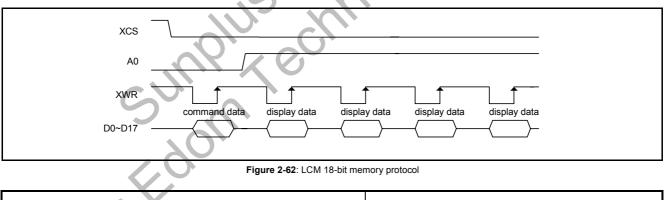

#### 2.6.2. 18-bit Memory interface

RGB data is carried by data bus D[17:0]. The A0 pin allows the SPCA554A to change the address of the register to be accessed. Typical LCMs with memory protocol allow the SPCA554A to program internal registers for initialization. In addition, there is

address mapping to the LCM data port, allowing the SPCA554A to access frame buffer inside the LCM. Waveform and data sequence are shown as follows:

Note: The SPCA554 can also read LCM data by internal CPU.

| Color Format   | Data Sequence Option   |

|----------------|------------------------|

| 18 bit RGB 666 | {B[5:0],G[5:0],R[5:0]} |

|                | {R[5:0],G[5:0],B[5:0]} |

Table 2-9: Data sequence of the 18 bit RGB 666 format

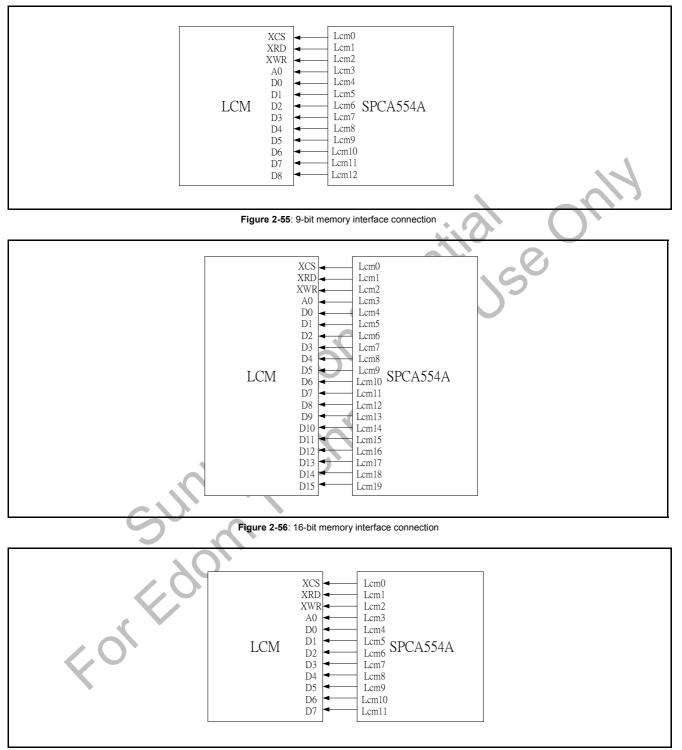

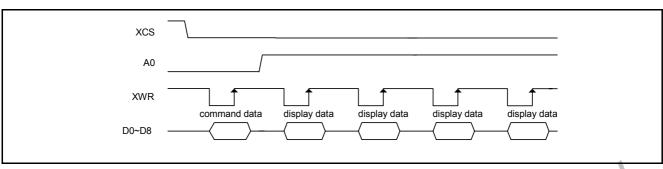

#### 2.6.3. 9-bit Memory interface

The 9-bit memory interface transfers data by parallel data bus (D0 ~ D8), XCS, A0, XWR, and XRD. Waveform and data sequence are shown as follows:

SPCA554A

| Color Format  | Data Sequence Option |

|---------------|----------------------|

| 9 bit RGB 666 | {G[2:0],R[5:0]}      |

|               | {B[5:0],G[5:3]}      |

|               | {R[5:0],G[2:0]}      |

|               | {G[5:3],B[5:0]}      |

|               |                      |

Table 2-10: Data sequence of 9 bit RGB 666 format

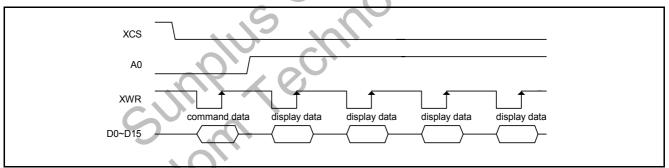

#### 2.6.4. 16-bit Memory interface

The 16-bit memory interface transfers data by parallel data bus (D0 ~ D15), XCS, A0, XWR, and XRD. Waveform and Data sequence is shown as follows:

Figure 2-64: LCM 16-bit memory protocol

| Color Format      | Data Sequence Option              |  |

|-------------------|-----------------------------------|--|

| 16 bit RGB 666 NR | {B1[3:0],G1[5:0],R1[5:0]}         |  |

|                   | {B2[1:0],G2[5:0],R2[5:0],B1[5:4]} |  |

|                   | {G3[5:0],R3[5:0],B2[5:2]}         |  |

|                   | {G4[3:0],R4[5:0],B3[5:0]}         |  |

|                   | {G5[1:0],R5[5:0],B4[5:0],G4[5:4]} |  |

|                   | {R6[5:0],B5[5:0],G5[5:2]}         |  |

|                   | {R7[3:0],B6[5:0],G6[5:0]}         |  |

|                   | {R8[1:0],B7[5:0],G7[5:0],R7[5:4]} |  |

|                   | {B8[5:0],G8[5:0],R8[5:2]}         |  |

Preliminary

## SPCA554A

| Color Format   | Data Sequence Option              |

|----------------|-----------------------------------|

|                | {R1[5:0],G1[5:0],B1[3:0]}         |

|                | {B1[5:4],R2[5:0],G2[5:0],B2[1:0]} |

|                | {B2[5:2],R3[5:0],G3[5:0]}         |

|                | {B3[5:0],R4[5:0],G4[3:0]}         |

|                | {G4[5:4],B4[5:0],R5[5:0],G5[1:0]} |

|                | {G5[5:2],B5[5:0],R6[5:0]}         |

|                | {G6[5:0],B6[5:0],R7[3:0]}         |

|                | {R7[5:4],G7[5:0],B7[5:0],R8[1:0]} |

|                | {R8[5:2],G8[5:0],B8[5:0]}         |

| 16 bit RGB 565 | {B[4:0],G[5:0],R[4:0]}            |

|                | {R[4:0],G[5:0],B[4:0]}            |

| 16 bit RGB 444 | {4'b0,B[3:0],G[3:0],R[3:0]}       |

|                | { B[3:0],G[3:0],R[3:0],4'b0}      |

|                | {4'b0,R[3:0],G[3:0],B[3:0]}       |

|                | { R[3:0],G[3:0],B[3:0],4'b0}      |

| 16 bit RGB 666 | {4'b0,G1[5:0],R1[5:0]}            |

|                | {4'b0,R2[5:0], B1[5:0]}           |

|                | {4'b0, B2[5:0], G2[5:0]}          |

|                | {2'b0,G1[5:0], 2'b0,R1[5:0]}      |

|                | {2'b0,R2[5:0], 2'b0, B1[5:0]}     |

|                | {2'b0, B2[5:0], 2'b0, G2[5:0]}    |

|                | {G1[5:0],R1[5:0], 4'b0}           |

|                | {R2[5:0], B1[5:0], 4'b0}          |

|                | {B2[5:0], G2[5:0], 4'b0}          |

|                | {G1[5:0], 2'b0,R1[5:0], 2'b0}     |

|                | {R2[5:0], 2'b0, B1[5:0], 2'b0}    |

|                | {B2[5:0], 2'b0, G2[5:0], 2'b0}    |

|                | {4'b0,R1[5:0],G1[5:0]}            |

|                | {4'b0,B1[5:0], R2[5:0]}           |

| FORES          | {4'b0, G2[5:0], B2[5:0]}          |

|                | {2'b0,R1[5:0], 2'b0,G1[5:0]}      |

|                | {2'b0,B1[5:0], 2'b0, R2[5:0]}     |

| 2.0            | {2'b0, G2[5:0], 2'b0, B2[5:0]}    |

| X              | {R1[5:0],G1[5:0], 4'b0}           |

| •              | {B1[5:0],R2[5:0], 4'b0}           |

|                | { G2[5:0], B2[5:0], 4'b0}         |

|                | {R1[5:0], 2'b0,G1[5:0], 2'b0}     |

|                | {B1[5:0], 2'b0, R2[5:0], 2'b0}    |

|                | {G2[5:0], 2'b0,B2[5:0], 2'b0}     |

Table 2-11: Data sequence of 16 bit RGB format

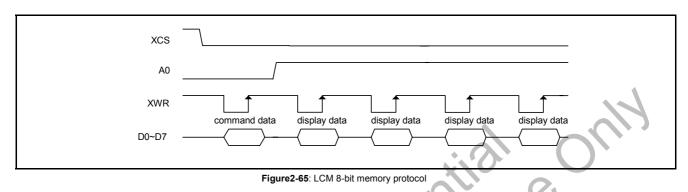

#### 2.6.5. 8-bit Memory interface

The 8-bit memory interface transfers data by parallel data bus (D0 ~ D7), XCS, A0, XWR, and XRD. The waveform and data sequence is shown as follows:

| Color Format     | Data Sequence Option   |

|------------------|------------------------|

| 8 bit RGB 666 NR | {G1[1:0],R1[5:0]}      |

|                  | {B1[3:0],G1[5:2]}      |

|                  | {R2[5:0],B1[5:4]}      |

|                  | {B2[1:0],G2[5:0]}      |

|                  | {R3[3:0],B2[5:2]}      |

|                  | {G3[5:0],R3[5:4]}      |

|                  | {R4[1:0],B3[5:0]}      |

|                  | {G4[3:0],R4[5:2]}      |

|                  | {B4[5:0],G4[5:4]}      |

|                  | {R1[5:0],G1[1:0]}      |

|                  | {G1[5:2],B1[3:0]}      |

|                  | { B1[5:4], R2[5:0]}    |

| 5                | { G2[5:0], B2[1:0]}    |

|                  | { B2[5:2], R3[3:0]}    |

| 20               | { R3[5:4], G3[5:0]}    |

|                  | { B3[5:0], R4[1:0]}    |

|                  | { R4[5:2], G4[3:0]}    |

|                  | { G4[5:4], B4[5:0]}    |

| 8 bit RGB 332    | {B[1:0],G[2:0],R[2:0]} |

|                  | {R[2:0],G[2:0],B[1:0]} |

| 8 bit RGB 444    | {G1[3:0],R1[3:0]}      |

|                  | {R2[3:0],B1[3:0]}      |

|                  | {B2[3:0],G2[3:0]}      |

|                  | {R1[3:0],G1[3:0]}      |

|                  | {B1[3:0],R2[3:0]}      |

|                  | {G2[3:0],B2[3:0]}      |

| 8 bit RGB 565    | {G1[2:0],R1[4:0]}      |

|                  | {B1[4:0],G1[5:3]}      |

|                  | {R1[4:0],G1[5:3]}      |

|                  | {G1[2:0],B1[4:0]}      |

| Color Format  | Data Sequence Option |

|---------------|----------------------|

| 8 bit RGB 666 | {2'b0,R[5:0]}        |

|               | {2'b0,G[5:0]}        |

|               | {2'b0,B[5:0]}        |

|               | {R[5:0], 2'b0}       |

|               | {G[5:0], 2'b0}       |

|               | {B[5:0], 2'b0}       |

Table 2-12: Data sequence of 8 bit RGB format

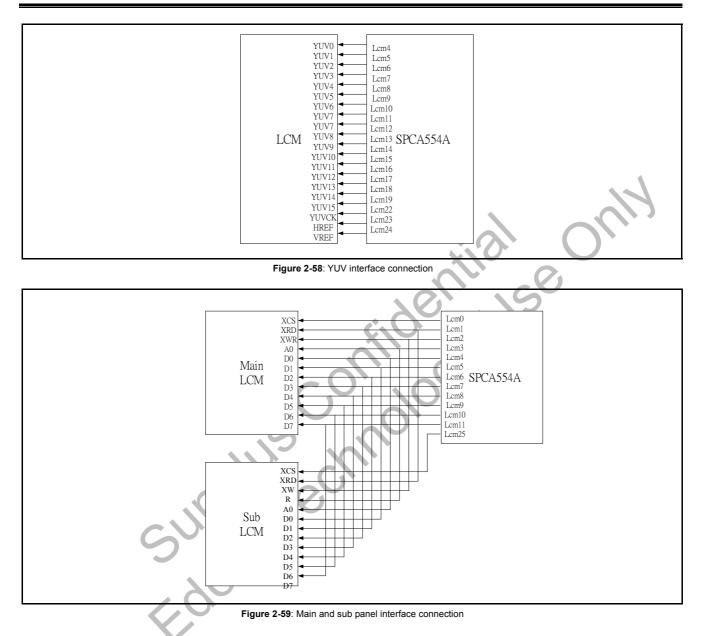

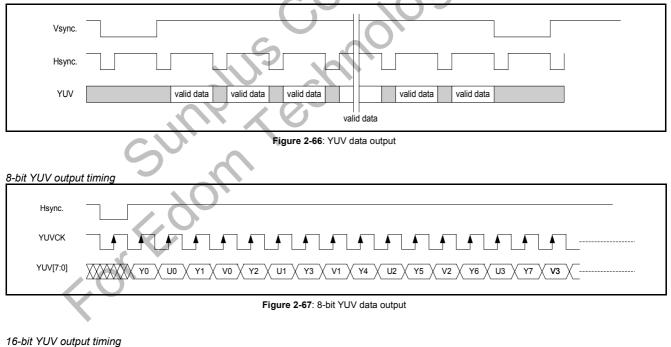

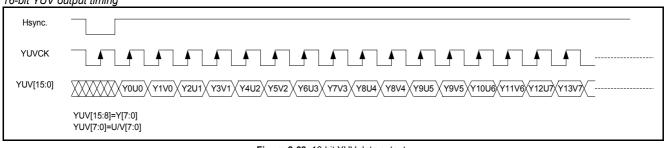

#### 2.6.6. YUV data output

The SPCA554A supports continuous YUV image data output. In this mode, the SPCA554A outputs data with its accompanying clock, vertical reference signal and horizontal reference signal. Data should be sampled at the rising edge of clock. The data bus width can be 8-bits wide or 16-bits wide. The clock frequency is automatically adjusted by the SPCA554A according to the frame rate of the sensor. The maximum frequency is 24MHz. The YUV data output waveform is shown below. The

valid data is sampled when both horizontal and vertical reference signals are high, and horizontal and vertical reference signals may be longer than one clock cycle but they always change their state at the falling edge of clock. YUV output is not normally used to interface with an LCM panel even though it shares LCM interface pins. This YUV output function is used to convert Bayer pattern raw data into YUV data, taking advantages of the SPCA554A internal image enhancement function.

Figure 2-68: 16-bit YUV data output

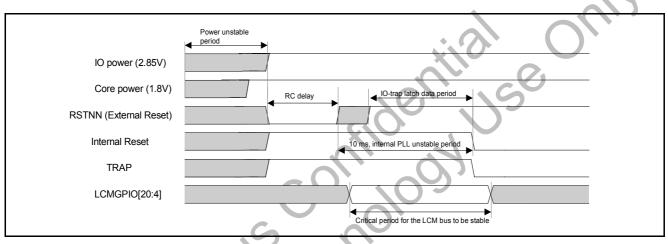

## **3.RESET AND IO-TRAP**

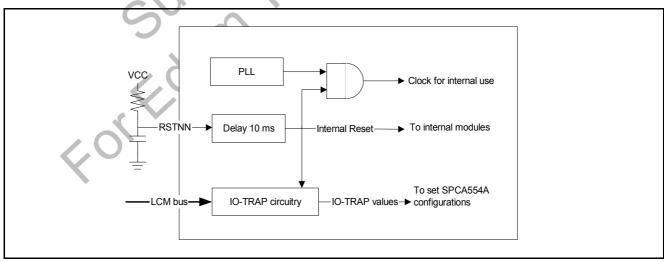

Power-on reset of the SPCA554 can be designed by a simple RC-delay circuit. The SPCA554 reset pin connects to an internal Schmitt-Triggered buffer. The SPCA554 internal reset circuitry delays the external reset for 10 ms, allowing the stabilization of the on chip phase lock loop. The delayed reset signal (i.e., internal reset signal) is used to reset all internal modules of the SPCA554A. At the end of the internal reset signal, the SPCA554A latches values on the LGPIO bus to determine the

IO-TRAP configuration. Core power must be supplied before IO power to avoid accidental signal conflicts. During the IO-TRAP working period (10 ms after external reset), the LCMGPIO bus must be stable because the SPCA554A latches the bus value for its power-on configuration. If the IO-TRAP latches false values, the SPCA554A cannot function normally. The trap signal is an observable IO pin useful for IO-TRAP function debug.

Table 3-1: Description of Figure: 3-1

The following figure shows a conceptual internal reset circuit. The RSTNN pin can also be driven by the host processor (with GPIO). But the host processor must guarantee that RSTNN is de-asserted after power is stable.

Figure 3-2: SPCA554A internal reset circuit

Besides hardware reset, the SPCA554A has software set to all the internal modules. Internal modules, which can be reset by software, include sensor controller, color DSP, Display controller, host bridge, 2D graphics engine, USB controller, MPEG/JPEG

engine, SDRAM controller, storage media controller and DMA controller. These modules can be reset independently by the internal RISC CPU or by the host controller. The RISC CPU can also be reset by the host processor.

## **4.BOOT SEQUENCE**

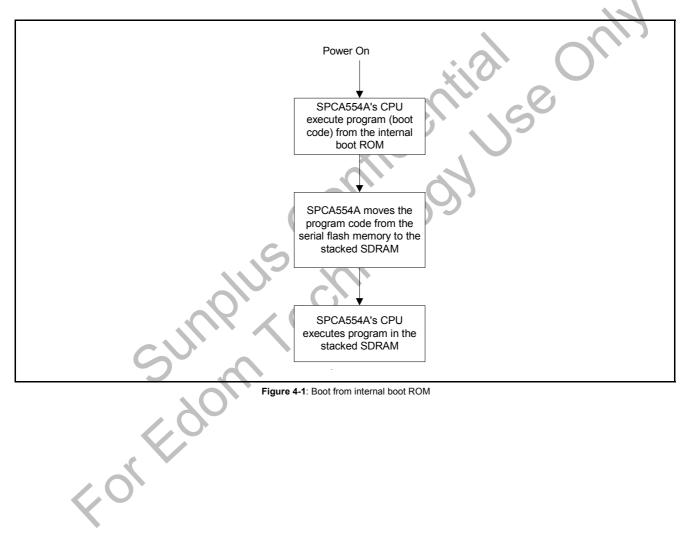

The SPCA554A supports two boot sources. The first is boot from the host processor, the other is boot from the internal boot ROM. The boot source is selected by IO-TRAP[7].

## 4.1. Boot From Internal Boot ROM

The SPCA554A internal boot ROM is a 16K-byte mask ROM, which contains the boot code. The boot code includes the

program shadow function from the external serial flash memory to the stacked low power SDRAM. The boot code also includes the ISP (In-system-programming) function for host processor update of code in external serial flash. Program shadowing is code moved from external serial flash memory to stacked low power SDRAM, and then being executed. Figure 4.1 shows the flow of booting from the internal boot ROM.

## Preliminary SPCA554A

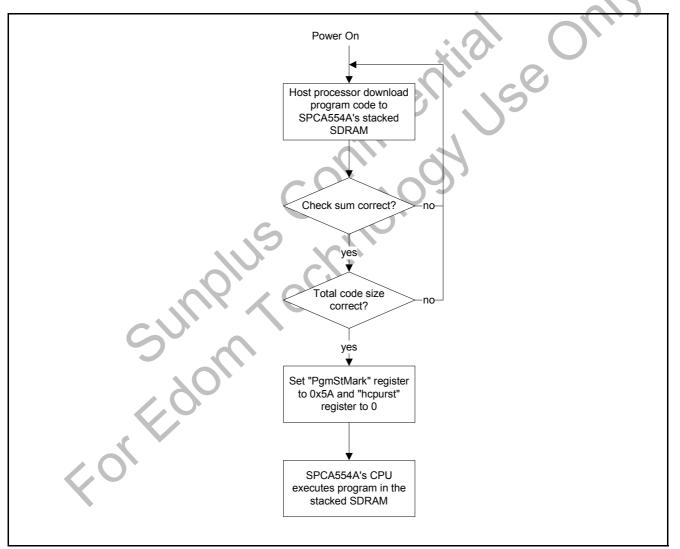

### 4.2. Boot From The Host Processor

If this configuration is selected, the SPCA554A internal CPU stays in the reset state after power-on. The internal CPU does not start to execute program in the stacked SDRAM until after the "PgmStMark " register in the host bridge is set to 0x5A and the "hcpurst" register is cleared to 0. From the host processor point-of-view, the host processor must download the program code to the stacked SDRAM of the SPCA554A, set the "PgmStMark " register to 0x5A, and set the "hcpurst" register to 0, and then the SPCA554A internal CPU will then start running. Figure 4.2 shows the operational flow from the host processor point-of-view. Note that the SPCA554A automatically generates check sum from the program code it receives from the host processor. And that the total byte count of the program code is also recorded in the host bridge register. After the code is downloaded, the host processor should check the check sum and byte count of the program code for data integrity.

Figure 4-2: Boot from the host processor

## **5.POWER MANAGEMENT**

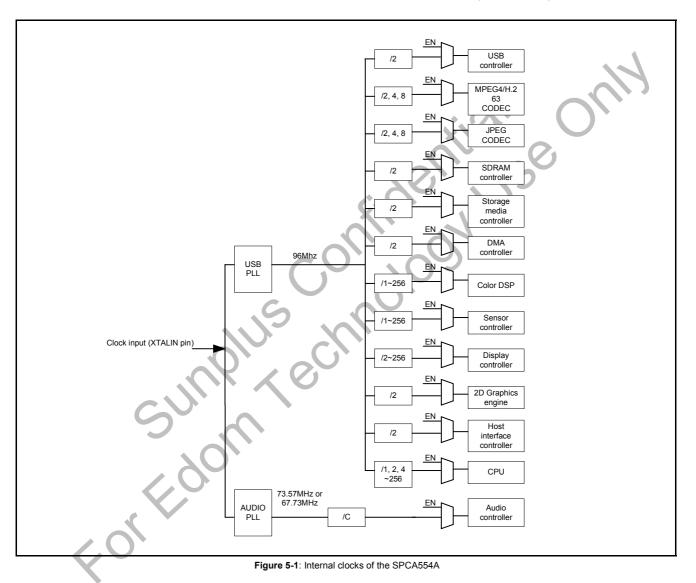

## 5.1. Internal Clock Control

All major clocks to the internal building blocks of the SPCA554A can be turned off by software. The following diagram shows the internal clock structure of the SPCA554A. To achieve minimum

power consumption, these clocks must be manipulated according to the tasks that the SPCA554A executes. Unused clocks should be turned off to minimize power consumption.

The clock usages in different operation modes are show in the following table:

|                | USB<br>Controller | Audio<br>Controller | MPEG | JPEG<br>CODEC | SDRAM<br>Controller | Storage<br>media<br>Controller | DMA<br>Controller | Color DSP | Sensor<br>Controller | Display<br>Controller | 2D<br>Graphics | Host Bridge | RISC CPU |

|----------------|-------------------|---------------------|------|---------------|---------------------|--------------------------------|-------------------|-----------|----------------------|-----------------------|----------------|-------------|----------|

| Idle           | N                 | N                   | Ν    | N             | Y                   | N                              | Ν                 | Ν         | Ν                    | Ν                     | Ν              | Ν           | Y        |

| Reset          | Y                 | Y                   | Y    | Y             | Y                   | Y                              | Y                 | Y         | Y                    | Y                     | Y              | Y           | Y        |

| SPCA554A Boot  | Ν                 | N                   | Ν    | N             | Y                   | O(1)                           | O(1)              | Ν         | Ν                    | Ν                     | Ν              | O(2)        | O(1)     |

| Camera Preview | Ν                 | N                   | Ν    | Ν             | Y                   | Ν                              | Ν                 | Y         | Y                    | Y                     | O(3)           | Y           | Y        |

## Preliminary

## SPCA554A

|                              | USB<br>Controller | Audio<br>Controller | MPEG | JPEG<br>CODEC | SDRAM<br>Controller | Storage<br>media<br>Controller | DMA<br>Controller | Color DSP | Sensor<br>Controller | Display<br>Controller | 2D<br>Graphics | Host Bridge | RISC CPU |

|------------------------------|-------------------|---------------------|------|---------------|---------------------|--------------------------------|-------------------|-----------|----------------------|-----------------------|----------------|-------------|----------|

| PC-Camera                    | Y                 | Ν                   | N    | Y             | Y                   | Ν                              | Y                 | Y         | Y                    | Y                     | N              | Y           | Y        |

| Still mage Capture           | Ν                 | Ν                   | Ν    | Y             | Y                   | Y                              | Y                 | Y         | Y                    | Y                     | O(3)           | Y           | Y        |

| Still Image Playback         | Ν                 | Ν                   | Ν    | Y             | Y                   | Y                              | Y                 | Ν         | Ν                    | Y                     | O(3)           | Y           | Y        |

| Video Recording              | Ν                 | Y                   | Y    | Y             | Y                   | Y                              | Y                 | Y         | Y                    | Y                     | O(3)           | Y           | Y        |

| Video Playback               | Ν                 | Y                   | Y    | Y             | Y                   | Y                              | Y                 | Y         | N                    | Y                     | O(3)           | Y           | Y        |

| Audio Record/Playback        | Ν                 | Y                   | Ν    | Ν             | Y                   | Y                              | Y                 | N         | N                    | Y                     | N              | Y           | Y        |

| JAVA Application             | Ν                 | Y                   | Ν    | Ν             | Y                   | Y                              | Y                 | N         | N                    | Y                     | Υ              | Y           | Y        |

| Host Compression             | Ν                 | Ν                   | Y    | Y             | Y                   | Ν                              | Ν                 | N         | N                    | Y                     | Y              | Y           | Y        |

| Screen Saver                 | Ν                 | Ν                   | Y    | Y             | Y                   | Ν                              | N                 | N         | N                    | Y                     | Y              | Y           | Y        |

| LCM Bypass Mode<br>(Suspend) | Ν                 | Ν                   | Ν    | N             | Ν                   | Ν                              | N                 | N         | N                    | Ν                     | N              | Ν           | Ν        |

Table 5-1: Power management for the SPCA554A

N: Clock to the module should be turned-off.

Y: Clock to the module must be turn-on.

- O(1): Clock supply depends on the boot source. If the SPCA554A boots from serial flash memory, the storage media controller, the DMA controller and the CPU must be supplied with clocks.

- O(2): If the SPCA554A boots from the host, the clock must be turned-on.

- O(3): Whether the 2D graphics engine clock must be turned on depends on the application. For example, in still image capture, the 2D graphics engine is required only to create photo sticker. Plain image capture does not require the 2D graphics engine to function.

## 5.2. Deep Power Down Mode

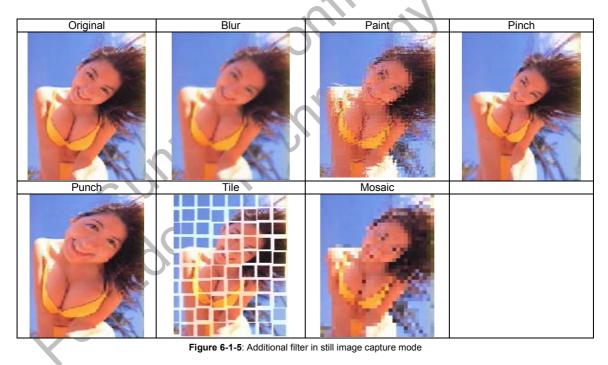

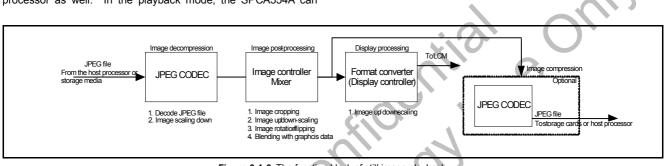

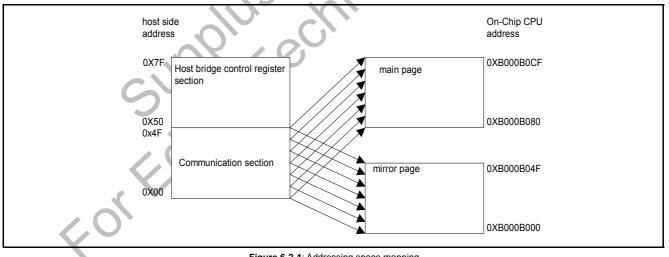

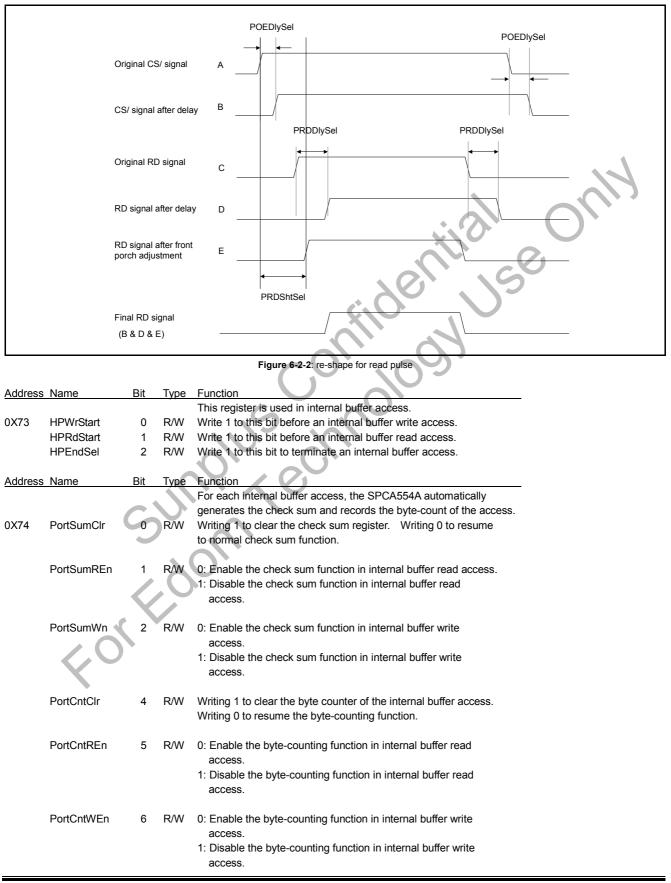

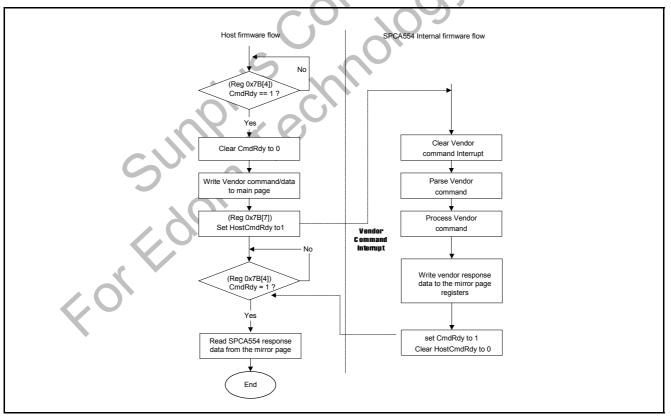

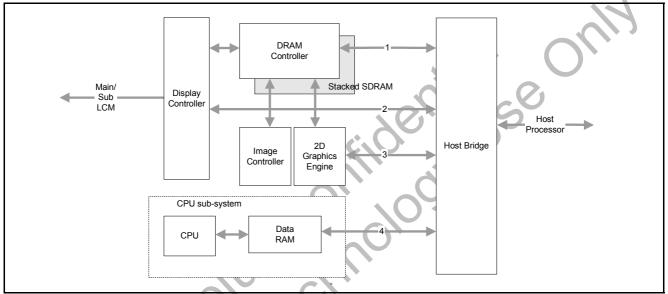

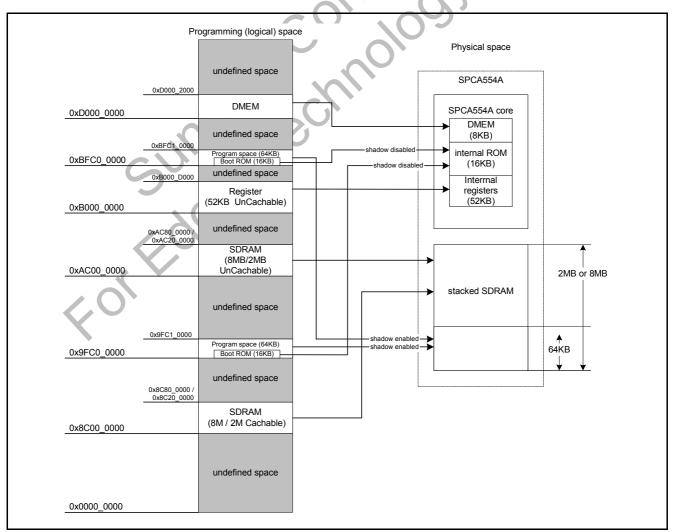

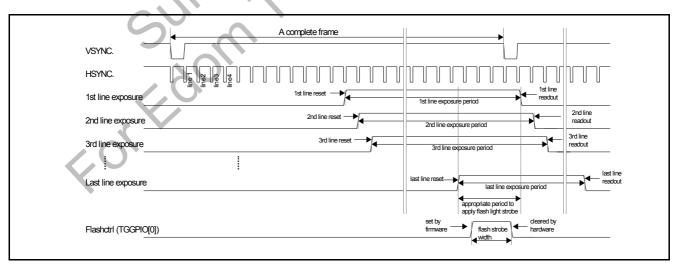

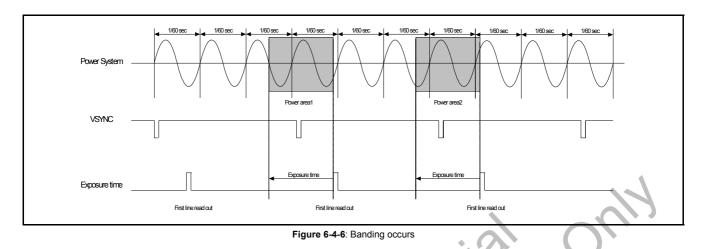

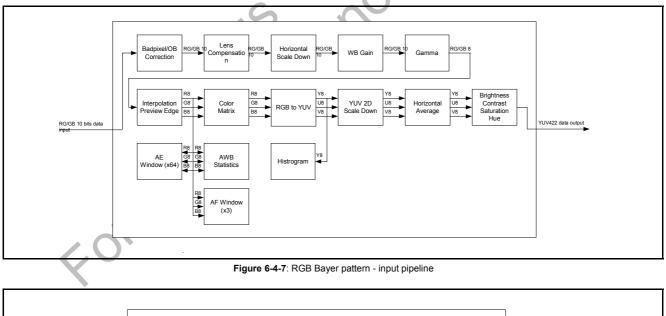

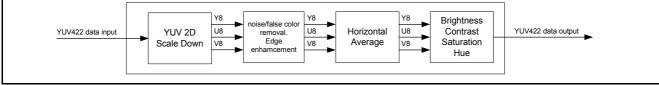

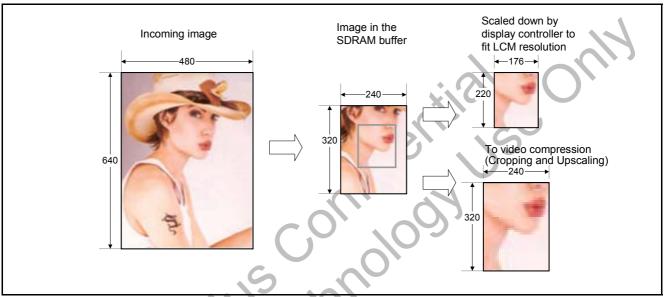

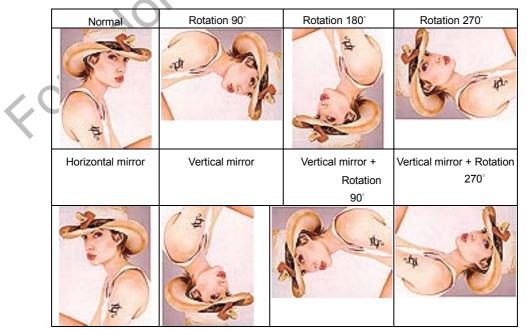

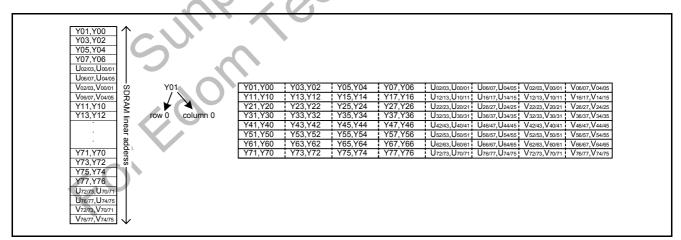

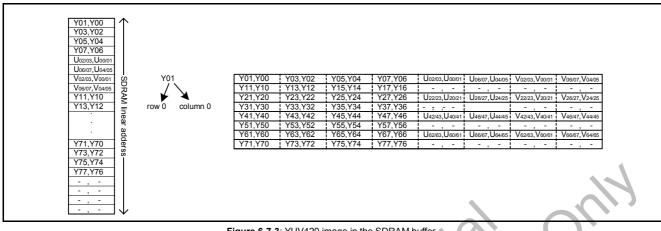

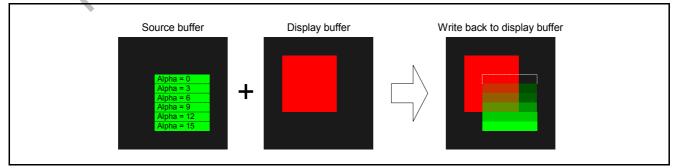

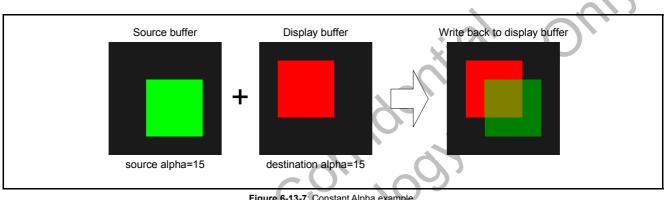

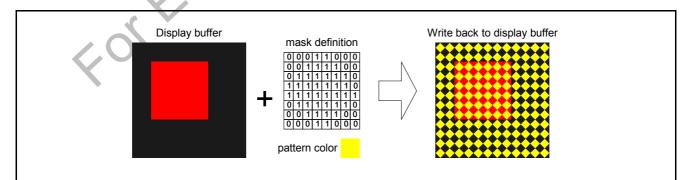

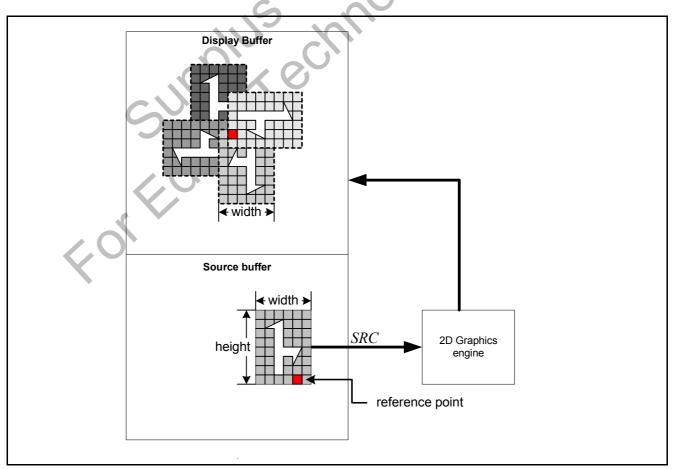

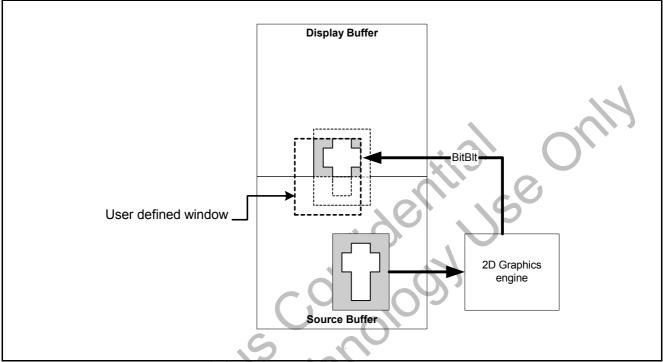

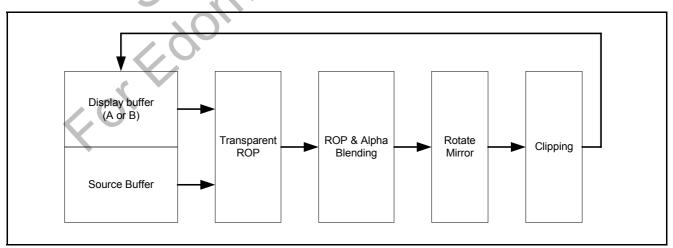

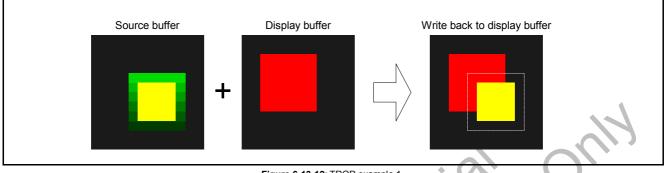

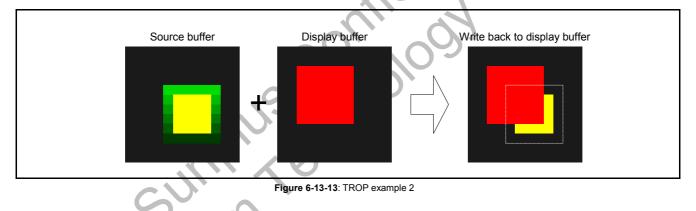

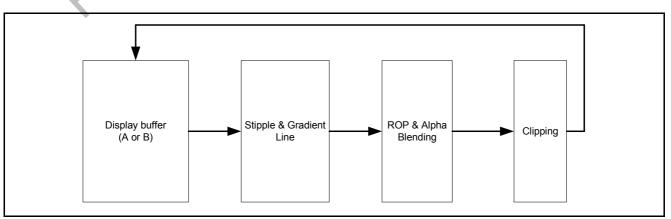

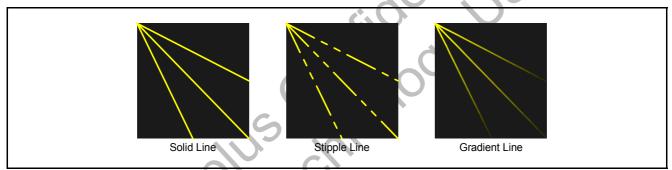

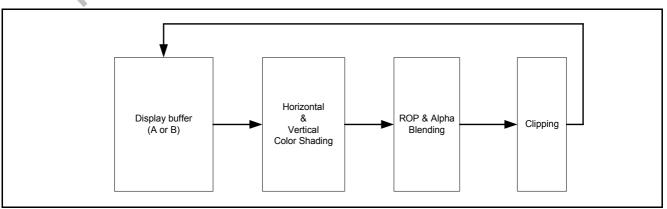

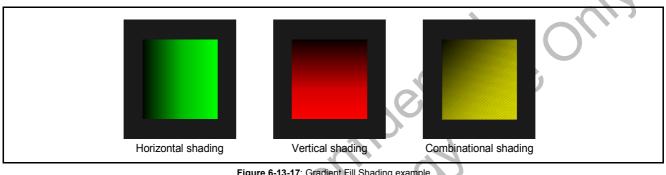

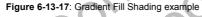

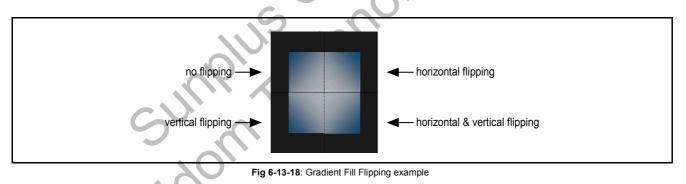

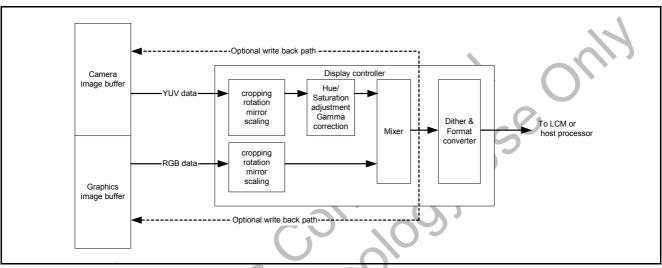

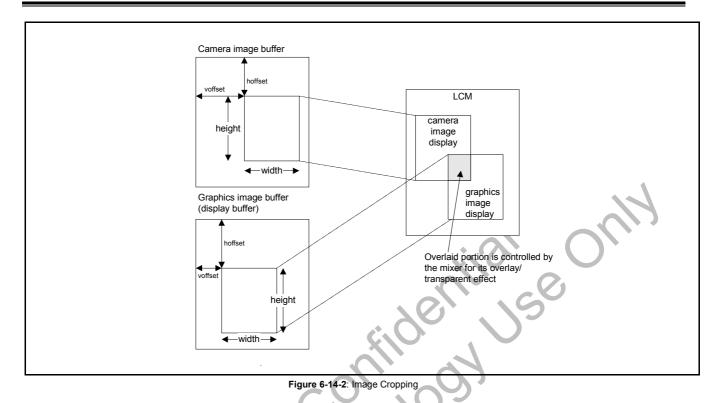

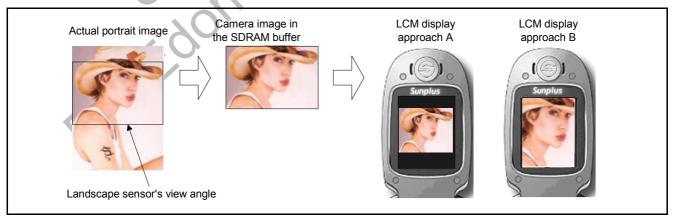

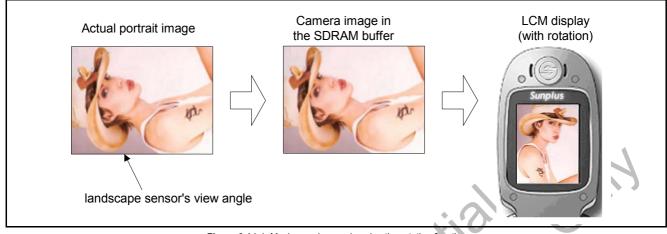

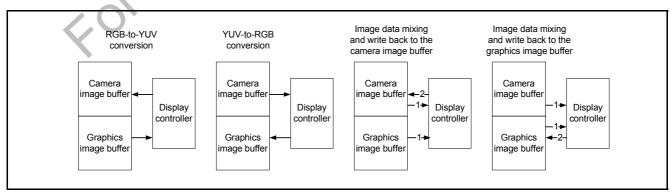

The SPCA554A supports the deep power down mode, in which all the internal clocks stop. The PLL also stops working in the deep power down mode. The deep power down mode is often refered to as the suspend mode in this specification. All functions of the SPCA554A do not work in the suspend mode except the bypass function. The host processor can still access the LCM by asserting the BYPASS signal.