## GT-64242

## System Controller for MIPS Processors

### **FEATURES**

Integrated system controller with PCI interface for high-performance embedded control applications.

### Supports 64-bit bus MIPS CPUs:

- PMC-Sierra RM5260, RM5270, RM7000A and RM7000C

- IDT RC5000 and RC64575

- NEC Rv5000 and Rv5464

- LSI Viper

#### CPU interface features:

- Multiplexed 64-bit address/data bus (36-bit address, 64-bit data).

- Up to 100MHz CPU bus frequency.

- 2.5V or 3.3V CPU bus interface.

- 256 byte write posting buffer that accepts up to six CPU cache line writes with zero wait-states

- 64 byte CPU read buffer that accepts up to two cache line CPU reads.

- Supports RM700A split read transactions (two outstanding reads) with out-of-order completion.

- Supports R4000 and pipeline write modes (also available in multiple GT-64242 configuration).

- Supports R5000/R7000 CPU caches.

### CPU address remapping to PCI.

Supports access, write, and caching protection to configurable address ranges.

Supports up to four multiple GT-64242 devices on the same CPU bus.

Supports both Little and Big Endian modes.

Synchronization barrier support between the CPU and the PCI.

#### SDRAM controller:

- 64-bit wide (+ 8-bit ECC) SDRAM interface.

- · Up to 100MHz SDRAM frequency.

- · 3.3V SDRAM interface.

- Supports SDRAM and registered SDRAM.

- · Four DRAM banks.

- · 1MB-1GB bank address space.

- · Up to 4GB DRAM address space.

- Supports 2-way & 4-way SDRAM bank interleaving.

- Supports 16/64/128/256/512 Mbit SDRAM.

- · Supports up to 16 pages open.

# Supports the Unified Memory Architecture Stan-

- Allows for external masters access to SDRAM directly.

- Allows glueless multiple GT–64242 devices share the same SDRAM.

#### **Device controller:**

- A dedicated 32-bit multiplexed address/data bus (separated from SDRAM bus).

- Up to 100MHz bus frequency.

- 3.3V device interface.

- Five chip selects.

- 1MB-512MB bank address space.

- Up to 2.5GB Device address space.

- Programmable timing for each chip select.

- Supports many types of standard memory and I/O devices.

- Optional external wait-state support.

- 8-,16-,32-bit width device support.

- Support for boot ROMs.

### Four channels DMA controller:

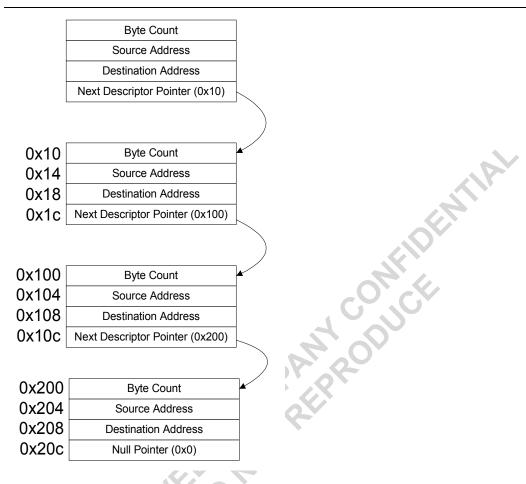

- Chaining via linked-lists of records.

- Byte address boundary for source and destination.

- Moves data between the PCI, SDRAM, Devices, and CPU buses.

- Two 2Kbyte internal FIFOs allowing transfers to take place concurrently.

- Alignment of source and destination addresses.

- Increment or hold of source and destination addresses.

- DMAs can be initiated by the CPU, external DMAReg\* signal, or an internal timer/counter.

- Termination of DMA transfer on each channel.

- Descriptor ownership transfer to CPU.

- Supports unlimited burst DMA transfers between the SDRAM and the PCL

http://www.galileoT.com

Doc. No. MV-S100424-00 Rev. A

http://www.marvell.com

Page 1

## FEATURES (CONTINUED)

# One high-performance PCI 2.2 compliant interface.

- PCI bus speed of up to 66MHz with zero wait states.

- Operates either synchronous or asynchronous to CPU clock, at slower, equal, or faster clock frequency.

- 32/64-bit PCI master and target operations.

- Supports flexible byte swapping through the PCI interface.

- 3.3V PCI buffers (configurable 3.3/5V).

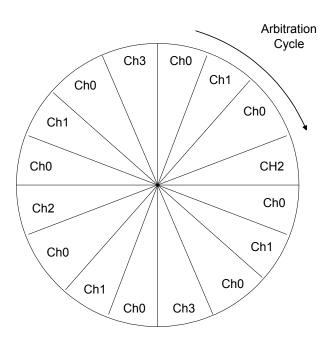

- Configurable PCI arbiter for up to six external masters, plus the internal master.

#### Master specific features:

- 512 bytes posted write buffer and 512 bytes read buffer for unlimited DMA bursts between SDRAM and the PCI.

- Host to PCI bridge translates CPU cycles to PCI I/ O or Memory cycles.

- Supports 64-bit addressing through Dual Address cycles.

- Supports configuration, interrupt acknowledge, and special cycles on the PCI bus.

#### Target specific features:

- · PCI to main memory bridge.

- 512 bytes posted write buffer and 1Kbyte read prefetch buffer for unlimited bursts between the PCI and SDRAM.

- · Up to eight delayed reads.

Page 2

- Read prefetch of up to 1Kbyte.

- Supports fast back-to-back transactions.

- Supports memory and I/O transactions to internal configuration registers.

- Supports 64-bit addressing through dual address cycles.

- Synchronization barrier support between the PCI and the CPU.

- · PCI address remapping to resources.

- Supports access and write protect to configurable address ranges.

# PCI Hot-Plug and CompactPCI Hot-Swap ready compliant.

### **Messaging Unit:**

- Efficient messaging interface between the PCI and the CPU, or between the two PCI interfaces.

- Doorbell and message interrupts between the CPU and the PCI.

- I<sub>2</sub>O support.

### **Plug and Play Support:**

- Plug and Play compatible configuration registers.

- PCI configuration registers can be accessed from the CPU or PCI side.

- · Expansion ROM support.

- VPD support.

- PCI Power Management compliant.

- Message signal interrupt support.

- BIST support.

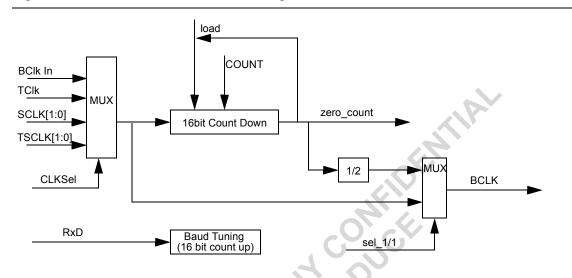

# Three baud rate generators with multiple clock sources.

# 32 multi purpose pins (MPP) dedicated for peripheral functions and general purpose I/Os (GPP).

Doc. No. MV-S100424-00 Rev. A

- Each pin can be configured independently.

- GPP inputs can generate a maskable interrupt.

## FEATURES (CONTINUED)

Data integrity support between the CPU, PCI, and DRAM interfaces:

- · ECC support on SDRAM interface.

- · Parity support on the CPU and PCI busses.

- Propagation of parity and ECC errors between the three interfaces.

- · Full error report, including error counter.

- · Support corruption of ECC bank for debug.

### Interrupt controller:

- Maskable interrupts to CPU and PCI.

- · Drive up to seven interrupt pins.

Four 32-bit wide timer/counters initiated by the CPU or externally through the MPP pin.

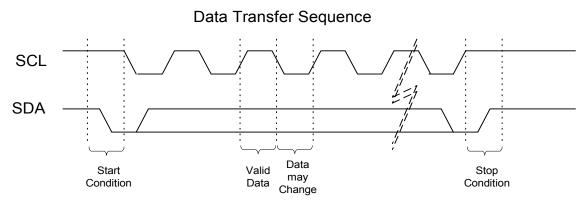

I<sup>2</sup>C interface that supports master and slave operations.

Serial ROM initialization through I<sup>2</sup>C interface.

Advanced 0.18 micron process.

Doc. No. MV-S100424-00 Rev. A

665 PBGA package

Doc. No. MV-S100424-00 Rev. A

| Document Co                                                         | onventions                                                                                                                                                                                                                                                        |  |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| The following name and usage conventions are used in this document: |                                                                                                                                                                                                                                                                   |  |

| Signal Range                                                        | A signal name followed by a range enclosed in brackets represents a range of logically related signals. The first number in the range indicates the most significant bit (MSb) and the last number indicates the least significant bit (LSb).  Example: GTXD[7:0] |  |

| Active Low Signals *                                                | A * symbol at the end of a signal name indicates that the signal's active state occurs when voltage is low.  Example: INT*                                                                                                                                        |  |

| Document Status            |                                                                                                                                                                                                                          |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced<br>Information    | This datasheet contains design specifications for initial product development. Specifications may change without notice. Contact Marvell Field Application Engineers for more information.                               |

| Preliminary<br>Information | This datasheet contains preliminary data, and a revision of this document will be published at a later date. Specifications may change without notice. Contact Marvell Field Application Engineers for more information. |

| Final<br>Information       | This datasheet contains specifications on a product that is in final release. Specifications may change without notice. Contact Marvell Field Application Engineers for more information.                                |

#### Disclaimer

Preliminary or Advanced Information: This document provides preliminary or advanced information about the product described. All specifications described herein are based on design goals only. Do not use for final design. Visit Marvell's web site at www.marvell.com or call 1-866-674-7253 for the latest information on Marvell products.

#### DISCLAIMER

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no warranty of any kind, expressed or implied, with regard to any information contained in this document, including, but not limited to, the implied warranties of merchantability or fitness for any particular purpose. Further, Marvell does not warrant the accuracy or completeness of the information, text, graphics, or other items contained within this document. Marvell makes no commitment either to update or to keep current the information contained in this document. Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use Marvell products in these types of equipment or applications. The user should contact Marvell to obtain the latest specifications before finalizing a product design.

Marvell assumes no responsibility, either for use of this product or for any infringements of patents and trademarks, or other rights of third parties resulting from its use. No license is granted under any patents, patent rights, or trademarks of Marvell. These products may include one or more optional functions. The user has the choice of implementing any particular optional function. Should the user choose to implement any of these optional functions, it is possible that the use could be subject to third party intellectual property rights. Marvell recommends that the user investigate whether third party intellectual property rights are relevant to the intended use of this product and obtain licenses as appropriate under relevant intellectual property rights.

Marvell comprises Marvell Technology Group Ltd. (MTGL) and its subsidiaries, Marvell International Ltd. (MIL), Marvell Semiconductor, Inc. (MSI), Marvell Asia Pte Ltd. (MAPL), Marvell Japan K.K. (MJKK), Galileo Technology Ltd. (GTL) and Galileo Technology Inc. (GTI). Copyright © 200x Marvell. All Rights Reserved. Marvell, GalNet, Gallieo, Galileo Technology, Fastwriter, Moving Forward Faster, Alaska, the M logo, GalTis, GalStack, GalRack, NetGX, the Max logo, Communications Systems on Silicon, and Max bandwidth trademarks are the property of Marvell. All other trademarks are the property of their respective owners.

Galileo / Marvell 2350 Zanker Road San Jose, CA 95131 Phone: 1 408 367-1400 Fax: 1 (408) 367-1401 www.galileoT.com www.marvell.com

Document Status: Preliminary

## **Table of Contents**

| 1. | Overview                                               |    |

|----|--------------------------------------------------------|----|

|    | 1.2 SDRAM Interface                                    |    |

|    |                                                        |    |

|    | 1.3 Device Interface                                   |    |

|    | 1.4 PCI Interface                                      |    |

|    | 1.5 DMA Engines                                        |    |

|    | 1.6 Data Integrity                                     |    |

| 2. | Pin Information                                        | 21 |

| 3. | Address Space Decoding                                 | 33 |

|    | 3.1 CPU Address Decoding                               | 33 |

|    | 3.2 PCI Address Decoding                               |    |

|    | 3.3 Disabling Address Decoders                         | 36 |

|    | 3.4 IDMA Unit Address Decoding                         | 36 |

|    | 3.5 Address Space Decoding Errors                      | 36 |

|    | 3.6 Default Memory Map                                 | 37 |

|    | 3.7 Programming Address Decoding Registers             | 40 |

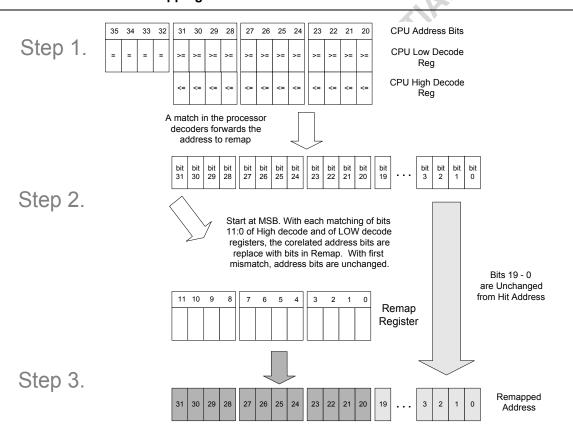

|    | 3.8 Address Remapping                                  |    |

|    | 3.9 IDMA Unit Address Decoding Override                |    |

| 4. | CPU Interface                                          | 44 |

|    | 4.1 CPU Address Decoding                               |    |

|    | 4.2 CPU Access Protection                              | 44 |

|    | 4.3 CPU Slave Operation                                | 45 |

|    | 4.4 MIPS 64-bit Multiplexed Address/Data Bus Interface | 45 |

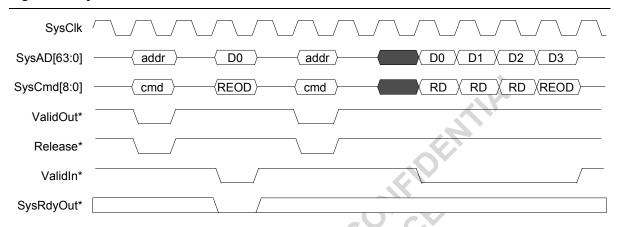

|    | 4.5 RM7000 Split Transactions Support                  |    |

|    | 4.6 Burst Support                                      | 52 |

|    | 4.7 Transactions Flow Control                          | 53 |

|    | 4.8 MIPS CPU Cache Support                             | 54 |

|    | 4.9 Multi-GT Support                                   | 55 |

|    | 4.10Parity Support                                     |    |

|    | 4.11CPU Endian Support                                 |    |

|    | 4.12CPU Synchronization Barrier                        |    |

|    | 4.13Clocks Synchronization                             | 59 |

|    | 4.14Programing the CPU Configuration Register          | 60 |

|    | 4.15CPU Interface Registers                            | 60 |

| 5. | SDRAM Controller                          | 84  |

|----|-------------------------------------------|-----|

|    | 5.1 SDRAM Controller Implementation       |     |

|    | 5.2 DRAM Type                             | 85  |

|    | 5.3 SDRAM Density                         | 86  |

|    | 5.4 SDRAM Timing Parameters               | 88  |

|    | 5.5 SDRAM Burst                           | 89  |

|    | 5.6 SDRAM Interleaving                    |     |

|    | 5.7 SDRAM Open Pages                      | 94  |

|    | 5.8 Read Modify Write                     | 95  |

|    | 5.9 SDRAM Refresh                         | 96  |

|    | 5.10SDRAM Initialization                  | 98  |

|    | 5.11SDRAM Operation Mode Register         | 98  |

|    | 5.12Heavy Load Interface                  | 100 |

|    | 5.13SDRAM Clocking                        | 100 |

|    | 5.14Unified Memory Architecture Support   | 101 |

|    | 5.15SDRAM Interface Registers             | 105 |

| 6. | Address and Data Integrity                | 115 |

|    | 6.1 CPU Parity Support                    | 115 |

|    | 6.2 SDRAM ECC                             | 115 |

|    | 6.3 Parity Support for Devices            | 120 |

|    | 6.4 PCI Parity Support                    |     |

|    | 6.5 Parity/ECC Errors Propagation         | 120 |

| 7. | Device Controller                         | 122 |

|    | 7.1 Device Controller Implementation      | 122 |

|    | 7.2 Device Timing Parameters              | 123 |

|    | 7.3 Data Pack/Unpack and Burst Support    | 124 |

|    | 7.4 Ready* Support                        | 125 |

|    | 7.5 Additional Device Interface Signaling | 127 |

|    | 7.6 Error Report                          | 128 |

|    |                                           |     |

|    | 7.7 Interfacing With 8/16/32-Bit Devices  | 128 |

| 8.  | PCI Interface                       | . 135 |

|-----|-------------------------------------|-------|

|     | 8.1 PCI Master Operation            | . 135 |

|     | 8.2 PCI Master Termination          | . 137 |

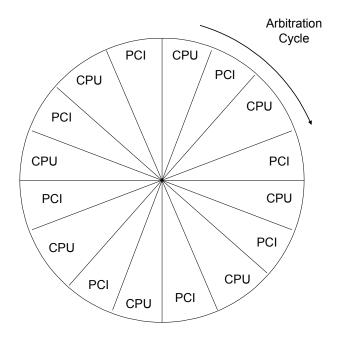

|     | 8.3 PCI Bus Arbitration             | . 137 |

|     | 8.4 PCI Master Configuration Cycles | . 139 |

|     | 8.5 PCI Target Address Decoding     | . 141 |

|     | 8.6 PCI Access Protection           |       |

|     | 8.7 PCI Target Operation            | . 143 |

|     | 8.8 PCI Target Termination          | . 146 |

|     | 8.9 Initialization Retry            | . 147 |

|     | 8.10Synchronization Barrier         | . 148 |

|     | 8.11Clocks Synchronization          |       |

|     | 8.12Data Endianess                  | . 149 |

|     | 8.1364-bit PCI Interface            | . 150 |

|     | 8.1464-bit Addressing               | . 151 |

|     | 8.15PCI Parity and Error Support    | . 152 |

|     | 8.16Configuration Space             | . 152 |

|     | 8.17PCI Special Features            | . 156 |

|     | 8.18PCI Interface Registers         | . 161 |

| 9.  | Messaging Unit                      | . 216 |

|     | 9.1 Message Registers               | . 216 |

|     | 9.2 Doorbell Registers              | . 217 |

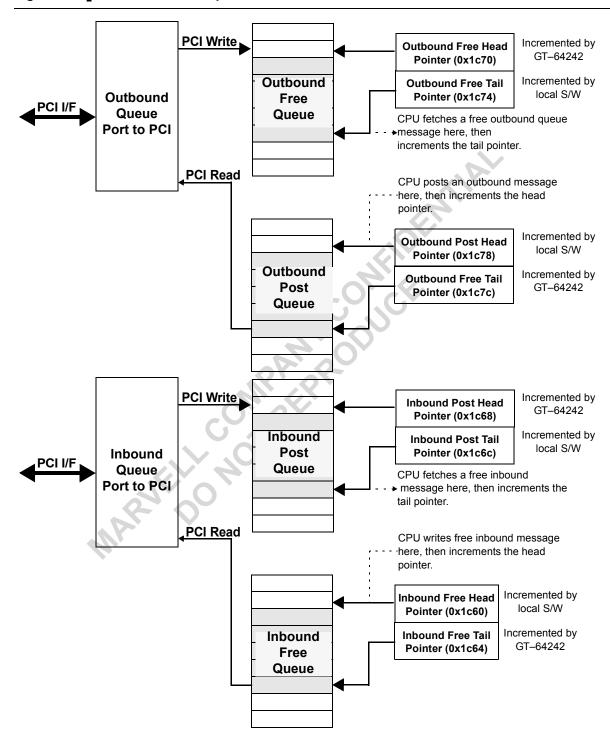

|     | 9.3 Circular Queues                 | . 218 |

|     | 9.4 Messaging Unit Registers        | . 224 |

| 10. | IDMA Controller                     | 234   |

|     | 10.1IDMA Operation                  |       |

|     | 10.2IDMA Descriptors                | . 234 |

|     | 10.3IDMA Address Decoding           | . 236 |

|     | 10.4IDMA Access Protection          | . 236 |

|     | 10.5IDMA Channel Control            | . 236 |

|     | 10.6Arbitration                     | . 243 |

|     | 10.7Big and Little Endian Support   | . 243 |

|     | 10.8DMA Interrupts                  | . 244 |

|     | 10.9IDMA Registers                  | . 244 |

| 11. | Timer/Counters                      | 263   |

|     | 11.1Timers/Counters Registers       |       |

|     | -                                   |       |

| 12.  | Baude Rate Generators (BRG)                            |                   |

|------|--------------------------------------------------------|-------------------|

|      | 12.1BRG Inputs and Outputs                             |                   |

|      | 12.2BRG Baud Tuning                                    |                   |

| 40   | •                                                      |                   |

| 13.  | Watchdog Timer                                         |                   |

|      | 13.2Watchdog Operation                                 |                   |

| 4.4  | General Purpose Port                                   |                   |

| 14.  | 14.1GPP Control Registers                              | <b>212</b><br>272 |

|      | 14.2GPP Value Register                                 |                   |

|      | 14.3GPP Interrupts                                     | 272               |

|      | 14.4General Purpose Port Registers                     | 273               |

| 15.  | MPP Multiplexing                                       | 275               |

| 15.  | 15.1MPP Multiplexing                                   | 275               |

|      | 15.2MPP Interface Registers                            | 276               |

| 16.  | I2C Interface                                          | 289               |

| . •. | 16.1I2C Bus Operation                                  | 289               |

|      | 16.2I2C Registers                                      |                   |

|      | 16.3I2C Master Operation                               | 294               |

|      | 16.4I2C Slave Operation                                | 295               |

|      | 16.5I2C Interface Registers                            | 296               |

| 17.  | Interrupt Controller                                   | 299               |

|      | 17.1Interrupt Cause and Mask Registers                 |                   |

|      | 17.2Interrupt Controller Registers                     | 300               |

| 18.  | Internal Arbitration Control                           | 307               |

| 19.  | Reset Pins                                             | 310               |

| 20.  | Reset Configuration                                    | 311               |

|      | 20.1Pins Sample Configuration                          |                   |

|      | 20.2Serial ROM Initialization                          | 314               |

| 21.  | GT-64242 Clocking                                      | 319               |

| 22.  | DC Characteristics                                     | 320               |

|      | 22.1Absolute and Recommended Operating Conditions      |                   |

|      | 22.2DC Electrical Characteristics Over Operating Range | 321               |

|      | 22.3Thermal Data                                       | 324               |

|      | 22.4PLL Power Filter Circuit                           | 324               |

|      |                                                        |                   |

| AC Timing                               | 327                       |

|-----------------------------------------|---------------------------|

| Pinout Table, 665 Pin BGA               | 331                       |

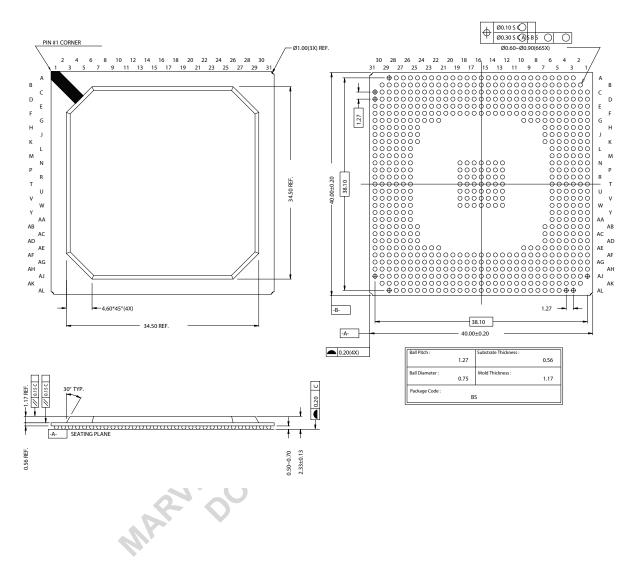

| 665 PBGA Package Mechanical Information | 342                       |

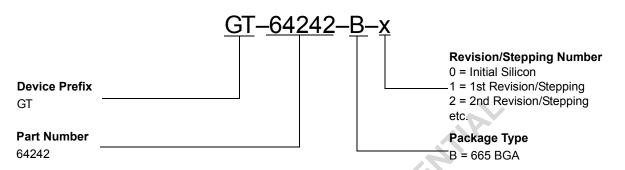

| GT-64242 Part Numbering                 | 343                       |

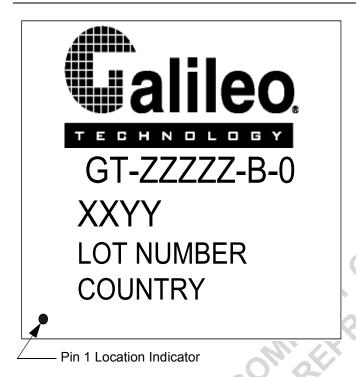

| GT-64242 Part Marking and Pin Location  | 344                       |

| Revision History                        | 345                       |

| MIARATE DO NOT REEP ROBLICE             |                           |

|                                         | Pinout Table, 665 Pin BGA |

## **List of Tables**

| 2. | Pin Inforr | mation                                                   | 21 |

|----|------------|----------------------------------------------------------|----|

|    | Table 1:   | Pin Assignment Table Conventions                         | 21 |

|    | Table 2:   | Core Clock Pin Assignments                               | 22 |

|    | Table 3:   | CPU Interface Pin Assignments                            | 22 |

|    | Table 4:   | PCI Bus Interface Pin Assignments                        | 24 |

|    | Table 5:   | SDRAM Interface Pin Assignments                          | 28 |

|    | Table 6:   | Device Interface Pin Assignments                         |    |

|    | Table 7:   | MPP Interface Pin Assignment                             | 30 |

|    | Table 8:   | I2C Interface Pin Assignments                            | 30 |

|    | Table 9:   | JTAG Interface Pin Assignments                           | 31 |

|    | Table 10:  | MPP Pins Functionality                                   | 31 |

| 3. |            | Space Decoding                                           |    |

|    | Table 11:  | CPU Interface Address Decoder Mappings                   |    |

|    | Table 12:  | PCI Interface Address Decoder Mappings                   |    |

|    | Table 13:  | PCI Interface 64-bit Addressing Address Decoder Mappings | 35 |

|    | Table 14:  | CPU Default Address Mapping                              |    |

|    | Table 15:  | PCI Default Address Mapping                              | 38 |

|    | Table 16:  | 64-bit Addressing PCI Default Address Mapping            | 39 |

|    | Table 17:  | PCI Address Remapping Example                            |    |

| 4. | CPU Inter  | rface                                                    | 44 |

|    | Table 18:  | CPU Interface Signals                                    | 46 |

|    | Table 19:  | Read/Write Request Command Bits Summary                  | 47 |

|    | Table 20:  | Null Request Command Bits Summary                        | 47 |

|    | Table 21:  | Data Identifier Bits Summary                             | 48 |

|    | Table 22:  | Partial Word Byte Lane                                   | 48 |

|    | Table 23:  | 64-bit Bus Sub-block Ordering                            | 53 |

|    | Table 24:  | Multi-GT ID Encoding                                     | 57 |

|    | Table 25:  | CPU Address Decode Register Map                          | 60 |

|    | Table 26:  | CPU Control Register Map                                 | 61 |

|    | Table 27:  | CPU Sync Barrier Register Map                            | 62 |

|    | Table 28:  | CPU Access Protection Register Map                       | 62 |

|    | Table 20.  | CPLL Error Report Register Man                           | 62 |

# **List of Tables (Continued)**

| 5. | SDRAM C    | controller                                  | 84    |

|----|------------|---------------------------------------------|-------|

|    | Table 96:  | Address Control for 16Mbit SDRAM            | 92    |

|    | Table 97:  | Address Control for 64/128Mbit SDRAM        | 92    |

|    | Table 98:  | Address Control for 256/512Mbit SDRAM       | 93    |

|    | Table 99:  | SDRAM Configuration Register Map            | . 105 |

|    | Table 100: | SDRAM Banks Parameters Register Map         | . 105 |

|    | Table 101: | Error Report Register Map                   | . 106 |

| 6. | Address a  | and Data Integrity                          | . 115 |

|    | Table 121: | ECC Code Matrix                             | . 115 |

| 7. | Device Co  | ontroller                                   | . 122 |

|    |            | 8-bit Devices                               |       |

|    | Table 123: | 16-bit Devices                              | . 129 |

|    | Table 124: | 32-bit Devices                              | . 129 |

|    | Table 125: | Device Control Register Map                 | . 129 |

|    | Table 126: | Device Interrupts Register Map              | . 130 |

| 8. | PCI Interf | ace                                         | . 135 |

|    |            | DevNum to IdSel Mapping                     |       |

|    | Table 140: | Data Swap Control                           | . 149 |

|    | Table 141: | 32-bit PCI Byte and Word Swap Settings      | . 149 |

|    | Table 142: | 64-bit PCI Byte and Word Swap Settings      | . 150 |

|    | Table 143: | PCI Slave Address Decoding Register Map     | . 161 |

|    | Table 144: | PCI Control Register Map                    | . 162 |

|    | Table 145: | PCI Configuration Access Register Map       | . 164 |

|    | Table 146: | PCI Error Report Register Map               | . 164 |

|    | Table 147: | PCI Configuration, Function 0, Register Map | . 164 |

|    | Table 148: | PCI Configuration, Function 1, Register Map | . 165 |

|    | Table 149: | PCI Configuration, Function 4, Register Map | . 165 |

|    | Table 150: | PCI Configuration, Function 5, Register Map | . 166 |

|    | Table 151: | PCI Configuration, Function 6, Register Map | . 166 |

|    | Table 152: | PCI Configuration, Function 7, Register Map | . 166 |

| 9. | Messagin   | g Unit                                      | . 216 |

|    | Table 286: | Circular Queue Starting Addresses           | . 219 |

|    | Table 287: | I2O Circular Queue Functional Summary       | . 222 |

|    | Table 288: | Messaging Unit Register Map                 | . 224 |

|    | Table 300: | Outbound Queue Port Virtual Register        | . 229 |

# **List of Tables (Continued)**

|     | IDAGA G. J. II                                                  |     |

|-----|-----------------------------------------------------------------|-----|

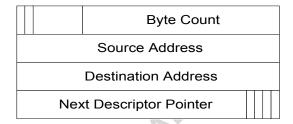

| 10. | Table 311: DMA Descriptor Definitions                           |     |

|     | Table 312: IDMA Descriptor Register Map                         |     |

|     | Table 313: IDMA Control Register Map                            |     |

|     | Table 314: IDMA Interrupt Register Map                          |     |

|     | Table 315: IDMA Debug Register Map                              |     |

|     |                                                                 |     |

| 11. | Timer/Counters                                                  |     |

|     | Table 370: IDMA Descriptor Register Map                         |     |

| 12. | Baude Rate Generators (BRG)                                     | 267 |

|     | Table 378: BRG Registers Map                                    |     |

| 13. | Watchdog Timer                                                  | 270 |

|     | Table 382: Watchdog Configuration Register (WDC), Offset 0xb410 |     |

|     | Table 383: Watchdog Value Register (WDV), Offset 0xb414         | 271 |

| 14. | General Purpose Port                                            | 272 |

|     | Table 384: GPP Register Map                                     |     |

| 15. | MPP Multiplexing                                                | 275 |

| 13. | Table 390: MPP Function Summary                                 | 275 |

|     | Table 391: GPP Interface Register Map                           |     |

| 46  | I2C Interface                                                   |     |

| 16. | Table 396: I2C Control Register Bits                            |     |

|     | Table 397: I2C Status Codes                                     |     |

|     | Table 398: I2C Interface Register Map                           |     |

|     |                                                                 |     |

| 17. | Interrupt Controller  Table 406: Interrupts Cause Registers     |     |

|     | Table 400: Interrupts Cause Registers                           |     |

|     |                                                                 |     |

| 20. | Reset Configuration                                             |     |

|     | Table 420: Reset Configuration                                  | 311 |

| 22. | DC Characteristics                                              |     |

|     | Table 425: Absolute Maximum Ratings                             |     |

|     | Table 426: Recommended Operating Conditions                     |     |

|     | Table 427: Pin Capacitance                                      |     |

|     | Table 428: DC Electrical Characteristics Over Operating Range   |     |

|     | Table 429: Thermal Data for The GT–64242 in BGA 665             | 324 |

| 23. | AC Timing                                                       | 327 |

|     | Table 430: 100 MHz AC Timing                                    | 327 |

## **List of Tables (Continued)**

Doc. No. MV-S100424-00 Rev. A

| 24. | Pinout Table, 665 Pin BGA        | 331 |

|-----|----------------------------------|-----|

|     | Table 431: GT-64242 Pinout Table |     |

| 28. | Revision History                 | 345 |

|     | Table 432: Revision History      |     |

MARVE DO NOT REPRODUCE

# **List of Figures**

| 2. | Pin Inforn | nation                                                  | 21  |

|----|------------|---------------------------------------------------------|-----|

|    | Figure 1:  | GT-64242 Interfaces                                     | 21  |

| 3. | Address    | Space Decoding                                          |     |

|    | Figure 2:  | CPU Address Decode Example                              |     |

|    | Figure 3:  | Bank Size Register Function Example (16Meg Decode)      | 36  |

|    | Figure 4:  | CPU Address Remapping                                   |     |

| 4. | CPU Inter  | rface                                                   |     |

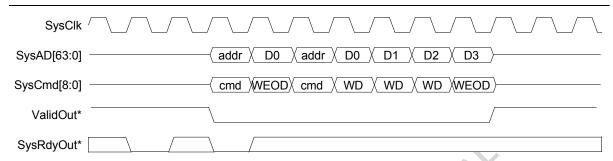

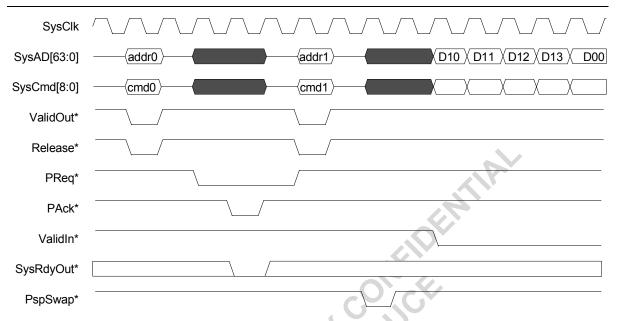

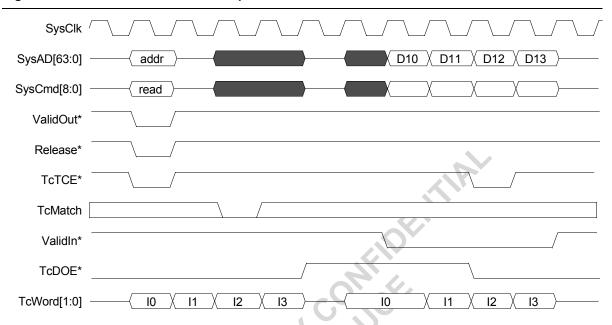

|    | Figure 5:  | SysAD Read Protocol                                     |     |

|    | Figure 6:  | SysAD Write Protocol                                    | 51  |

|    | Figure 7:  | R7000 Split Read Transaction Example                    | 52  |

|    | Figure 8:  | R7000 L3 Read Miss Example                              | 55  |

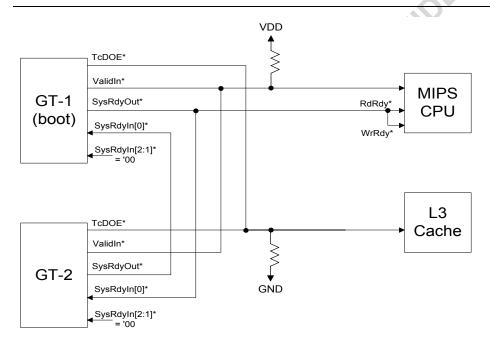

|    | Figure 9:  | Multi-GT-64242 Hardware Connections to the MIPS CPU Bus | 56  |

|    | Figure 10: |                                                         |     |

| 5. | SDRAM C    | Controller                                              | 84  |

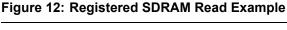

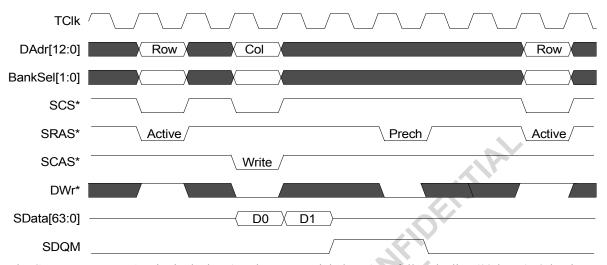

|    | Figure 11: | SDRAM Read Example                                      |     |

|    | Figure 12: |                                                         |     |

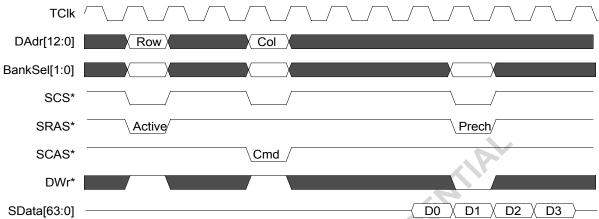

|    | Figure 13: | SDRAM Timing Parameters                                 | 89  |

|    | Figure 14: | Burst Write Termination Example                         | 90  |

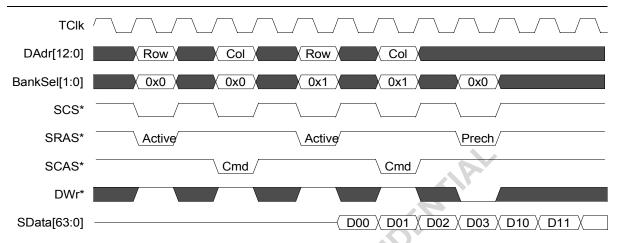

|    | Figure 15: | Virtual DRAM Banks Interleaving Example                 | 91  |

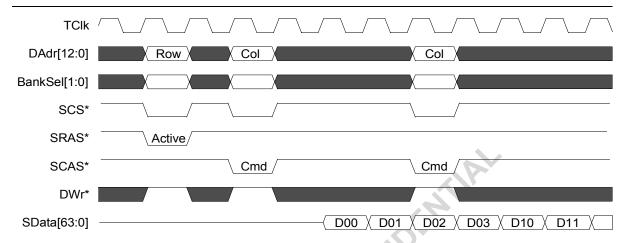

|    | Figure 16: | Sequential Accesses to the Same Page                    | 95  |

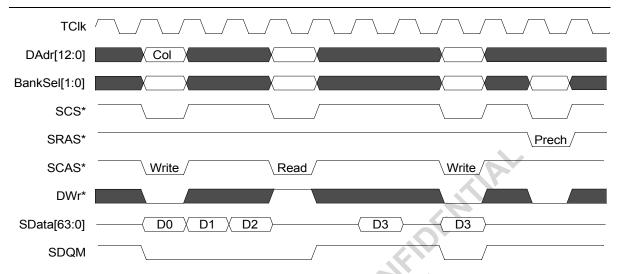

|    | Figure 17: | SDRAM RMW Example                                       | 96  |

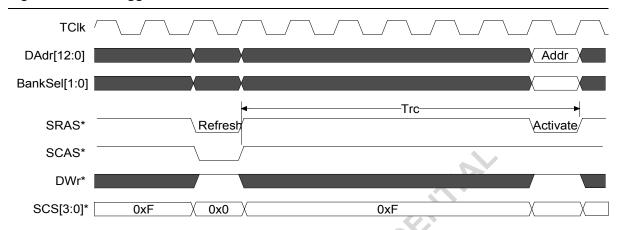

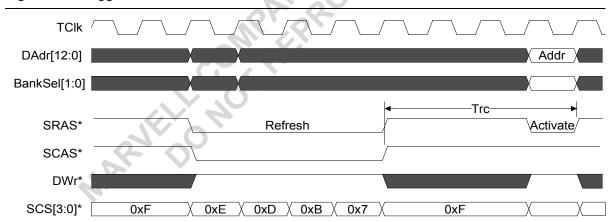

|    | Figure 18: | Non-Staggered Refresh Waveform                          | 97  |

|    | Figure 19: | Staggered Refresh Waveform                              | 97  |

|    | Figure 20: | Heavy Load Example                                      | 100 |

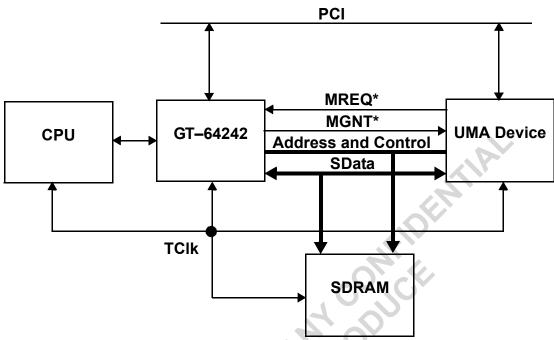

|    | Figure 21: | UMA Device and GT-64242 Sharing SDRAM                   | 102 |

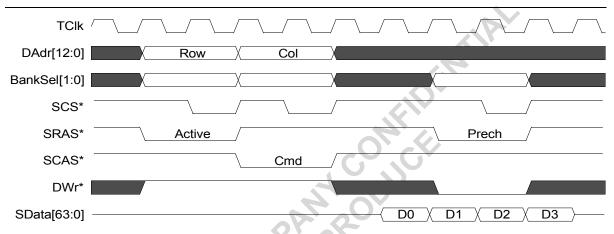

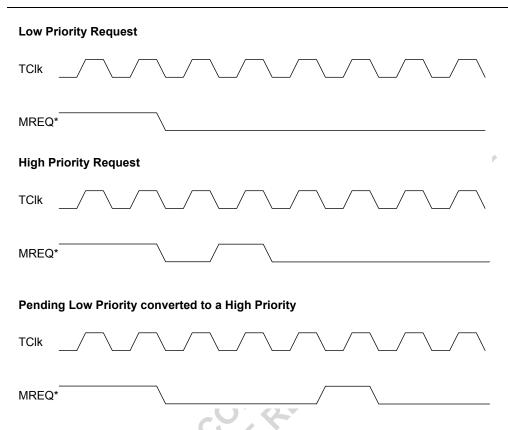

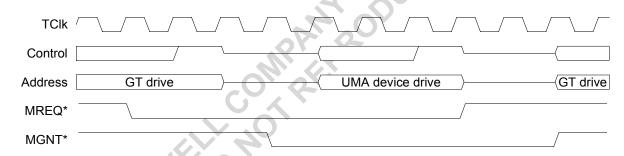

|    | Figure 22: | UMA Device Requests                                     | 103 |

|    | Figure 23: | Handing the Bus Over                                    | 104 |

| 7. | Device Co  | ontroller                                               | 122 |

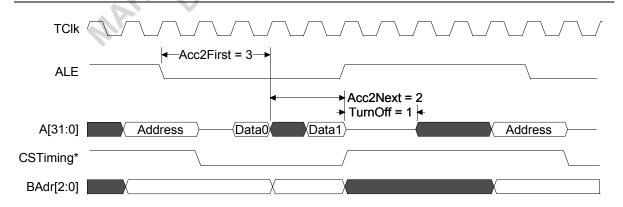

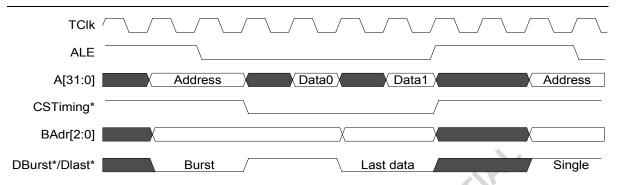

|    | Figure 24: | Device Read Parameters Example                          | 123 |

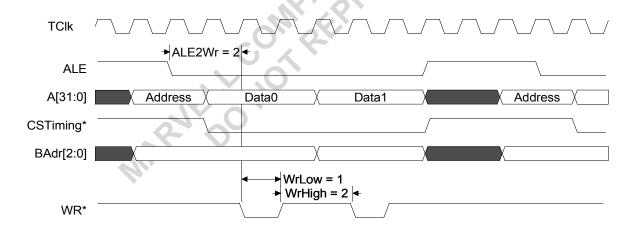

|    | Figure 25: | Device Write Parameters Example                         | 124 |

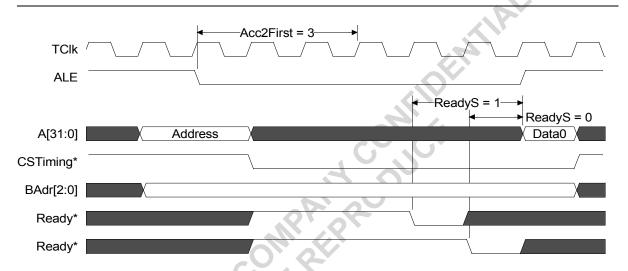

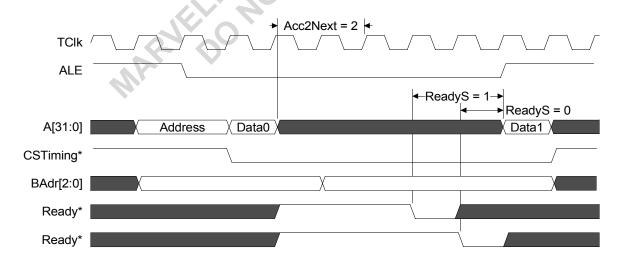

|    | Figure 26: | Ready* Extending Acc2First                              | 126 |

|    | Figure 27: | Ready* Extending Acc2Next                               | 126 |

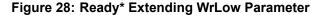

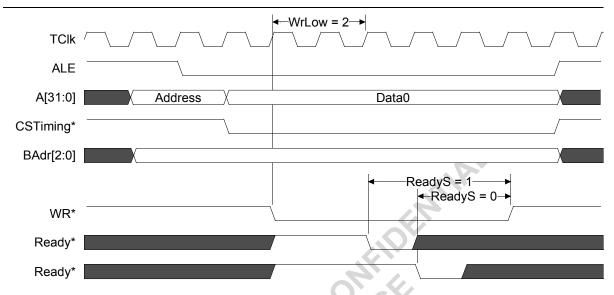

|    | Figure 28: | Ready* Extending WrLow Parameter                        | 127 |

|    | Figure 29: | DBurst*/Dlast* Example                                  | 128 |

# **List of Figures (Continued)**

| 8.  | <b>PCI</b> Interf | ace                                                       | 135 |

|-----|-------------------|-----------------------------------------------------------|-----|

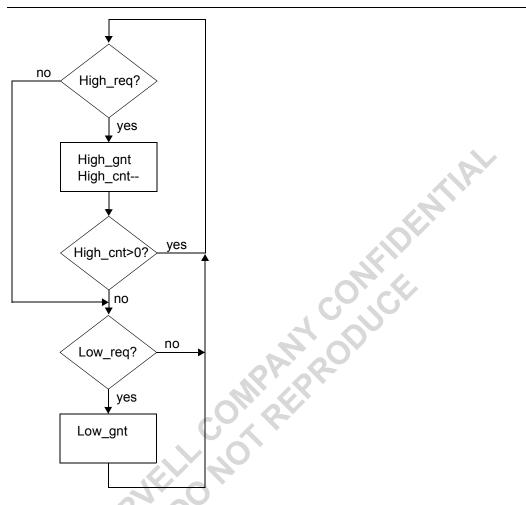

|     | Figure 30:        | Internal PCI Arbiter Flow                                 | 139 |

|     | Figure 31:        | CPU Sync Barrier Example                                  | 148 |

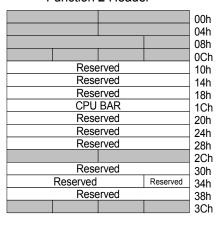

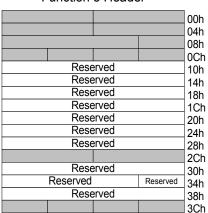

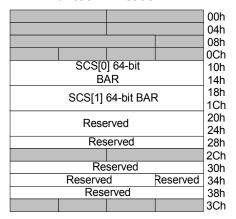

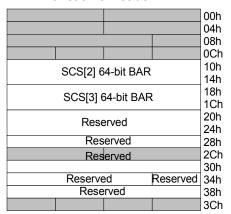

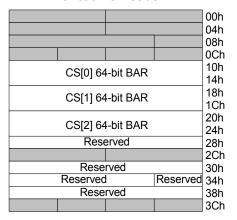

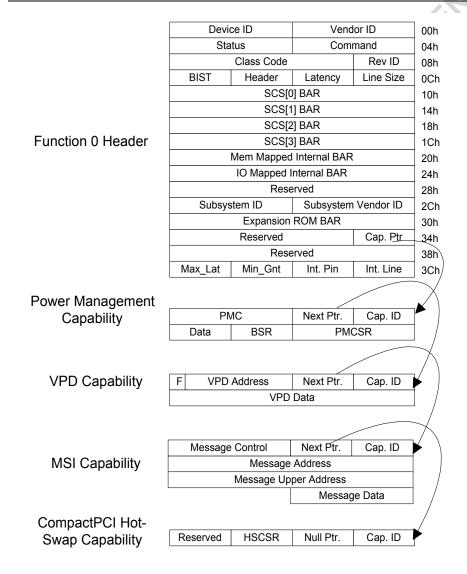

|     | Figure 32:        | PCI Configuration Space Header                            | 154 |

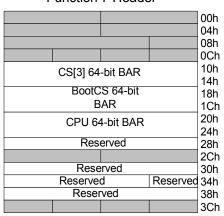

|     | Figure 33:        | PCI Configuration Space Header                            | 155 |

|     | Figure 34:        | GT-64242 Capability List                                  | 156 |

| 9.  | Messagin          | ng Unit                                                   | 216 |

|     | -                 | I2O Circular Queue Operation                              |     |

| 10. | IDMA Cor          | ntroller                                                  | 234 |

|     |                   | IDMA Descriptors                                          |     |

|     | Figure 37:        | Chained Mode IDMA                                         | 238 |

|     |                   | Configurable Weights Arbiter                              |     |

| 12. | Baude Ra          | ate Generators (BRG)                                      | 267 |

|     | _                 | Baud Rate Generator Block Diagram                         |     |

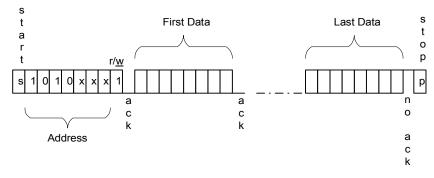

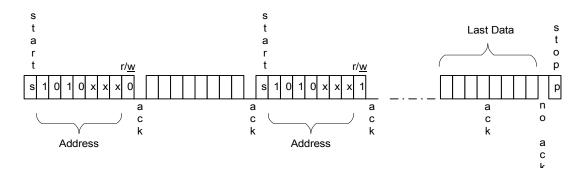

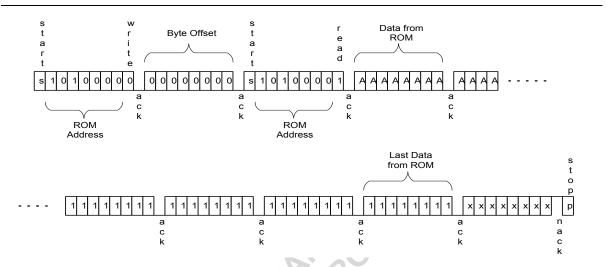

| 16. | I2C Interf        | ace                                                       | 289 |

|     |                   | I2C Examples                                              |     |

| 18. | Internal A        | Arbitration Control                                       | 307 |

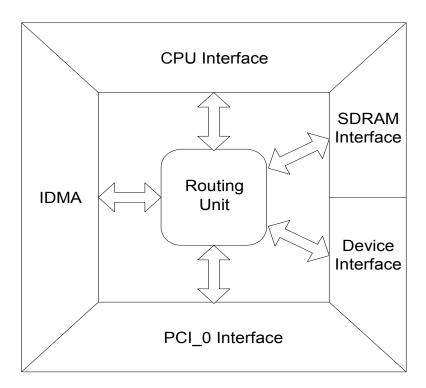

|     | Figure 41:        | GT-64242 Inter Units Connect                              | 307 |

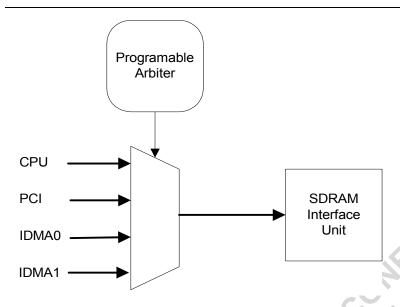

|     | Figure 42:        | SDRAM Interface Arbitration                               | 308 |

|     | Figure 43:        | Configurable Weights Arbiter                              | 308 |

| 20. | Reset Co          | nfiguration                                               | 311 |

|     |                   | Serial ROM Data Structure                                 |     |

|     | Figure 45:        | Serial ROM Read Example                                   | 316 |

| 22. | DC Chara          | octeristics                                               | 320 |

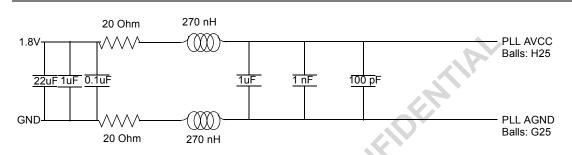

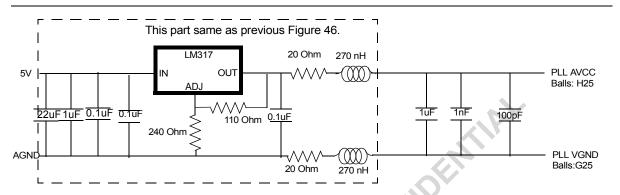

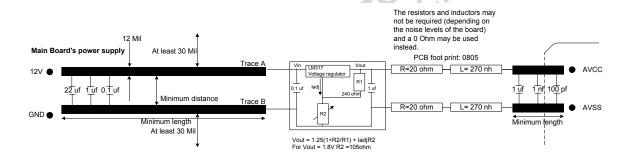

|     | Figure 46:        | PLL Power Filter Circuit With Common On-board 1.8V Supply | 325 |

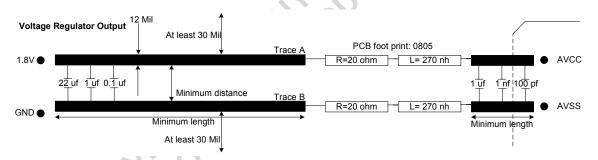

|     | Figure 47:        | PLL Layout Guideline for a PCI Add-on Card                | 325 |

|     | Figure 48:        | PLL Power Filter Circuit With Dedicated 1.8V Supply       | 326 |

|     | Figure 49:        | PLL Layout Guideline for Backplane Layout                 | 326 |

| 24. | Pinout Ta         | ıble, 665 Pin BGA                                         | 331 |

|     | Figure 50:        |                                                           |     |

|     | Figure 51:        | GT-64242 Pinout Map (top view, right section)             | 341 |

# **List of Figures (Continued)**

| 26. | GT-64242 Part Numbering |                               |     |  |  |  |

|-----|-------------------------|-------------------------------|-----|--|--|--|

|     |                         |                               | 343 |  |  |  |

| 27. | GT-64242                | Part Marking and Pin Location | 344 |  |  |  |

|     |                         |                               | 344 |  |  |  |

MARVE DO NOT REPRODUCE

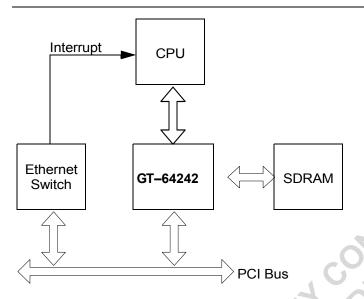

## 1. OVERVIEW

The GT–64242 provides a single-chip solution for designers building systems for a MIPS64-bit bus CPU. The GT–64242 architecture supports several system implementations for different applications.

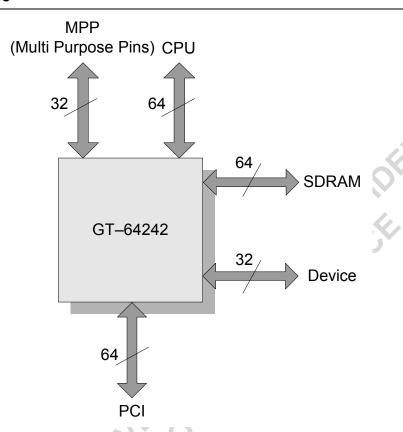

The GT-64242 has a four bus architecture:

- A 64-bit interface to the CPU bus

- A 64-bit interface to SDRAM.

- A 32-bit interface to Devices.

- One 64-bit PCI interfaces.

The four buses are de-coupled from each other in most accesses, enabling concurrent operation of the CPU bus, PCI devices, and accesses to memory. For example, the CPU bus can write to the on-chip write bufferor a PCI device can write into an on-chip FIFO, all simultaneously.

### 1.1 CPU Bus Interface

The GT-64242 supports MIPS bus protocol. With a maximum frequency of 100MHz, the CPU can transfer in excess of 1 Gbytes/sec.

**NOTE:** The QED RM7000C CPU is now supported in TTL mode, only.

The GT-64242 supports up to two pipelined transactions on the CPU bus. For example, if the CPU initiates a data read from the PCI interface and starts a code read from SDRAM, the two cycles are pipelined. The CPU interface reads from the PCI interface and from SDRAM in parallel.

By the time read data is returned from the PCI interface, read data from SDRAM is already available – since an SDRAM access is faster than a PCI access. The GT–64242 drives the data of the SDRAM read immediately after a PCI read data with zero wait states. In case of a RM7000 CPU, that supports out of order read completion, the GT–64242 drives the SDRAM read data first and then the PCI read data that arrives later.

The CPU can connect with up to four GT–64242 or any other 60x compatible slave devices. This increases the flexibility of system design significantly.

**NOTE:** The increased loading has a small effect on the system's maximum operating frequency.

The GT-64242 supports CPU address remapping to the PCI interface. It also supports access, write, and caching protection, per user specified address ranges.

The GT-64242 CPU interface supports both Little and Big Endian modes.

**NOTE:** For additional information about the CPU bus interface, see Section 4. "CPU Interface" on page 44.

## 1.2 SDRAM Interface

The GT-64242 SDRAM controller supports SDRAM and registered SDRAM. It supports 16/64/128/256/512 Mbit SDRAMs.

The GT-64242 works at frequencies up to 100MHz, and can address up to 4GBytes.

Up to four banks of SDRAM may be connected to The GT-64242.

The controller supports two bank interleaving for 16 Mbit SDRAMs and four bank interleaving for 64/128/256/ 512 Mbit SDRAMs.

The GT-64242 also supports page mode, which minimizes SDRAM cycles on multiple transactions to the same SDRAM page, and can be configured to support up to 16 simultaneously opened pages.

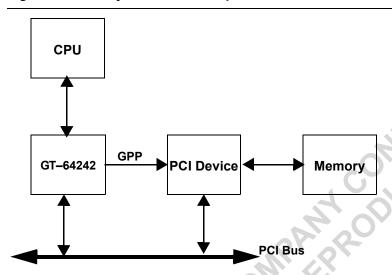

The GT-64242 supports the Unified Memory Architecture (UMA) protocol that enables external masters to arbitrate for direct access to SDRAM. This feature enhances system performance and gives flexibility when designing shared memory systems.

NOTE: For additional information about the SDRAM interface, see Section 5. "SDRAM Controller" on page

#### **Device Interface** 1.3

The GT-64242 device controller supports different types of memory and I/O devices.

It has the control signals and the timing programmability to support devices such as SynBurst SRAM, Flash, EPROMs, FIFOs, and I/O controllers. Device widths of 8-, 16-, and 32-bits are supported.

The GT-64242 has a dedicated 32-bit Device bus. It supports bursts of up to 32 bytes to a 32-bit wide device and can run SDRAM and Device transactions simultaneously, so SDRAM access performance is not affected by access to slow memory devices.

**NOTE:** For additional information about the Device interface, see Section 7. "Device Controller" on page 122.

#### 1.4 **PCI** Interface

The GT-64242 interfaces directly with one 64-bit PCI busses, operating at a maximum frequency of 66MHz. The PCI interface can act as a master initiating a PCI bus transaction or as a target responding to a PCI bus transac-

The GT-64242 becomes the PCI bus master when the CPU, DMA, or Comm port initiates a bus cycle to a PCI device. It's internal buffers allow unlimited DMA bursts between PCI and memory. It supports all PCI commands including 64-bit addressing using DAC cycles.

The GT-64242 acts as a target when the PCI device initiates a memory access. It responds to all memory read/ write accesses, including DAC, and to all configuration and I/O cycles, in the case of internal registers. It's internal buffers allow unlimited burst reads and writes. It supports up to eight pending delayed reads.

There are no restrictions between the PCI and CPU clock ratios. It is possible for the PCI clock speed to be slower, equal, or faster than the CPU clock. It is also optional to synchronize the PCI clock to the CPU clock.

It is possible to program the PCI slave to retry all PCI transactions targeted to the GT-64242, during CPU initialization.

The PCI slave performs PCI address remapping to SDRAM and Devices. It also supports configurable read prefetch, access and write protect, and byte swapping per user specified address ranges.

The GT-64242 PCI interface is fully PCI rev. 2.2 compliant. It contains all the required PCI configuration registers. All internal registers, including the PCI configuration registers, are accessible from the CPU bus or the PCI bus.

The GT-64242 configuration register set is PC Plug and Play compatible. It supports PCI spec rev. 2.2 features such as VPD, message signal interrupt, and power management.

The GT-64242 also supports PCI Hot-Plug and CompactPCI Hot-Swap ready.

The GT-64242 also includes a messaging unit to support industry standard I<sub>2</sub>O messaging. This includes:

- Two doorbell registers.

- Two message registers.

- Four messages queues located in SDRAM.

NOTE: For additional information about the PCI interface, see Section 8. "PCI Interface" on page 135.

## 1.5 DMA Engines

The GT-64242 incorporates four high performance DMA engines. Each DMA engine has the capability to transfer data between PCI devices, SDRAM, or devices.

The DMA uses two internal 2Kbyte FIFOs for temporary DMA data storage. Two FIFOs allows two DMA channels to work concurrently since each channel utilizes a FIFO. For example, channel0 transfers data from SDRAM to PCI using one FIFO, while channel2 transfers data from external system memory to device using the other FIFO.

Source and destination addresses can be non-aligned on any byte address boundary. The DMA channels are programmable by the CPU or without CPU bus intervention via a linked list of descriptors. This linked list is loaded by the DMA controller into the channel's working set when a DMA transaction ends. The DMA supports increment/hold on source and destination addresses independently, and alignment of addresses towards source and destination.

It is possible to initiate a DMA transfer by the software writing to a register, an external request via a DMAReq\* pin, or an internal timer/counter. Four End of Transfer pins act as inputs to the GT–64242 and allow ending a DMA transfer on a certain channel. In cases of chained mode with the transfer completed, it is possible to transfer the descriptor to CPU ownership. The CPU can calculate the number of remaining bytes in the buffer associated with the closed descriptor.

**NOTE:** For additional information about the DMA engines, see Section 10. "IDMA Controller" on page 234.

## 1.6 Data Integrity

The GT-64242 supports full data integrity on its different interfaces.

The GT-64242 supports ECC on SDRAM. It supports detection and correction of one error, detection of two errors, and detection of three and four errors, if they are in the same nibble. It supports SDRAM read-modify-write for partial writes. It has full error report, including ECC error counter. It also supports corruption of ECC bank for debug.

The GT-64242 supports parity checking and generation on the PCI bus through PAR and PERR\* signals. It also supports configured SERR\* assertion for different errors. In cases of error detection, address and data are latched for debug.

The GT-64242 also supports data parity checking and generation on the CPU bus. In case of error detection, an interrupt is asserted. As with error detection on the PCI bus, address and data are latched for debug.

ECC and parity errors are optionally propagated between the interfaces. For example, in case of a PCI read from SDRAM that results in detection of uncorrectable ECC error, the GT-64242 may drive the wrong PAR value with the read data on the PCI bus.

aress and contribution of the little of the NOTE: For additional information about data integrity features, see Section 6. "Address and Data Integrity" on page 115.

## 2. PIN INFORMATION

Figure 1 shows the GT-64242 interfaces.

Figure 1: GT-64242 Interfaces

Table 1 lists the conventions that apply to I/O or O type pins described in the Pin Assignment tables:

**Table 1: Pin Assignment Table Conventions**

| Abbreviation | Description                                                                                                                                    |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| t/s          | Tri-State pin.                                                                                                                                 |

| s/t/s        | Sustained Tri-State pin.  Driven to its inactive value for one cycle before float.  NOTE: A pull-up is required to sustain the inactive value. |

| o/d          | Open Drain pin. Allows multiple drivers simultaneously (wire-OR connection).  NOTE: A pull-up is required to sustain the inactive value.       |

#### Table 2: **Core Clock Pin Assignments**

| Pin Name/<br>Ball #     | Type | Full Name      | Description                                                                                                                          |

|-------------------------|------|----------------|--------------------------------------------------------------------------------------------------------------------------------------|

| TClk<br>F24             | I    | Internal Clock | The GT–64242 units internal clock (up to 100MHz). Used as input clock to the internal PLL.                                           |

| AVCC<br>H25             | I    | PLL Vcc        | Quiet power supply to the internal PLL.  NOTE: For information on the PLL, see Section 22.4  "PLL Power Filter Circuit" on page 324. |

| AGND<br>G25             | I    | PLL Vss        | Quiet ground supply to the internal PLL.                                                                                             |

| Core Clock Pin Count: 3 |      |                | .2                                                                                                                                   |

## Table 3: CPU Interface Pin Assignments

| Pin Name/<br>Ball # | Type    | Full Name                     | Description                                                                                                                                                                                                                                                                |

|---------------------|---------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SysClk<br>E25       | ı       | System Clock                  | CPU interface clock (up to 100 MHz).  Can run at any frequency less than or equal to the TClk frequency asynchronously.  The CPU interface can be configured to run with TClk instead of SysClk.  NOTE: In this configuration, SysClk is not used and must be tied to GND. |

| SysRst*<br>D25      | e JK    | System Reset                  | Main reset signal of the GT–64242.  Resets all units to their initial state.  NOTE: When in the reset state, all output pins, except for SDRAM address and control signals, are put into tristate.                                                                         |

| SysAD[63:0]         | t/s I/O | System<br>Address/Data<br>Bus | 64-bit multiplexed CPU address/data bus.  Driven by the CPU during address phase and write data phase.  Driven by GT–64242 during read response data phase.                                                                                                                |

[63:54] AC27, AC28, U27, AC29, V30, V29, L29, L30, Y31, P30

[53:44] AD26, P29, AC30, R30, AD27, AA30, AA31, V31, AA28, U28

[43:34] W27, R31, W28, AD28, W29, AD29, P31, AB27, AB28, AD30

[33:24] W30, T26, M26, R27, N28, N27, T27, L31, U30, M31

[23:14] Y27, M30, P28, Y29, V27, P27, T30, AC26, V26, AA27

[13:0] AC31, T31, V28, Y30, AA29, U31, R29, AB31, Y28, N31, T28, AB29, W31, AD31

Table 3: CPU Interface Pin Assignments (Continued)

| Pin Name/<br>Ball #                                              | Type    | Full Name                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------|---------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SysADC[7:0]<br>L28, R28, M28,<br>AB30, M29, N30,<br>U29, T29     | t/s I/O | System<br>Address/Data<br>Parity Bus       | 8-bit parity for the SysAD bus. Driven by CPU during write data phase. Driven by GT–64242 during read response data phase.  NOTE: – SysADC is valid on data cycles only.  — If not using CPU parity, a pull-up is required.                                                                                                                                                                                                                                                       |

| SysCmd[8:0]<br>G26, G27, G29, F28,<br>F29, F30, F31, F26,<br>E31 | t/s I/O | System Com-<br>mand/Data<br>Identifier Bus | 9-bit multiplexed CPU command/data identifier bus.  System Command driven by the CPU during address phase.  Data identifier driven by the CPU during write data phase and by the GT–64242 during read response data phase.                                                                                                                                                                                                                                                        |

| ValidOut*<br>D31                                                 | I       | Valid Output                               | The CPU signals that it is driving valid address/data on the SysAD bus and valid command/data identifier on the SysCmd bus.                                                                                                                                                                                                                                                                                                                                                       |

| Release*<br>E27                                                  | I       | Release                                    | The CPU signals that it has released the SysAD and the SysCmd buses after completion of a read request.                                                                                                                                                                                                                                                                                                                                                                           |

| ValidIn*<br>C31                                                  | t/s O   | Valid Input                                | The GT–64242 signals that it is driving valid read data on the SysAD bus and a valid data identifier on the SysCmd bus.  NOTE: In multi-GT mode, acts as s/t/s pin.                                                                                                                                                                                                                                                                                                               |

| SysRdyOut*<br>A29                                                | t/s O   | Read/Write<br>Ready Output                 | The GT–64242 signals that it can accept a CPU read or write request.  NOTE: Must be connected to both RdRdy* and WrRdy* CPU input pins.  In multi-GT–64242 configurations, SysRdyOut*, of the boot GT–64242, is connected to the CPU RdRdy* and WrRdy* inputs. The SysRdyOut* outputs, of the other GT–64242 devices, are connected to SysRdyIn[2:0] of the boot GT–64242 device.                                                                                                 |

| SysRdyIn[2:0]*<br>H27, H30, H31                                  | I       | Read/Write<br>Ready Input                  | NOTE: Relevant only in multi-GT–64242 configurations. In a single GT configuration, connect to GND.  SysRdyIn of the boot GT–64242 device is connected to SysRdyOut of all other GT–64242 devices.  • SysRdyIn[0]* of all the GT–64242 devices, except for the boot device, are connected to the boot GT–64242 device's SysRdyOut* signal, which is also the CPU RdRdy* and WrRdy* input.  • SysRdyIn[2:1]* of all the GT–64242 devices, except of the boot device, are not used. |

**CPU Interface Pin Assignments (Continued)** Table 3:

| r                           |       |                                            | ·                                                                                                                                                                                        |

|-----------------------------|-------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name/<br>Ball #         | Type  | Full Name                                  | Description                                                                                                                                                                              |

| PReq*<br>A26                | I     | Processor<br>Request                       | CPU requests from the GT–64242 for SysAD bus mastership.  NOTE: If interfacing with a CPU that does not support Preq*, pull up is required on this pin.                                  |

| PAck*<br>C25                | t/s O | Processor<br>Acknowledge                   | The GT–64242 signals that it releases the SysAD bus in response to PReq*.  NOTE: In multi-GT mode, acts as s/t/s pin.                                                                    |

| RspSwap*<br>E26             | t/s O | Read<br>Response<br>Swap                   | The GT–64242 signals that it is returning read data to the CPU out of order.  NOTE: In a multi-GT configuration, RspSwap* is NC.                                                         |

| CPUInt*<br>C25              | t/s O | Interrupt                                  | Level sensitive interrupt driven by the GT–64242 to the CPU. There are four more optional CPU interrupt pins multiplexed on the GPP pins.                                                |

| TcTCE*<br>G30               | I     | Ternary Cache<br>Tag RAM Chip<br>Enable    | The CPU L3 cache controller signals that it is accessing L3 cache.  NOTE: If interfacing with a CPU that does not support-TcTCE*, pull up is required on this pin.                       |

| TcDOE*<br>H26               | t/s O | Ternary Cache<br>Data RAM<br>Output Enable | In case of a cache hit, the GT–64242 enables L3 data RAM drive read data on SysAD.  NOTE: In a multi-GT configuration, acts as s/t/s pin.                                                |

| TcWord[1:0]<br>E28, E29     | t/s O | Ternary Cache<br>Word Index                | Determines correct L3 double-word index.  Driven by the GT–64242 in case of a CPU block read miss (driven by CPU L3 cache controller in case of L3 hit).  NOTE: A pull-down is required. |

| TcMatch<br>C29              | S.    | Ternary Cache<br>Tag Match                 | Asserted by tag RAMon L3 cache tag match.  NOTE: If there is no L3 cache, or when working in SimpleCache mode, connect the TcMatch input to GND.                                         |

| CPU Interface Pin Count: 97 |       |                                            |                                                                                                                                                                                          |

## Table 4: PCI Bus Interface Pin Assignments

| Pin Name/<br>Ball # | Type | Full Name | Description                                                                                                                                           |

|---------------------|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clk<br>AH16         | I    | PCI Clock | The PCI clock range is between 0 and 66MHz. PClk0 is completely independent of SysClk and TClk.                                                       |

| Rst*<br>AJ16        | I    | PCI Reset | Dedicated reset signal for PCI interface.  When in the reset state, all PCI output pins are put into tristate and all open drain signals are floated. |

Table 4: PCI Bus Interface Pin Assignments (Continued)

|                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 | ·                                                                                                                                                                                                                                                                                                                                           |  |

|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name/<br>Ball #                                                                              | Type                                                                                                                                                                                                                                                                                                                                                                                                                                     | Full Name                       | Description                                                                                                                                                                                                                                                                                                                                 |  |

| VREF<br>AF17                                                                                     | I                                                                                                                                                                                                                                                                                                                                                                                                                                        | PCI Voltage<br>Reference        | This pin must be connected directly to the 3.3V or the 5V power plane depending on which voltage level PCI supports.                                                                                                                                                                                                                        |  |

| PAD[63:0]                                                                                        | t/s I/O                                                                                                                                                                                                                                                                                                                                                                                                                                  | PCI Address/<br>Data            | -bit PCI multiplexed address/data bus.  Driven by the transaction master during address phase and write data phase.  Driven by the target device during read data phase.  NOTE: If configured with a 64-bit PCI, PAD[63:32] requires a pull-up. When configured as a 32-bit bus, the GT–64242 drives these pins; a pull-up is not required. |  |

| [53:44] AK29, AJ29, A<br>[43:32] AG28, AF31, A<br>[31:24] AL17, AK17, A<br>[23:14] AL19, AK19, A | [63:54] AL27, AK27, AJ27, AH27, AG27, AL28, AK28, AJ28, AH28, AL29 [53:44] AK29, AJ29, AJ30, AJ31, AH31, AH30, AH29, AG31, AG30, AG29 [43:32] AG28, AF31, AF30, AF29, AF28, AF27, AE31, AE30, AE29, AE28, AE27, AE26 [31:24] AL17, AK17, AJ17, AH17, AG17, AL18, AK18, AJ18 [23:14] AL19, AK19, AJ19, AH19, AG19, AL20, AK20, AJ20, AJ22, AH22 [13:0] AG22, AF22, AL23, AK23, AJ23, AH23, AF23, AL24, AK24, AJ24, AH24, AG24, AF24, AL25 |                                 |                                                                                                                                                                                                                                                                                                                                             |  |

| CBE[7:0]* AL26, AK26, AJ26, AG26, AH18, AH20, AK22, AG23                                         | t/s I/O                                                                                                                                                                                                                                                                                                                                                                                                                                  | PCI Com-<br>mand/Byte<br>Enable | 8-bit multiplexed command/byte-enable bus, driven by transaction master.  Contains command during the address phase and byte-enable during data phase.  NOTE: If configured with a 64-bit PCI, CBE[7:4] requires a pull-up. When configured as a 32-bit bus, the GT–64242 drives these pins; a pull-up is not required.                     |  |

| PAR<br>AL22                                                                                      | t/s I/O                                                                                                                                                                                                                                                                                                                                                                                                                                  | PCI Parity<br>(low)             | Even parity calculated for PAD[31:0] and CBE[3:0].  Driven by transaction master for address phase and write data phase.  Driven by target for read data phase.                                                                                                                                                                             |  |

| FRAME*<br>AG20                                                                                   | s/t/s<br>I/O                                                                                                                                                                                                                                                                                                                                                                                                                             | PCI Frame                       | Asserted by the transaction master to indicate the beginning of a transaction.  The master de-asserts FRAME* to indicate that the next data phase is the final data phase transaction.                                                                                                                                                      |  |

| IRDY*<br>AF20                                                                                    | s/t/s<br>I/O                                                                                                                                                                                                                                                                                                                                                                                                                             | PCI Initiator<br>Ready          | Asserted by the transaction master to indicate it is ready to complete the current data phase of the transaction. A data phase is completed when TRDY* and IRDY* are asserted.                                                                                                                                                              |  |

PCI Bus Interface Pin Assignments (Continued) Table 4:

| Pin Name/       |              |                                          |                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|--------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ball #          | Type         | Full Name                                | Description                                                                                                                                                                                                                                                                                                                                        |

| DEVSEL*<br>AK21 | s/t/s<br>I/O | PCI Device<br>Select                     | Asserted by the target of the current access.  As a master, the GT–64242 expects the target to assert DEVSEL* within five bus cycles. If the target does not assert DEVSEL* within the required bus cycles, the GT–64242 aborts the cycle.  As a target, the GT–64242 asserts DEVSEL* in a medium speed; two cycles after the assertion of FRAME*. |

| TRDY*<br>AL21   | s/t/s<br>I/O | PCI Target<br>Ready                      | Asserted by the target to indicate it is ready to complete the current data phase of the transaction. A data phase is completed when when TRDY* and IRDY* are asserted.                                                                                                                                                                            |

| STOP*<br>AJ21   | s/t/s<br>I/O | PCI Stop                                 | Asserted by target to indicate transaction termination.  Used by a target device to generate a Retry, Disconnect, or Target Abort termination signal.                                                                                                                                                                                              |

| IDSEL<br>AG18   | I            | PCI Initializa-<br>tion Device<br>Select | Asserted to act as a target device chip select during PCI configuration transactions.                                                                                                                                                                                                                                                              |

| REQ64*<br>AJ25  | s/t/s<br>I/O | PCI Request<br>64-bit Transfer           | Asserted by the transaction master to indicate a request of a 64-bit bus width transaction.  REQ64* timing is the same as FRAME* timing.  NOTE: A 64-bit transaction occurs when REQ64* and ACK64* are asserted.                                                                                                                                   |

| ACK64*<br>AK25  | s/t/s<br>I/O | PCI Acknowl-<br>edge 64-bit<br>Transfer  | Asserted by the target in response to REQ64* to indicate it accepts a 64-bit bus width transaction.  ACK64* timing is the same as DEVSEL* timing.  NOTE: A 64-bit transaction occurs when REQ64* and ACK64* are asserted.                                                                                                                          |

| PAR64<br>AF26   | t/s I/O      | PCI Parity<br>(high)                     | In cases of a 64-bit PCI transaction, even parity is calculated for PAD[63:32] and CBE[7:4].  Driven by the transaction master for address phase and write data phase.  Driven by the target for read data phase.  NOTE: A pull-up is required. When configured as a 32-bit bus, the GT–64242 drives this pin; a pull-up is not required.          |

| REQ*<br>AF16    | t/s O        | PCI Bus<br>Request                       | If using an external PCI arbiter, asserted by the GT–64242 PCI master to indicate it requires PCI bus mastership to initiate a new transaction.  If using the internal PCI arbiter, leave unconnected.                                                                                                                                             |

Table 4: PCI Bus Interface Pin Assignments (Continued)

| Pin Name/              |              |                                                 |                                                                                                                                                                                                                                                                                                       |

|------------------------|--------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ball #                 | Type         | Full Name                                       | Description                                                                                                                                                                                                                                                                                           |

| GNT*<br>AG16           | I            | PCI Bus Grant                                   | If using an external PCI arbiter, asserted to indicates to the GT–64242 PCI master that bus mastership is granted.  NOTES: – The PCI master drives the bus only when it's GNT* signal is asserted and the bus is in idle state.  – If using the GT–64242 internal PCI arbiter, a pull-up is required. |

| PERR*                  |              | PCI Parity                                      | Asserted when a data parity error is detected.                                                                                                                                                                                                                                                        |

| AH21                   | s/t/s<br>I/O | Error                                           | Asserted by a target device in response to bad address or write data parity, or by master device in response to bad read data parity.                                                                                                                                                                 |