Version: 1.0

## Preliminary

May 30, 2002

#### © Copyright International Business Machines Corporation 2002

All Rights Reserved Printed in the United States of America May 2002

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both

| IBM Logo       |

|----------------|

| PowerPC Logo   |

| PowerPC 750    |

| PowerPC 750CXe |

|                |

|                |

Other company, product and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in implantation or other life support, space, nuclear, or military applications where malfunction may result in injury or death to persons. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

**Note:** This document contains information on products in the sampling and/or initial production phases of development. This information is subject to change without notice. Verify with your IBM field applications engineer that you have the latest version of this document before finalizing a design.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Microelectronics Division 1580 Route 52, Bldg. 504 Hopewell Junction, NY 12533-6351

The IBM home page can be found at <a href="http://www.ibm.com">http://www.ibm.com</a>

The IBM Microelectronics Division home page can be found at <a href="http://www.chips.ibm.com">http://www.chips.ibm.com</a>

Title\_750FX\_Tech\_Sum.fm.1.0 May 30, 2002

## Contents

| List of Tables                                                          | 7    |

|-------------------------------------------------------------------------|------|

| List of Figures                                                         | 9    |

| 1. IBM PowerPC <sup>®</sup> 750FX Technical Summary<br>1.1 Introduction |      |

| 2. Features                                                             | 12   |

| 3. Summary of Enhancements                                              | 15   |

| 3.1 Performance                                                         | . 15 |

| 3.1.1 L2 Cache                                                          | . 15 |

| 3.1.2 L1 Data Cache                                                     | . 15 |

| 3.1.3 Bus Pipelining                                                    |      |

| 3.1.4 Floating Point Unit Reservation Station                           | . 16 |

| 3.2 Power                                                               | . 16 |

| 3.3 Reliability                                                         | . 17 |

| 3.4 Pin Interfaces                                                      | . 17 |

| 3.4.1 60x Interface                                                     |      |

| 3.4.2 Configuration and Power Pins                                      | . 17 |

|                                                                         | 4.0  |

| 4. The 750FX Functional Units                                           |      |

| 4.1 Principles of Operation                                             |      |

| 4.2 Control Unit                                                        | . 19 |

| 4.3 Instruction Fetch                                                   | . 19 |

| 4.4 Branch Processing                                                   | . 19 |

| 4.5 Instruction Dispatch                                                | . 20 |

| 4.6 Instruction Completion                                              | . 20 |

| 4.7 Interrupt Handling                                                  | . 21 |

| 4.8 System Execution Unit                                               | . 21 |

| 4.9 Data Execution Units                                                | . 21 |

| 4.10 Load / Store Unit                                                  | . 21 |

| 4.11 Caches                                                             |      |

| 4.11.1 750FX Level 1 Cache Description                                  |      |

| 4.11.1.1 Coherency Support                                              |      |

| 4.11.1.2 Cache Loads                                                    |      |

| 4.11.1.3 Cache Replacements                                             |      |

| 4.11.2 750FX Level 2 Cache Features.                                    | . 23 |

| 4.12 Bus Interface Unit                                                 | . 23 |

| 5. PowerPC 750FX Microprocessor Implementation                          | 24   |

| 6. PowerPC Registers and Programming Model                              | 25   |

| 7. Instruction Set                                                                  |    |

|-------------------------------------------------------------------------------------|----|

| 8. On-Chip Cache Implementation                                                     | 29 |

| 8.1 PowerPC Cache Model                                                             |    |

| 8.2 PowerPC 750FX Microprocessor Cache Implementation                               |    |

| 8.2.1 Description of 750FX L1 Caches                                                |    |

| 8.2.2 Description of 750FX L2 Cache                                                 |    |

| 8.2.2.1 L2 Cache Operation                                                          |    |

|                                                                                     |    |

| 9. Exception Model                                                                  |    |

| 9.1 PowerPC Exception Model                                                         |    |

| 9.2 PowerPC 750FX Microprocessor Exception Implementation                           |    |

| 9.2 PowerPC 750FX Microprocessor Exception implementation                           | JZ |

| 10. Memory Management                                                               | 34 |

| 10.1 PowerPC Memory Management Model                                                |    |

|                                                                                     |    |

| 10.2 PowerPC 750FX Microprocessor Memory Management Implementation                  | 35 |

| 11. Instruction Timing                                                              | 26 |

|                                                                                     |    |

| 12. Power Management                                                                | 30 |

| 12.1 Full On                                                                        |    |

|                                                                                     |    |

| 12.2 Doze                                                                           |    |

| 12.3 Nap                                                                            |    |

| 12.4 Sleep                                                                          | 40 |

| 13. Thermal Management                                                              | 11 |

|                                                                                     |    |

| 14. Performance Monitor                                                             | 12 |

|                                                                                     | 42 |

| 15. PowerPC Architecture™ Compliance                                                | 12 |

| •                                                                                   |    |

| 15.1 Implementation-Specific MSR-bits for 750FX                                     |    |

| 15.1.1 Machine State Register<br>15.1.2 Implementation-Specific SRR1 bits for 750FX |    |

| 15.1.3 Processor Version Register                                                   |    |

| 15.1.4 Implementation-Specific SPRs                                                 |    |

| 15.1.5 Hardware Implementation Dependent Register 0 (HID0) Bit Functions            |    |

| 15.1.6 Hardware Implementation Dependent Register 1 (HID) Bit Functions             |    |

| 15.1.7 Hardware Implementation Dependent Register 2 (HID2) Bit Functions            |    |

| 15.1.8 Illegal and Invalid SPR Operations                                           |    |

| 15.1.9 TLB and BAT Software Reset Requirement                                       |    |

| ·                                                                                   |    |

| 15.2 Exceptions<br>15.2.1 Machine Check Exception                                   |    |

| 15.2.1 Machine Check Exception                                                      |    |

| 15.2.2 System Management Exception                                                  |    |

| 15.2.4 External Exception                                                           |    |

| 15.2.5 Thermal Management Exception                                                 |    |

|                                                                                     |    |

| 15.2.6 Alignment Exception                                       | 52 |

|------------------------------------------------------------------|----|

| 15.2.7 Data Storage Exception                                    |    |

| 15.2.8 Implementation-Specific Exception Vector Offsets          | 52 |

| 15.2.9 Trace Exception                                           | 53 |

| 15.2.10 Instruction Address Breakpoint Exception                 |    |

| 15.2.11 Data Address Breakpoint Exception                        | 53 |

| 15.2.12 Soft Stops                                               |    |

| 15.2.13 Performance Monitor Exception                            |    |

| 15.2.14 Floating Point Assist Exception                          | 54 |

| 15.2.15 Floating Point Unavailable                               | 54 |

| 15.2.16 Program Exception                                        | 54 |

| 15.2.17 System Call Exception                                    |    |

| 15.2.18 Instruction Storage Exception                            | 54 |

| 15.2.19 Decrementer Exception                                    | 55 |

| 15.2.20 Exception Latencies                                      |    |

| 15.2.21 Exception Priorities                                     |    |

| 15.2.22 Summary of Front-End Exception Handling                  | 56 |

| 15.3 THRM1, THRM2, THRM3 Bit Field Settings                      | 57 |

| 15.4 Synchronization Requirements for SPRs and Segment Registers |    |

|                                                                  |    |

| Revision Log                                                     | 61 |

## List of Tables

| Table 2-1. Instructions                                                               | 12 |

|---------------------------------------------------------------------------------------|----|

| Table 3-1. I/O Voltage Selection Settings                                             | 17 |

| Table 9-1. PowerPC 750FX Microprocessor Exception Classifications                     | 32 |

| Table 9-2. Exceptions and Conditions                                                  | 32 |

| Table 15-1. Machine State Register 750FX-Specific Bits                                | 45 |

| Table 15-2. SRR1 750FX-Specific Bits for Machine Check                                | 45 |

| Table 15-3. 750FX Implementation-Specific SPRs                                        | 45 |

| Table 15-4. HID0 Bit Functions                                                        |    |

| Table 15-5. HID1 Bit Functions                                                        | 48 |

| Table 15-6. HID2 Bit Definitions                                                      | 49 |

| Table 15-7. Sources and Priorities of Externally-Generated Exceptions                 | 51 |

| Table 15-8. 750FX Implementation-Specific Exception Vector Offsets                    | 53 |

| Table 15-9. 750FX Exception Priorities                                                | 55 |

| Table 15-10. THRM1 and THRM2 SPR Bit Field Settings                                   | 57 |

| Table 15-11. THRM3 Bit Field SPR Settings                                             | 58 |

| Table 15-12. Instructions and Registers Requiring a Context-Synchronization Operation | 58 |

|                                                                                       |    |

# List of Figures

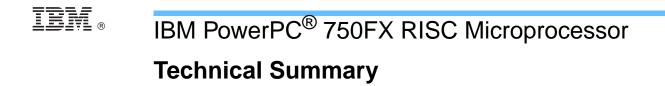

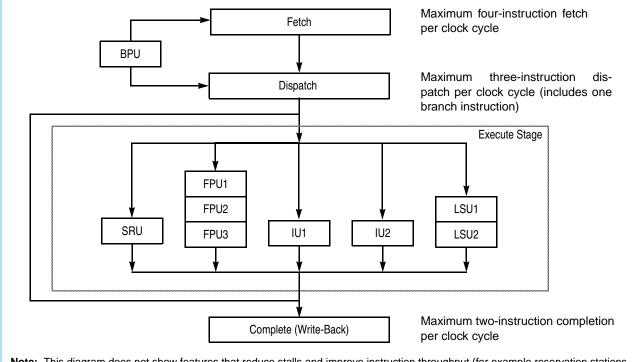

| Figure 4-1. 750FX Block Diagram                                        | 19 |

|------------------------------------------------------------------------|----|

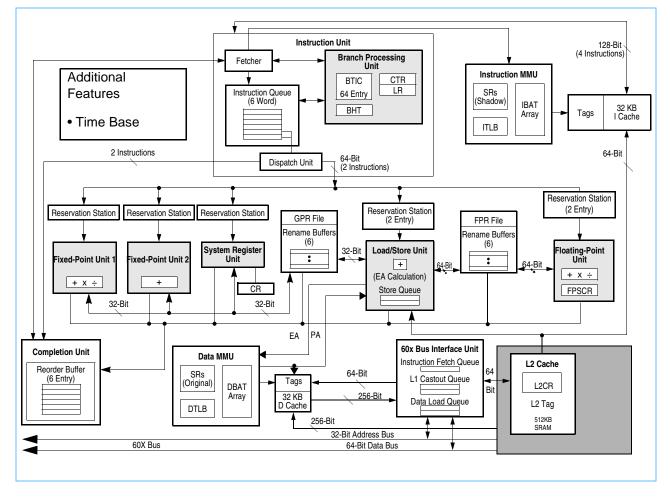

| Figure 4-2. Completion Buffer Queue Block Diagram                      | 20 |

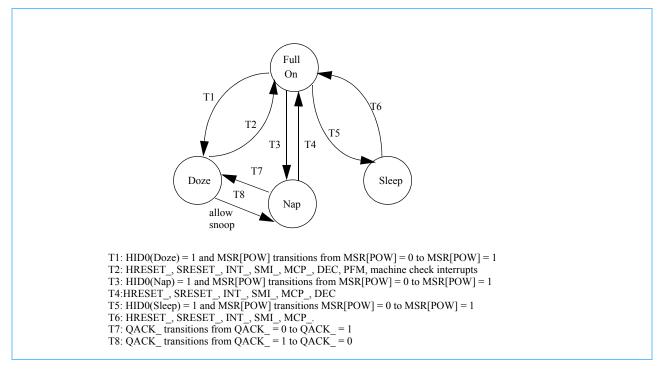

| Figure 6-1. PowerPC 750FX Microprocessor Programming Model — Registers | 26 |

| Figure 11-1. Pipeline Diagram                                          | 36 |

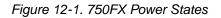

| Figure 12-1. 750FX Power States                                        | 39 |

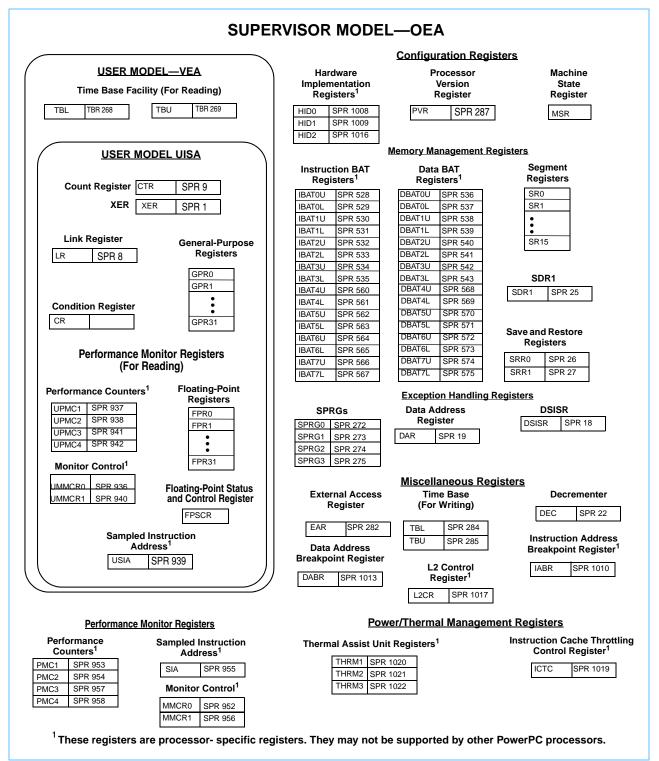

| Figure 15-1. PowerPC 750FX Microprocessor Programming Model—Registers  | 44 |

| Figure 15-2. IABR Register Diagram                                     | 53 |

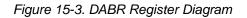

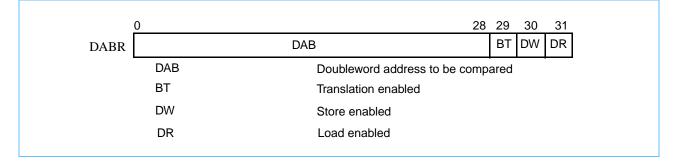

| Figure 15-3. DABR Register Diagram                                     | 54 |

# **1. IBM PowerPC<sup>®</sup> 750FX Technical Summary**

The IBM PowerPC<sup>®</sup> 750FX RISC microprocessor is an implementation of the PowerPC Architecture<sup>™</sup> with enhancements based on the IBM PowerPC 750<sup>™</sup> and 750CXe<sup>™</sup> RISC microprocessor designs. This section provides an overview of the PowerPC 750FX microprocessor features, including a block diagram showing the major functional components. It also provides information about how PowerPC 750FX implementation complies with the PowerPC Architecture definition.

Note: In this document PowerPC 750FX RISC Microprocessor is abbreviated as PowerPC 750FX or 750FX.

### **1.1 Introduction**

The 750FX processor is a 32-bit implementation of the PowerPC Architecture in a 0.13 micron CMOS technology with six levels of copper interconnect. The 750FX is designed for high performance (up to 1GHz) and low power consumption. It provides a super set of functionality to the PowerPC 750 processor, including a complete 60x bus interface, and enhancements such as an onboard 512KB L2 cache.

## 2. Features

The following is a brief list of some of the key features of the 750FX processor:

- Implements full PowerPC 32-bit architecture

- Four (4) stage Pipeline control

- Fetch

- Dispatch and decode

- Execute

- Complete/Write back

- Dual Issue superscalar control

- A maximum of two instructions completed plus one branch folded per cycle

- Two instructions dispatched in one of the combinations shown in Table 2-1

#### Table 2-1. Instructions

| inst0 \ inst1 | fxu1 | fxu2 | lsu | fpu | sysu |

|---------------|------|------|-----|-----|------|

| fxu1          |      | Х    | Х   | Х   | Х    |

| fxu2          | Х    |      | Х   | Х   | Х    |

| lsu           | Х    | Х    |     | Х   | Х    |

| fpu           | Х    | Х    | Х   |     | Х    |

| sysu          | Х    | Х    | Х   | Х   |      |

- Branch folding

- Buffers for architectural registers to support fast speculation correction

- Precise interrupt handling

- Branch processing unit

- Four instructions fetched per clock

- One branch processed per cycle (plus resolving two speculations)

- Up to one speculative stream in execution, one additional speculative stream in fetch

- 512-entry branch history table (BHT) for dynamic prediction

- 64-entry, 4-way set associative branch target instruction cache (BTIC) for eliminating branch delay slots

- Dispatch unit

- Full hardware detection of dependencies (resolved in the execution units)

- Dispatch two instructions to six independent units (system, branch, load/store, fixed-point unit 1, fixed-point unit 2, or floating-point)

- 4-stage pipeline: fetch, dispatch, execute, and complete

- Serialization control (predispatch, postdispatch, execution, serialization)

- Decode

- Register file access

- Forwarding control

- Partial instruction decode

- Load/store unit

- One cycle load or store cache access (byte, half-word, word, double-word)

- Effective address generation

- Non-blocking cache (up to two outstanding misses)

- Single-cycle misaligned access within double word boundary

- Alignment, zero padding, sign extend for integer register file

- Floating-point internal format conversion (alignment, normalization)

- Sequencing for load/store multiples and string operations

- Store gathering

- Cache and TLB instructions

- Big- and little-endian byte addressing supported

- Misaligned little-endian support in hardware

- Fixed-point units

- Fixed-point unit 1 (FXU1): multiply, divide, shift, rotate, arithmetic, logical

- Fixed-point unit 2 (FXU2): shift, rotate, arithmetic, logical

- Single-cycle arithmetic, shift, rotate, logical

- Multiply and divide support (multi-cycle)

- Early out multiply

- Thirty-two, 32-bit general purpose registers

- Floating-point unit

- Support for IEEE-754 standard single and double-precision floating-point arithmetic

- Optimized for single-precision multiply/add

- Thirty-two, 64-bit floating point registers

- Enhanced reciprocal estimates

- 3-cycle latency, 1-cycle throughput, single-precision multiply-add

- 3-cycle latency, 1-cycle throughput, double-precision add

- 4-cycle latency, 2-cycle throughput, double-precision multiply-add

- Hardware support for divide

- Hardware support for denormalized numbers

- Time deterministic non-IEEE mode

- System unit

- Executes CR logical instructions and miscellaneous system instructions

- Special register transfer instructions

- L1 Cache structure

- 32KB, 32-byte line, 8-way set associative instruction cache

- 32KB, 32-byte line, 8-way set associative data cache

- Single-cycle cache access

- Pseudo-LRU replacement

- Copy-back or write-through data cache (on a page per page basis)

- 3-state (MEI) memory coherency

- Hardware support for data coherency

- Non-blocking instruction cache (one outstanding miss)

- Non-blocking data cache (two outstanding misses)<sup>1</sup>

- No snooping of instruction cache

- Parity added for L1 tags and caches<sup>1</sup>

<sup>1.</sup> Not supported under DD 1.X.

- Memory management unit

- 128 entry, two way set associative instruction (data) TLB

- Hardware reload for TLB's

- 8 instruction BATs and 8 data BATs

- Virtual memory support for up to 4 exabytes (2<sup>52</sup>) virtual memory

- Real memory support for up to 4 gigabytes  $(2^{32})$  of physical memory

- Level 2 (L2) cache

- 512KB, two-way set associative unified L2 cache

- Copy-back or write-through data cache on a page basis, or for all L2

- 64-byte line size, two sectors per line

- L2 frequency at core speed

- On-board ECC<sup>1</sup>

- Parity added for L2 tags

- Supports up to 2 outstanding misses (1 data and 1 instruction)

- Supports up to 2 outstanding misses (2 data)<sup>1</sup>

- Cache locking by way<sup>1</sup>

- Bus interface

- Compatible with 60x

- 32-bit address bus

- 64-bit data bus (or 32-bit mode)

- Enhanced 60x bus: pipelines back-to-back reads to a depth of 2

- Core-to-bus frequency multipliers of 2x, 2.5x, 3x, 3.5x, 4x, 4.5x, 5x, 5.5x, 6x, 6.5x, 7x, 7.5x, 8x, 8.5x, 9x, 9.5x, 10x, 11x, 12x, 13x, 14x, 15x, 16x, 17x, 18x, 19x, and 20x supported

- Power

- Dual PLLs for seamless frequency switching

- 3 static power saving modes: doze, nap, and sleep

- Dynamic power management (DPM)<sup>1</sup>

- · Reliability and serviceability

- Parity checking on 60x busses

- Parity checking on internal arrays<sup>1</sup>

- ECC checking on L2 cache

- Parity on the L1 arrays<sup>1</sup>

- Parity on the L1 and L2 tags<sup>1</sup>

- Testability

- LSSD scan design for high percentage stuck-fault test coverage

- AC LSSD scan design for signal transition fault coverage

- Programmable array built-in self test for complete test coverage of large arrays

- Powerful diagnostic and test interface through Common On-Chip Processor (COP) and IEEE 1149.1 (JTAG) interface

<sup>1.</sup> Not supported under DD 1.X.

## 3. Summary of Enhancements

This section provides a summary of the major enhancements for the PowerPC 750.

### 3.1 Performance

The performance enhancements included in the 750FX microprocessor are:

- Up to 1GHz operating frequency

- 512KB on-board L2 cache with locking by way<sup>1</sup>

- L1 data cache availability improvements

- Bus pipelining (consecutive data reads)

- Additional floating point unit (FPU) reservation station and improved reciprocal estimates

- Eight (8) data BATs and instruction BATs

#### 3.1.1 L2 Cache

The 750FX has an internal L2 cache capacity of 512KB. The cache is two-way set associative; each way contains 4096 blocks and each block consists of two 32-byte sectors. Array read and write operations execute in one processor cycle. Writes to the array are 64 bits wide, while reads are 256 bits wide.

In addition, the L2 cache has an 8-bit ECC for every 64-bit word in memory that can be used to correct a majority of single bit errors and detect multiple bit errors.

The L2 tags also support parity and locking by way.<sup>1</sup>

#### 3.1.2 L1 Data Cache

The 750FX L1 data cache supports miss-under-miss access, meaning that with one miss outstanding, the cache can continue to be accessed until a second miss occurs. Additionally, the 750FX L1 data cache allows the second miss to initiate a transaction in the bus interface unit, while the first miss is pending<sup>1</sup>.

In previous PowerPC 750 microprocessor implementations the data bus width for bus interface unit (BIU) accesses of the L1 data cache array was 64 bits. To cast out or to reload a 256-bit cache line required four access cycles. On the 750FX, this bus has been expanded to 256 bits. As a result, cache line data bursts can be read from or written to the cache array in a single cycle, reducing cache contention between the BIU and the load-store unit.

#### 3.1.3 Bus Pipelining

The 60x bus has decoupled address and data busses, allowing transactions to be pipelined on the bus. That is, the address operation for a second transaction can be initiated before the data operation for a previous transaction is complete. The 750FX BIU allows pipelined read transactions to a depth of two back-to-back reads.

<sup>1.</sup> Not supported under DD 1.X.

#### 3.1.4 Floating Point Unit Reservation Station

The floating point unit (FPU) consists of a three-stage pipeline. Formerly, there was a restriction that if the pipeline was full with three (3) floating point instructions, a single cycle stall would occur before a new instruction could be loaded into the floating point unit. The 750FX has added a second reservation station so the floating point unit can now accept a floating point instruction every cycle.

### 3.2 Power

The 750FX design includes two PLLs (PLL0 and PLL1), allowing the processor clock frequency to be changed on-the-fly to match processing requirements.

During reset PLL0 is selected to provide the internal processor (i.e. core) clock. The external clock to core clock multiplier is selected using external pins. Thereafter, PLL0 and PLL1 may be controlled using software. The HID1 register contains fields that specify the frequency range of each PLL, the clock multiplier for each PLL, external or internal control of PLL0, and a bit to choose which PLL is selected as the source of the processor clock at any given time.

### 3.3 Reliability

Parity is implemented for the following arrays: I-Cache, I-Tag, D-Cache, D-Tag, and L2 Tag. Parity errors will result in a machine check interrupt which is not recoverable.<sup>1</sup>

### 3.4 Pin Interfaces

#### 3.4.1 60x Interface

The 750FX processor defines a versatile bus interface which allows for a wide range of system performance versus system complexity trade-offs to be exploited. The interface defines a 72-bit data bus (64 bits of data and 8 bits of parity), a 36-bit address bus (32 bits of address and 4 bits of parity) along with sufficient control signals to allow for unique system level optimizations. The interface allows for address-only transactions as well as address and data transactions. The 750FX initiates an address-only transaction for a **dcbz** cache control instruction, but can be configured (via HID0) to initiate address-only transactions for other data cache control instructions, **eieio**, and **sync**. The **dcbz** is the only address-only transaction that is snooped by the 750FX. The 750FX will generate or accept either one beat or four beat data transactions, although it is possible for other bus participants to perform longer data transfers.

In addition, the 750FX processor supports cache snooping. The bus interface defines the signals required to build systems which require a coherent memory system. It is envisioned that a wide range of system implementations can be constructed from the defined interface.

#### 3.4.2 Configuration and Power Pins

Signals introduced in the 750FX design include PLL\_CFG[4] and PLL\_RNG[0:1]. PLL\_CFG[4] provides an additional PLL configuration bit to support additional processor to bus clock frequency ratios. PLL\_RNG[0:1] are used to select a frequency range for the processor clock. This allows a wider range of frequencies to be supported by the PLLs. In addition, a second analog voltage pin, AVdd1, has been added to power the second PLL.

I/O voltage is selectable through using the BVSEL pin and L1\_TSTCLK pin.

| Table 3-1. I/O | Voltage Selection | Settings |

|----------------|-------------------|----------|

|----------------|-------------------|----------|

| Voltage Selection | Bvsel | L1tstclk<br>(Second Vsel Signal) |

|-------------------|-------|----------------------------------|

| Reserved          | 0     | 0                                |

| 1.2, 1.5, or 1.8V | 0     | 1                                |

| 2.5V              | 1     | 1                                |

| 3.3V              | 1     | 0                                |

<sup>1.</sup> Not support under DD 1.X.

## 4. The 750FX Functional Units

This section presents a brief overview and high-level block diagrams of each functional unit of the processor. The 750FX processor is partitioned into the following subsystems:

- Control Unit

- · Fixed Point and Floating Point Units

- Load/Store Unit

- Cache and Memory Management Unit

- Bus Interface Unit

## 4.1 Principles of Operation

The block diagram of the 750FX is shown in *Figure 4-1 on page 19*. The instruction fetch unit prefetches instructions from the instruction cache into the instruction buffers. The branch unit identifies any branch instructions in the instruction buffers and folds them out if possible.

The dispatcher decodes the two instructions from the instruction buffer and decides whether they can be dispatched. The dispatcher also reads the operands from the register files. If any operand is not yet available for any reason, the dispatcher supplies a rename tag for that operand. The dispatched instructions are placed on the instruction dispatch busses along with their execution unit assignment and rename register assignment for destination results.

The execution units store the operands/tags that have been assigned to them from the dispatch busses. When all operands are available, the instruction is executed.

The execution unit writes the result of a finished instruction on the proper rename bus and into the rename register.

The completion logic retires an instruction when all instructions ahead of it have been retired and the instruction has finished execution. Retirement will write the instruction's result into the proper architectural register and remove it from the rename buffers. It also updates any other machine state that is affected by this instruction. Up to two instructions can be simultaneously retired.

## 4.2 Control Unit

This section describes the control unit of the 750FX. The control unit contains the instruction fetch unit, branch unit, instruction dispatch unit, completion unit, interrupt handling logic, and the system execution unit.

## 4.3 Instruction Fetch

The instruction fetch unit controls the flow of instructions from the cache to the instruction buffers and dispatch buffer.

## 4.4 Branch Processing

The branch unit executes branch instructions, predicts conditional branches and provides addresses for instruction fetches.

### 4.5 Instruction Dispatch

The dispatch unit includes the dispatch buffer which is two instructions wide and the issue logic. The major functions of the issue logic are:

- Opcode decoding to determine the instruction class and resource requirements for each instruction in the dispatch buffer.

- Rename buffer assignment for fixed and float instruction destinations.

- · Source and destination register dependency checking.

- Execution unit assignment.

- Determine post-dispatch serialization and inhibit subsequent instruction dispatching.

The dispatch system operates in a single processor clock cycle.

## **4.6 Instruction Completion**

Completion provides a mechanism to track instructions from dispatch through execution, then retire or "complete" them in program order. Completing an instruction implies committing to the machine any architectural register changes caused by that instruction. In-order completion ensures the correct architectural state when the machine must recover from a mispredicted branch or any interrupt. Due to the possibility of out-of-order instruction, some state of each instruction must be maintained to allow in-order completion.

Instruction state and all information required for completion is kept in a FIFO queue of six completion buffers. A single completion buffer is allocated for each instruction once it leaves dispatch. A completion buffer is a required resource for dispatch, i.e., if there are no completion buffers available, dispatch will stall. Two instructions per cycle are completed in order from the queue, while interrupts (including mispredicted branches) are monitored.

Figure 4-2. Completion Buffer Queue Block Diagram

Writes to the General Purpose or Floating Point Registers are tracked in their respective rename buffers but are initiated by completion. Other selected architectural register updates are renamed in the completion buffers. The completion logic also signals the functional units when to finish completion-serialized instructions.

The completion buffer queue and associated logic provide:

- Instruction tracking and peak completion of two instructions per cycle.

- Completion of instructions in program order while supporting out-of-order instruction execution, completion serialization and all instruction flow changes.

## 4.7 Interrupt Handling

The interrupt handling unit includes logic to handle interrupts and traps.

## 4.8 System Execution Unit

The System unit executes several miscellaneous instructions, including the Condition Register Logical Operations and Move to/from Special Purpose Register instructions. In order to maintain system state, numerous instructions executed by the system unit are serialized. These instructions access/modify system registers. In addition, due to their infrequent occurrence, the System unit may only hold one instruction for execution.

## 4.9 Data Execution Units

750FX data execution units consist of two fixed point units, the load/store unit, and the floating point unit. Included in the execution units section are the 32 by 32-bit General Purpose Registers (GPRs) and the 32- by 64-bit Floating Point Registers (FPRs). With all execution units busy a maximum of three instructions may speculatively finish in a single cycle but actual completion will support only two per cycle.

The execution units will accept instructions from the dispatcher when not busy. Instructions with data dependencies begin execution when all such dependencies are resolved.

## 4.10 Load / Store Unit

The load/store unit provides the data transfer interface between the cache memory and the internal GPRs and the FPRs. This unit consists of all logic necessary to calculate effective addresses, handle data alignment to and from the cache memory, and provide the sequences for load and store strings and multiples. *Figure 4-1 on page 19* shows the block diagram for the load/store unit.

### 4.11 Caches

#### 4.11.1 750FX Level 1 Cache Description

- 32KB Instruction Cache (8-way set associative)

- 32KB Data Cache (8-way set associative)

- · Physically addressed cache and tag array

- 32 byte line size

- Three-state coherency protocol

- Pseudo Least Recently Used (PLRU) replacement algorithm

### 4.11.1.1 Coherency Support

The 750FX supports a three state coherency protocol which supports the Invalid, Exclusive Unmodified and the Exclusive Modified cache states. This protocol is a compatible subset of the MESI four state protocol and will operate coherently in systems which contain four state caches. The 750FX initiates a broadcast of dcbz (to M=1, coherency required page) and snoops a dcbz broadcast on the 60x bus. All other data cache control instructions are not broadcast unless broadcast is enabled through the HID0[ABE] configuration bit. Instruction cache and TLB control instructions are not broadcast. Except for dcbz all other cache operations are not snooped. The cache operations are intended primarily for the management of the internal cache but not for other caches in the system. However, the optional data cache-op broadcast feature is necessary to allow proper management of a copyback L2.

#### 4.11.1.2 Cache Loads

The 750FX cache lines are loaded in four beats from the 60x bus (64 bits each) or 1 beat from the L2 (256 bits). The burst load is performed critical double word first. The cache which is being loaded is not blocked to internal accesses while the load completes (hits under misses). The critical double word is simultaneously written to the cache reload buffer and forwarded to the requesting unit, thus minimizing stalls due to load delays. The 750FX dcache miss-under-miss feature can be enabled or disabled by HID0. With this enabled one miss can be serviced while a current miss is in progress. Misses can be either load or store type.

### 4.11.1.3 Cache Replacements

Cache lines are selected for replacement based on an PLRU (Pseudo Least Recently Used) algorithm. Each time a cache line is accessed, it is tagged as the most recently used line of the set. When a miss occurs, if all lines in the set are valid (occupied), then the least recently used line is replaced with the new data. The LRU bits in the cache are updated each time a cache hit occurs.

When the data to be replaced is in the XM (exclusive modified) state, that data is written into a writeback buffer while the missed data is being accessed on the bus. When the load completes, the 750FX then pushes the replaced line from the writeback buffer to the L2 if L2 is enabled or to main memory if L2 is disabled.

#### 4.11.2 750FX Level 2 Cache Features.

The 750FX includes an internal level 2 (L2) cache with the following features:

- 512KB 2-way set associative

- Built-in error correction (ECC)

- Single cycle transfer to dcache (32 bytes)

- Handles miss-under-miss

- One from the icache and one from the dcache

- Two (2) from the dcache

- · Dual reload buffers

- Two (2) data load request queues to BIU

- · Cache locking by way with locked side managed by software and not snooped

- Parity added for L2 tags<sup>1</sup>

### 4.12 Bus Interface Unit

The BIU queues up bus requests from the instruction, data, and L2 caches, and runs the requests to the 60x bus. It includes address register queues, prioritization logic, and bus control units. The BIU also captures snoop addresses for snooping in the caches and in the address register queues and snoops for reservations. All data storage for the address register queues (load and store data queues) are located in the cache section. The data queues are considered temporary storage for the cache and not part of the BIU. For the 750FX a second data load queue was added. This bus pipelining feature is needed for support of the cache miss-under-miss capability.

<sup>1.</sup> Not supported under DD 1.X.

## 5. PowerPC 750FX Microprocessor Implementation

The PowerPC Architecture is derived from the POWER architecture (Performance Optimized With Enhanced RISC architecture). The PowerPC Architecture shares the benefits of the POWER architecture optimized for single-chip implementations. The PowerPC Architecture design facilitates parallel instruction execution and is scalable to take advantage of future technological gains.

This section describes the PowerPC Architecture in general, and provides details about the implementation of PowerPC 750FX as a low-power, 32-bit member of the PowerPC processor family.

| For a description of                 | See                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Registers and programming model      | Section 6 on page 25 describes the registers for the operating environment architecture common among PowerPC processors and describes the programming model. It also describes the registers that are unique to PowerPC 750FX.                                                                                                                                                                                         |

| Instruction set and addressing modes | Section 7 on page 27 describes the PowerPC instruction set and addressing modes for the PowerPC operating environment architecture, defines the PowerPC instructions implemented in PowerPC 750FX, and describes new instruction set extensions to improve the performance of single-precision floating-point operations and the capability of data transfer.                                                          |

| Cache implementation                 | Section 8 on page 29 describes the cache model that is defined generally for PowerPC processors by the virtual environment architecture. It also provides specific details about PowerPC 750FX L2 cache implementation.                                                                                                                                                                                                |

| Exception model                      | <i>Table 9</i> on page 31 describes the exception model of the PowerPC operating environment architecture and the differences in PowerPC 750FX exception model.                                                                                                                                                                                                                                                        |

| Memory management                    | <i>Table 10</i> on page 34 describes generally the conventions for memory management among the PowerPC processors. This section also describes PowerPC 750FX's implementation of the 32-bit PowerPC memory management specification.                                                                                                                                                                                   |

| Instruction timing                   | Section 11 on page 36 provides a general description of the instruction timing provided by the superscalar, parallel execution supported by the PowerPC Architecture and PowerPC 750FX.                                                                                                                                                                                                                                |

| Power management                     | Section 12 on page 39 describes how the power management can be used to reduce power consumption when the processor, or portions of it, are idle.                                                                                                                                                                                                                                                                      |

| Thermal management                   | Section 13 on page 41 describes how the thermal management unit and its associated registers (THRM1–THRM3) and exception can be used to manage system activity in a way that prevents exceeding system and junction temperature thresholds. This is particularly useful in high-performance portable systems, which cannot use the same cooling mechanisms (such as fans) that control overheating in desktop systems. |

| Performance monitor                  | Section 14 on page 42 describes the performance monitor facility, which system designers can use to help bring up, debug, and optimize software performance.                                                                                                                                                                                                                                                           |

## 6. PowerPC Registers and Programming Model

The PowerPC Architecture defines register-to-register operations for most computational instructions. Source operands for these instructions are accessed from the registers or are provided as immediate values embedded in the instruction itself. The three-register instruction formats allow specification of a target register distinct from the two source operands. Only load and store instructions transfer data between registers and memory.

PowerPC processors have two levels of privilege—supervisor mode of operation (typically used by the operating system) and user mode of operation (used by the application software, it is also called problem state). The programming models incorporate 32 GPRs, 32 FPRs, special-purpose registers (SPRs), and several miscellaneous registers. Each PowerPC microprocessor also has its own unique set of hardware implementation-dependent (HID) registers.

While running in supervisor mode the operating system is able to execute all instructions and access all registers defined in the PowerPC Architecture. In this mode the operating system establishes all address translations and protection mechanisms, loads all processor state registers. and sets up all other control mechanisms defined on the PowerPC 750CX processor. While running in user mode (problem state) many of these registers and facilities are not accessible and any attempt to read or write these register results in a program exception.

*Figure 6-1* on page 26 shows all the PowerPC 750FX registers available at the user and supervisor level. The numbers to the right of the SPRs indicate the number that is used in the syntax of the instruction operands to access the register.

|                                    |                         |                   |                           |                           | Confi                    | guration R                           | egisters      |                                  |          |

|------------------------------------|-------------------------|-------------------|---------------------------|---------------------------|--------------------------|--------------------------------------|---------------|----------------------------------|----------|

| Time Bas                           | USER MO<br>se Facility  |                   |                           | Hardware<br>Implementatio | n Registers <sup>1</sup> | Processor Ve<br>Register             | ersion        | Machine State<br>Register        | e        |

| TBL                                | TBR 268                 | TBU               | TBR 269                   | HIDO                      | SPR 1008                 | PVR                                  | SPR 287       | MSR                              | 7        |

|                                    |                         |                   |                           | HID1                      | SPR 1009                 |                                      |               |                                  | 1        |

| Count r                            |                         |                   | eneral-Purpose            |                           | Memory I                 | Managemer                            | nt Register   | 'S                               |          |

| Register<br>XER                    | CTR<br>XER              |                   | egisters                  | Instruction<br>Registers  | BAT                      | Data BAT<br>Registers                | -             | Segment<br>Registers             |          |

| L                                  |                         | Joint             | GPR0                      | IBATOU                    | SPR 528                  | DBATOU                               | SPR 536       | SR0                              | 7        |

| Link Reg                           | yister                  |                   | GPR1                      | IBATOL                    | SPR 529                  | DBATOL                               | SPR 537       | SR1                              | -        |

| LR                                 | SPR 8                   |                   |                           | IBAT1U                    | SPR 530                  | DBAT1U                               | SPR 538       | •                                | 1        |

| Condition                          | Register                |                   | GPR31                     | IBAT1L                    | SPR 531                  | DBAT1L                               | SPR 539       | :                                |          |

| CR                                 |                         |                   | GPRJI                     | IBAT2U                    | SPR 532                  | DBAT2U                               | SPR 540       | SR15                             |          |

| Deve                               | ormonoo                 | Floating-         | Point Registers           | IBAT2L                    | SPR 533                  | DBAT2L                               | SPR 541       | <u>.</u>                         | -        |

|                                    | ormance<br>or Registers |                   | FPR0                      | IBAT3U                    | SPR 534                  | DBAT3U                               | SPR 542       | SDR1                             |          |

|                                    | Reading)                |                   | FPR1                      | IBAT3L                    | SPR 535                  | DBAT3L                               | SPR 543       | SDR1                             | SPR 25   |

| Perform                            | ance Coun               | ters <sup>1</sup> |                           |                           | -<br>Exception           | Handling                             | <br>Registers | L                                | -        |

| UPMC1                              | SPR 9                   | 37                |                           | SPRGs                     | Exception                | Data Addre                           | •             | Save and Re                      | estore   |

| UPMC2                              | 2 SPR 9                 | 38<br>Eloat       | FPR31<br>ing-Point Status | SPRG0                     | SPR 272                  | Register                             |               | Registers                        |          |

| UPMC3                              | SPR 9                   | 41 and            | Control Register          | SPRG1                     | SPR 273                  | DAR                                  | SPR 19        | SRR0                             | SPR 26   |

| UPMC4                              |                         | 942 I             | FPSCR                     | SPRG2                     | SPR 274                  | DSISR                                |               | SRR1                             | SPR 27   |

| Monitor C                          | Control <sup>1</sup>    | Sample            | d Instruction             | SPRG3                     | SPR 275                  | DSISR                                | SPR 18        |                                  |          |

| UMMCR                              | 0 SPR 93                | Addres            | S'                        |                           |                          | llaneous R                           | eaisters      |                                  |          |

| UMMCR                              | 1 SPR 94                | USIA              | SPR 939                   | External Ac               |                          | Time Base                            | -             | Decremente                       | ۶r       |

|                                    |                         |                   |                           | Register                  | 7                        | (For Writin                          |               | DEC                              | SPR 22   |

|                                    |                         |                   |                           | EAR                       | SPR 282                  | TBL                                  | SPR 284       | Instruction                      | Address  |

|                                    |                         |                   |                           | Data Addre<br>Breakpoint  |                          | TBU                                  | SPR 285       | Breakpoint                       |          |

|                                    |                         |                   |                           | DABR                      | SPR 1013                 | L2 Control<br>Register <sup>1</sup>  |               | IABR                             | SPR 10   |

|                                    | Performar<br>tor Reg    |                   |                           |                           |                          | L2CR                                 | SPR 1017      | ,                                |          |

| erformanc<br>counters <sup>1</sup> | -                       |                   | Instruction               |                           |                          |                                      |               |                                  |          |

| PMC1                               | SPR 953                 | SIA               | SPR 955                   |                           |                          |                                      | •             | ment Registe                     |          |

| PMC2                               |                         | Monitor C         | Control <sup>1</sup>      |                           |                          | nal Assist<br>Registers <sup>1</sup> | -             | Instruction Ca<br>Throttling Cor |          |

| PMC3                               | SPR 957                 | MMCR0             | SPR 952                   |                           | THR                      | M1 SPR                               | 1020          | Register <sup>1</sup>            |          |

| PMC4                               | SPR 958                 | MMCR1             | SPR 956                   |                           | THR                      | M2 SPR                               | 1021          | ICTC                             | SPR 1019 |

|                                    |                         |                   |                           |                           | THR                      | M3 SPR                               | 1022          |                                  |          |

#### Figure 6-1. PowerPC 750FX Microprocessor Programming Model — Registers

## 7. Instruction Set

All PowerPC instructions are encoded as single-word (32-bit) instructions. Instruction formats are consistent among all instruction types (primary op-code is always 6 bits, register operands always specified in the same bit fields in the instruction), permitting efficient decoding to occur in parallel with operand accesses. This fixed instruction length and consistent format greatly simplify instruction pipelining.

### 7.1 PowerPC Instruction Set

The PowerPC instructions are divided into the following categories.

1. Integer instructions

These include computational and logical instructions.

- Integer arithmetic instructions

- Integer compare instructions

- Integer logical instructions

- Integer rotate and shift instructions

#### 2. Floating-point instructions

These include floating-point computational instructions, as well as instructions that affect the FPSCR.

- Floating-point arithmetic instructions

- Floating-point multiply/add instructions

- Floating-point rounding and conversion instructions

- Floating-point compare instructions

- Floating-point status and control instructions

- 3. Load/store instructions

These include integer and floating-point load and store instructions.

- Integer load and store instructions

- Integer load and store multiple instructions

- Floating-point load and store

- Primitives used to construct atomic memory operations (lwarx and stwcx. instructions)

- 4. Flow control instructions

These include branching instructions, condition register logical instructions, trap instructions, and other instructions that affect the instruction flow.

- Branch and trap instructions

- Condition register logical instructions (sets conditions for branches)

- System Call

- 5. Processor control instructions

These instructions are used for synchronizing memory accesses and management of caches, TLBs, and the segment registers.

- Move to/from SPR instructions

- Move to/from MSR

- Synchronize (processor and memory system)

- Instruction synchronize

- Order loads and stores

- 6. Memory control instructions

To provide control of caches, TLBs, and SRs.

- Supervisor-level cache management instructions

- User-level cache instructions

- Segment register manipulation instructions

- Translation lookaside buffer management instructions

This grouping does not indicate the execution unit that executes a particular instruction or group of instructions.

Integer instructions operate on byte, half-word, and word operands. Floating-point instructions operate on single-precision (one word) and double-precision (two words) floating-point operands. The PowerPC Architecture uses instructions that are four bytes long and word-aligned. It provides for integer byte, half-word, and word operand loads and stores between memory and a set of 32 GPRs. It also provides for single and double-precision loads and stores between memory and a set of 32 floating-point registers (FPRs).

Computational instructions do not access memory. To use a memory operand in a computation and then modify the same or another memory location, the memory contents must be loaded into a register, modified, and then written back to the target location using three or more instructions.

PowerPC processors follow the program flow when they are in the normal execution state; however, the flow of instructions can be interrupted directly by the execution of an instruction or by an asynchronous event. Either type of exception will cause the associated exception handler to be invoked.

Effective address computations for both data and instruction accesses use 32-bit signed two's complement binary arithmetic. A carry from bit 0 and overflow are ignored.

## 8. On-Chip Cache Implementation

This section describes the PowerPC Architecture treatment of cache in general, and the PowerPC 750FX-specific implementation.

## 8.1 PowerPC Cache Model

The PowerPC Architecture does not define hardware aspects of cache implementations. For example, PowerPC processors can have unified caches, separate instruction and data caches (Harvard architecture), or no cache at all. PowerPC microprocessors control the following memory access modes on a virtual page or block (BAT) basis

- Write-back/write-through mode

- Caching-inhibited mode

- Memory coherency

The caches are physically addressed, and the data cache can operate in either write-back or write-through mode, as specified by the PowerPC Architecture.

The PowerPC Architecture defines the term 'cache block' as the cacheable unit. The VEA and OEA define cache management instructions that a programmer can use to affect cache contents.

### 8.2 PowerPC 750FX Microprocessor Cache Implementation

#### 8.2.1 Description of 750FX L1 Caches

- 32K byte, 8-way set associative, L1 instruction cache (pseudo LRU replacement)

- 32K byte, 8-way set associative, L1 data cache (pseudo LRU replacement)

- 32 byte line size with each line having one valid bit and three possible states:

- Exclusive

- Modified

- Invalid

- Physically addressed cache and cache directory. Physical address tag stored in the cache directory.

#### 8.2.2 Description of 750FX L2 Cache

The 750FX 512KB L2 cache is implemented with an internal two-way set-associative tag memory with 4096 tags per way, and an internal 512KB SRAM for data storage. The tags are sectored to support two cache blocks per tag entry (two 32-byte sectors totalling 64 bytes). Each sector (32-byte L1 cache block) in the L2 cache has its own valid and modified bits. In addition, the SRAM includes an 8-bit ECC for every double-word. The ECC logic corrects most single-bit errors and detects double-bit errors as data is read from the SRAM. The L2 cache maintains cache coherency through snooping and is normally configured to operate in copy-back mode.

The L2 cache control register (L2CR) allows control of the following:

- L2 cache configuration

- Double bit error machine check

- Global invalidation of L2 contents

- Write-through operation

- L2 test support

- L2 locking by way<sup>1</sup>

### 8.2.2.1 L2 Cache Operation

The L2 cache for the 750FX is a combined instruction and data cache that receives memory requests from both L1 instruction and L1 data caches independently. The L1 requests are generally the result of instruction fetch misses, data load or store misses, write-through operations, or cache management instructions. Each L1 request generates an address lookup in the L2 tags. If a hit occurs, the instructions or data are forwarded to the L1 cache. A miss in the L2 tags causes the L1 request to be forwarded to the 60x bus interface. The cache block received from the bus is forwarded to the L1 cache immediately, and is also loaded into the L2 cache with the tag marked valid and unmodified. If the cache block loaded into the L2 causes a new tag entry to be allocated and the current tag entry is marked valid modified, the modified sectors of the tag to be replaced are castout from the L2 cache to the 60x bus.

At any given time the L1 instruction cache may have one instruction fetch request, and the L1 data cache may have two loads and two stores requesting L2 cache access. The L2 cache also services snoop requests from the 60x bus. When there are multiple pending requests to the L2 cache, snoop requests have highest priority, followed by data load and store requests (serviced on a first-in, first-out basis). Instruction fetch requests have the lowest priority in accessing the L2 cache when there are multiple accesses pending.

If read requests from both the L1 instruction and L1 data caches are pending, the L2 cache can perform hitunder-miss and supplies the available instruction or data while a bus transaction for the previous L2 cache miss is being performed. The L2 cache supports miss under miss. Up to two outstanding misses are supported: one miss from the instruction cache and one from the data cache, or two data cache misses. Requests that hit will be serviced even while misses are in progress on the bus.

All requests to the L2 cache that are marked cacheable (even if the respective L1 cache is disabled or locked) cause tag lookup and will be serviced if the instructions or data are in the L2 cache. Burst and single-beat read requests from the L1 caches that hit in the L2 cache are forwarded to the L1 caches as instructions or data, and the L2 LRU bit for that tag is updated. Burst writes from the L1 data cache due to a castout or replacement copyback are written only to the L2 cache, and the L2 cache sector is marked modified.

If the L2 cache is configured as write-through, the L2 sector is marked unmodified, and the write is forwarded to the 60x bus. If the L1 castout requires a new L2 tag entry to be allocated and the current tag is marked modified, any modified sectors of the tag to be replaced are cast out of the L2 cache to the 60x bus.

Single-beat read requests from the L1 caches that miss in the L2 cache do not cause any state changes in the L2 cache and are forwarded on the 60x bus interface. Cacheable single-beat store requests marked copy-back that hit in the L2 are allowed to update the L2 cache sector, but do not cause L2 cache sector allocation or deallocation. Cacheable, single-beat store requests that miss in the L2 are forwarded to the 60x bus. Single-beat store requests marked write-through (through address translation or through the configuration of L2CR[L2WT]) are written to the L2 cache if they hit and are written to the 60x bus independent of the L2 hit/miss status. If the store hits in the L2 cache, the modified/unmodified status of the tag remains unchanged. All requests to the L2 cache that are marked cache-inhibited by address translation (through either the MMU or by default WIMG configuration) bypass the L2 cache and do not cause any L2 cache tag state change.

<sup>1.</sup> Not supported in DD1.X

## 9. Exception Model

The section describes the PowerPC exception model and the PowerPC 750FX implementation.

### 9.1 PowerPC Exception Model

The PowerPC exception mechanism allows the processor to interrupt the instruction flow to handle certain situations caused by external signals, errors, or unusual conditions arising from the instruction execution. When exceptions occur, information about the state of the processor is saved to certain registers, and the processor begins execution at an address (exception vector) predetermined for each exception. System software must complete the saving of the processor state prior to servicing the exception. Exception processing proceeds in supervisor mode.

Although multiple exception conditions can map to a single exception vector, a more specific condition may be determined by examining a register associated with the exception—for example, the MSR, DSISR and the FPSCR contain status bits which farther identify the exception condition. Additionally, some exception conditions can be explicitly enabled or disabled by software.

The PowerPC Architecture requires that exceptions be handled in specific priority and program order; therefore, although a particular implementation may recognize exception conditions out of order, they are handled in program order. When an instruction-caused exception is recognized, any unexecuted instructions that appear earlier in the instruction stream, including any that are undispatched, are required to complete before the exception is taken, and any exceptions those instructions cause must also be handled first; likewise, asynchronous, precise exceptions are recognized when they occur but are not handled until the instructions currently in the completion queue successfully retire or generate an exception, and the completion queue is emptied.

Unless a catastrophic condition causes a system reset or machine check exception, only one exception is handled at a time. For example, if one instruction encounters multiple exception conditions, those conditions are handled sequentially in priority order. After the exception handler completes, the instruction processing continues until the next exception condition is encountered. Recognizing and handling exception conditions sequentially guarantees system integrity.

When an exception is taken, information about the processor state before the exception was taken is saved in SRR0 and SRR1. Exception handlers must save the information stored in SRR0 and SRR1 early to prevent the program state from being lost due to a system reset and machine check exception or due to an instruction-caused exception in the exception handler, and before re-enabling external interrupts. The exception handler must also save and restore any GPR registers used by the handler.

The PowerPC Architecture supports four types of exceptions.

1. Synchronous, precise

These are caused by instructions. All instruction-caused exceptions are handled precisely; that is, the machine state at the time the exception occurs is known and can be completely restored. This means that (excluding the trap and system call exceptions) the address of the faulting instruction is provided to the exception handler and that neither the faulting instruction nor subsequent instructions in the code stream will complete execution before the exception is taken. Once the exception is processed, execution resumes at the address of the faulting instruction (or at an alternate address provided by the exception handler). When an exception is taken due to a trap or system call instruction, execution resumes at an address provided by the handler.

#### 2. Synchronous, imprecise

The PowerPC Architecture defines two imprecise floating-point exception modes, recoverable and nonrecoverable. Even though PowerPC 750FX provides a means to enable the imprecise modes, it implements these modes identically to the precise mode (that is, enabled floating-point exceptions are always precise).

3. Asynchronous, maskable

The PowerPC Architecture defines external and decrementer interrupts as maskable, asynchronous exceptions. When these exceptions occur, their handling is postponed until the next instruction, and any exceptions associated with that instruction, completes execution. If no instructions are in the execution units, the exception is taken immediately upon determination of the correct restart address (for loading SRR0). As shown in the *Table 9-1* on page 32 the PowerPC 750FX implements additional asynchronous, maskable exceptions.

4. Asynchronous, nonmaskable

There are two nonmaskable asynchronous exceptions: system reset and the machine check exception. These exceptions may not be recoverable, or may provide a limited degree of recoverability. Exceptions report recoverability through the MSR[RI] bit.

### 9.2 PowerPC 750FX Microprocessor Exception Implementation

The PowerPC 750FX exception classes described above are shown in the *Table 9-1 PowerPC 750FX Microprocessor Exception Classifications* Although exceptions have other characteristics, such as priority and recoverability, *Table 9-1* describes categories of exceptions PowerPC 750FX handles uniquely. *Table 9-1* includes no synchronous imprecise exceptions; although the PowerPC Architecture supports imprecise handling of floating-point exceptions, PowerPC 750FX implements these exception modes precisely.

| Table 9-1. | . PowerPC 750FX Microprocessor Exception Classifications |  |

|------------|----------------------------------------------------------|--|

|------------|----------------------------------------------------------|--|

| Synchronous/Asynchronous  | Precise/Imprecise | Exception Type                                                                                   |

|---------------------------|-------------------|--------------------------------------------------------------------------------------------------|

| Asynchronous, nonmaskable | Imprecise         | Machine check, system reset                                                                      |

| Asynchronous, maskable    | Precise           | External, decrementer, system management, performance monitor, and thermal management interrupts |

| Synchronous               | Precise           | Instruction-caused exceptions                                                                    |

*Table 9-2 Exceptions and Conditions* lists the PowerPC 750FX exceptions and conditions that cause them. Exceptions specific to PowerPC 750FX are indicated.

| Exception Type       | Vector Offset<br>(hex) | Causing Conditions                                                                                                                                                       |

|----------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved             | 00000                  | _                                                                                                                                                                        |

| System reset         | 00100                  | Assertion of either HRESET or SRESET or at power-on reset                                                                                                                |

| Machine check        | 00200                  | Assertion of $\overline{\text{TEA}}$ during a data bus transaction, assertion of $\overline{\text{MCP}}$ , an address, data or L2 double bit error. MSR[ME] must be set. |

| DSI                  | 00300                  | As specified in the PowerPC Architecture. (e.g., page fault occurs)                                                                                                      |

| ISI                  | 00400                  | As defined by the PowerPC Architecture. (e.g., page fault occurs)                                                                                                        |

| 1. PowerPC 750FX-spe | cific                  |                                                                                                                                                                          |

| Table 9-2. | Exceptions and Conditions | (Continued) |

|------------|---------------------------|-------------|

|            |                           |             |

| Exception Type                                 | Vector Offset<br>(hex) | Causing Conditions                                                                                                                                                                                                                                                                                                                                |  |

|------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| External interrupt                             | 00500                  | MSR[EE] = 1 and INT is asserted.                                                                                                                                                                                                                                                                                                                  |  |

| Alignment                                      | 00600                  | A floating-point load/store, <b>stmw, stwcx, lmw</b> , <b>lwarx</b> , <b>eciwx</b> or <b>ecowx</b> instruction operand is not word-aligned.<br>A multiple/string load/store operation is attempted in little-endian mode.<br>The operand of <b>dcbz</b> is in memory that is write-through-required or caching-inhibited of the cache is disabled |  |

| Program                                        | 00700                  | As defined by the PowerPC Architecture.                                                                                                                                                                                                                                                                                                           |  |

| Floating-point unavailable                     | 00800                  | As defined by the PowerPC Architecture.                                                                                                                                                                                                                                                                                                           |  |

| Decrementer                                    | 00900                  | As defined by the PowerPC Architecture, when the most significant bit of the DEC reg-<br>ister changes from 0 to 1 and MSR[EE] = 1.                                                                                                                                                                                                               |  |

| Reserved                                       | 00A00-00BFF            | -                                                                                                                                                                                                                                                                                                                                                 |  |

| System call                                    | 00C00                  | Execution of the System Call (sc) instruction.                                                                                                                                                                                                                                                                                                    |  |

| Trace                                          | 00D00                  | MSR[SE] = 1 or a branch instruction completes and MSR[BE] = 1. Unlike the architec-<br>ture definition, <b>isync</b> does not cause a trace exception                                                                                                                                                                                             |  |

| Reserved                                       | 00E00                  | PowerPC 750FX does not generate an exception to this vector. Other PowerPC pro-<br>cessors may use this vector for floating-point assist exceptions.                                                                                                                                                                                              |  |