# Migrating from the GT6426x Devices to the MV6436x Devices

Doc. No. MV-S100648-00, Rev. A

February 6, 2002

| Document Status            |                                                                                                                                                                                                                          |                               |  |  |  |  |  |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--|--|--|--|--|--|

| Advanced<br>Information    | This datasheet contains design specifications for initial product development. Specifications may change without notice. Contact Marvell Field Application Engineers for more information.                               |                               |  |  |  |  |  |  |

| Preliminary<br>Information | This datasheet contains preliminary data, and a revision of this document will be published at a later date. Specifications may change without notice. Contact Marvell Field Application Engineers for more information. |                               |  |  |  |  |  |  |

| Final<br>Information       | This datasheet contains specifications on a product that is in final release. Specifications may change without notice. Contact Marvell Field Application Engineers for more information.                                |                               |  |  |  |  |  |  |

| Revision Code:             |                                                                                                                                                                                                                          |                               |  |  |  |  |  |  |

| Final Informat             | ion                                                                                                                                                                                                                      | Technical Publication: Rev. A |  |  |  |  |  |  |

Preliminary or Advanced Information

This document provides preliminary or advanced information about the products described. All specifications described herein are based on design goals only. **Do not use** for final design. Visit Marvell's web site at www.marvell.com or call 1-866-674-7253 for the latest information on Marvell products.

#### Disclaimer

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no warranty of any kind, expressed or implied, with regard to any information contained in this document, including, but not limited to, the implied warranties of mechantability or fitness for any particular purpose. Further, Marvell does not warrant the accuracy or completeness of the information, text, graphics, or other items contained within this document. Marvell makes no commitment either to update or to keep current the information contained in this document. Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use Marvell products in these types of equipment or applications. The user should contact Marvell to obtain the latest specifications before finalizing a product design.

Marvell assumes no responsibility, either for use of these products or for any infringements of patents and trademarks, or other rights of third parties resulting from its use. No license is granted under any patents, patent rights, or trademarks of Marvell. These products may include one or more optional functions. The user has the choice of implementing any particular optional function. Should the user choose to implement any of these optional functions, it is possible that the use could be subject to third party intellectual property rights. Marvell recommends that the user investigate whether third party intellectual property rights are relevant to the intended use of these products and obtain licenses as appropriate under relevant intellectual property rights.

Marvell comprises Marvell Technology Group Ltd. (MTGL) and its subsidiaries, Marvell International Ltd. (MIL), Marvell Semiconductor, Inc. (MSI), Marvell Asia Pte Ltd. (MAPL), Marvell Japan K.K. (MJKK), Galileo Technology Ltd. (GTL) and Galileo Technology, Inc. (GTI).

Copyright © 2002 Marvell. All Rights Reserved. Marvell, GalNet, Galileo, Galileo Technology, Fastwriter, Moving Forward Faster, Alaska, the M logo, GalTis, GalStack, Gal-Rack, NetGX, Prestera, the Max logo, Communications Systems on Silicon, and Max bandwidth trademarks are the property of Marvell. All other trademarks are the property of their respective owners.

Marvell Semiconductor, Inc.

2350 Zanker Road, San Jose, CA 95131 Phone: (408) 367-1400, Fax: (408) 367-140

CONFIDENTIAL Document Classification: Proprietary Information

# **Table of Contents**

| SEC  | TION 1.         |                                                 | 7 |

|------|-----------------|-------------------------------------------------|---|

| SEC  | TION <b>2</b> . | Overview                                        | 8 |

| SEC  | tion 3.         | CPU INTERFACE1                                  | 0 |

| 3.1  | Address         | Decoding1                                       | 0 |

| 3.2  | CPU Syn         | chronization Barrier1                           | 1 |

| 3.3  | Multi-CPU       | J and SMP (Symmetric Multi Processing) Support1 | 2 |

| 3.4  | Cache Co        | oherency Support1                               | 4 |

| 3.5  | CPU Inter       | rface Register Settings1                        | 5 |

| SEC  | TION 4.         | DDR SDRAM INTERFACE1                            | 8 |

| 4.1  | Operation       | n Mode Register Setting1                        | 8 |

| 4.2  | SDRAM T         | Timing Parameters1                              | 9 |

| 4.3  | DDR SDR         | AM Interface Register Settings2                 | 1 |

| SEC  | tion 5.         | DEVICE INTERFACE                                | 3 |

| 5.1  | Parity Su       | pport for Devices2                              | 3 |

| 5.2  | Device In       | terface Register Settings2                      | 3 |

| Sec. | tion 6.         | PCI INTERFACE                                   | 5 |

| 6.1  | PCI Confi       | iguration Space Header2                         | 5 |

| 6.2  | PCI Sync        | hronization Barrier2                            | 8 |

| 6.3  | Cache Co        | oherency Support2                               | 8 |

| 6.4  | PCI Acce        | ss Control Windows2                             | 8 |

| 6.5  | PCI Interf      | ace Register Settings2                          | 9 |

| SECTION 7. COMMUNICATION INTERFACES          | 32  |

|----------------------------------------------|-----|

| 7.1 Address Decoding                         | .32 |

| 7.2 Gigabit Ethernet Unit Priority Queuing   | .33 |

| 7.3 Interrupt Coalescing                     | .33 |

| 7.4 Rx Address Recognition                   | .33 |

| 7.5 TCP/UDP Checksum Generation and Checking | .33 |

| 7.6 Support for Jumbo Packets (9KB)          | .33 |

| SECTION 8. IDMA UNIT                         | 34  |

| 8.1 Address Decoding                         | .34 |

| 8.2 Cache Coherency Support                  | .34 |

| 8.3 Address Override                         | .34 |

| 8.4 PCI 64-bit Address                       | .36 |

| 8.5 IDMA Unit Register Settings              | .36 |

| SECTION 9. INTERRUPT CONTROLLER              | 39  |

| 9.1 Interrupt Controller Register Settings   | .39 |

| SECTION 10. INTEGRATED SRAM                  | 41  |

| 10.1 Headers Retarget                        | .42 |

| SECTION 11. GENERAL PURPOSE PORT             | 46  |

# **List of Tables**

| GT6426x Vs. MV6436x CPU Registers           | . 15                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GT6426x Vs. MV6436x SDRAM Timing Parameters | . 19                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GT6426x Vs. MV6436x SDRAM Registers         | . 21                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GT6426x Vs. MV6436x SDRAM Registers         | . 23                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GT6426x Vs. MV6436x PCI Registers           | . 29                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GT6426x Vs. MV6436x PCI Registers           | . 36                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Interrupt Cause and Mask Registers          | . 39                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Headers Retarget Control                    | . 42                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Header Retarget Base                        | . 43                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CPU Header Retarget Base and Remap          | . 43                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Headers Retarget Control                    | . 44                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Header Retarget Base                        | . 44                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CPU/PCI0 Header Retarget Base               | . 45                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                             | GT6426x Vs. MV6436x SDRAM Timing Parameters<br>GT6426x Vs. MV6436x SDRAM Registers<br>GT6426x Vs. MV6436x SDRAM Registers<br>GT6426x Vs. MV6436x PCI Registers<br>GT6426x Vs. MV6436x PCI Registers<br>Interrupt Cause and Mask Registers<br>Headers Retarget Control<br>Header Retarget Base<br>CPU Header Retarget Base and Remap<br>Headers Retarget Control<br>Headers Retarget Control<br>Headers Retarget Control<br>Headers Retarget Base and Remap |

### CONFIDENTIAL

| Figure 1: | GT6426x Interfaces                             | 8  |

|-----------|------------------------------------------------|----|

| Figure 2: | MV6436x Interfaces                             | 9  |

| Figure 3: | MV6436x Synchronization Barrier Implementation | 12 |

| Figure 4: | GT6426xPCI Configuration Space Header          | 26 |

| Figure 5: | MV6436xPCI Configuration Space Header          | 27 |

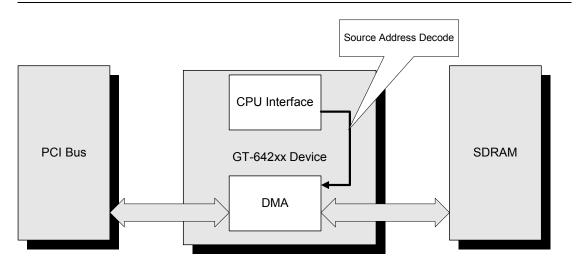

| Figure 6: | GT6426x Devices Address Override               | 35 |

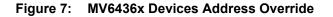

| Figure 7: | MV6436x Devices Address Override               | 35 |

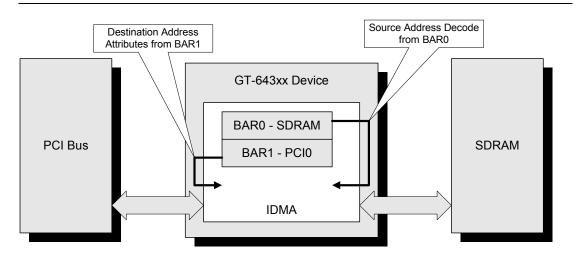

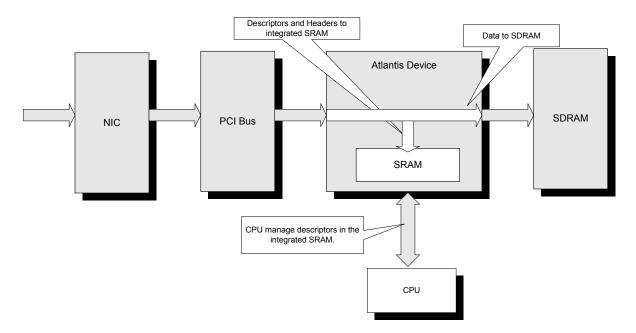

| Figure 8: | Application with Integrated SRAM               | 41 |

# Section 1. Introduction

This document describes the system software implications of the new/updated features of the GT6426x devices that differ from previous GT6426x devices.

The MV6436x datasheets and related documents discuss the detailed changes themselves.

| $\overline{\ }$ | Note |

|-----------------|------|

|-----------------|------|

In any conflict in information between the datasheet and this document, the datasheet's information is correct.

This document identifies and discusses some possible strategies for migrating systems from previous environments to the new MV6436x family devices.

### CONFIDENTIAL

# Section 2. Overview

Changes requiring a thorough treatment will be fully discussed in subsequent sections. The differences are organized and described according to the GT6426x interfaces or internal units.

- CPU interface

- SDRAM interface

- Device interface

- PCI interface

- Communication interfaces

- IDMA unit

- Interrupt controller

- Integrated SRAM

- General Purpose Port

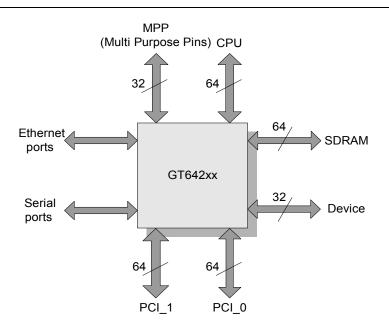

Figure 1 describes the GT6426x interfaces.

#### Figure 1: GT6426x Interfaces

# CONFIDENTIAL

Copyright © 2002 Marvell February 6, 2002,

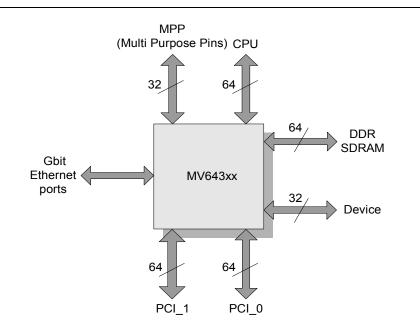

Figure 2 describes the MV6436x interfaces.

### Figure 2: MV6436x Interfaces

#### Note

Unless cited otherwise within this document, a reference to the GT6426x devices is a reference to the GT6426x/A/B.

# Section 3. CPU Interface

# 3.1 Address Decoding

The MV6436x CPU interface address decoding is NOT software compatible with GT6426x CPU interface address decoding scheme. Base and Top registers no longer define the address windows. Instead, the address windows in MV6436x are defined by Base and Size registers, similar to the PCI address-decoding scheme. Moreover the MV6436x support 36-bits addressing.

In the GT6426x devices, two registers define each address window - Low and High. The CPU address is compared with the values in the various CPU Low and High Decode registers.

The GT6426x CPU address windows are defined in 1 Mbyte granularity.

- The Base Address window is 12-bit wide, corresponding to CPU address bits [0:11].

- The High window is 12-bit wide, corresponds to address bits[0:11].

The MV6436x CPU address windows are defined in 64 KB granularity and can be configured up to 4 GB (except of the integrated SRAM which is fixed 256 KB).

- The Base Address is 20-bits wide, corresponding to CPU address bits [0:19]

- The Size is 16-bit wide, corresponding to address bits ] [4:19].

The Size register must be programmed as a set of '1's (staring from the LSB) followed by a set of '0's. The set of '1's define the window size. For example, if Size [15:0] is set to 0x03ff, the size is defined as 64Mbyte.

For example, configure SCS[1] to address 0x0.0A00.0000 - 0x0.0BFF.FFFF (32 MB size)

In the GT6426xthe address appears as:

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | CPU Address Bits     |

|----|----|----|----|----|----|----|----|----|----|----|----|----------------------|

| 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | Low Decode Register  |

| 0  | 0  | 0  | 0  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | High Decode Register |

- SCS[1]\* Low Decode Address 0x208 = 0xA0

- SCS[1]\* High Decode Address 0x210 = 0xBF

In MV6436xthe address appears as:.

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | CPU Address<br>Bits      |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|--------------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | Base Address<br>Register |

|   |   |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | Size Register            |

CS[1]\* Base Address 0x208 = 0xA00

CS[1]\* Size 0x210 = 0x1FF

Also, the default memory map in the MV6436x devices was changed to support an additional address window for the Integrated SRAM (see "Integrated SRAM" on page 41). This additional default internal

Doc. No. MV-S100648-00, Rev. A

### CONFIDENTIAL

SRAM address window (0x4200.0000 to 0x4203.FFFF) was not implemented the GT6426x devices. SW porting must make sure this window is not being used by any other resource or close/move this window.

The GT6426x devices implement two address windows (CPU 0/1) to map the IDMA and communication units to the CPU interface. These windows were implemented to enable the IDMA and communication units to access additional slaves on the CPU interface in multi-GT (multislave) modes.

The MV6436x does not implement the CPU 0/1 address decode windows. Instead, each of the Gigabit Ethernet, MPSCs, and the IDMA units interfaces implements its own address decoding mechanism (see "Communication Interfaces" on page 32 and "Interrupt Controller" on page 39). This mechanism enables the IDMA and communication units to access additional slaves on the CPU interface in multi-GT (multi-slave) mode and to any other interface.

# 3.2 CPU Synchronization Barrier

### 3.2.1 GT6426x Synchronization Barrier Implementation

The GT6426x devices implement two CPU synchronization barrier registers (offsets 0xC0 and 0xC8). One barrier register for each PCI interface. A CPU read from on of these registers creates a synchronization barrier cycle. When there is no posted write data in the buffers, the CPU read returns random data that should be ignored. The CPU interface treats PCI I/O reads and configuration reads as synchronization barrier cycles. These reads receive a response once no posted data remains within the PCI slave write buffer. To disable these sync barrier, set the CPU Configuration register's ConfSBDis and IOSBDis bits [29:28] to '1'.

### 3.2.2 MV6436x Synchronization Barrier Implementation

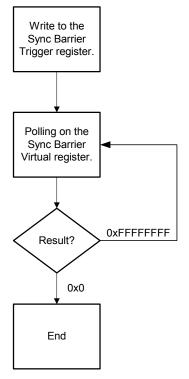

The MV6436x synchronization barrier implementation is different than the GT6426x implementation. The MV6436x implementation is register polling based, rather than a single read waiting for resolution. The MV6436x implements two sets of CPU sync barrier register. Each set contains a CPU Sync Barrier Trigger register (offsets 0xC0 and 0xD0), and a CPU Sync Barrier Virtual register (offsets 0xC8 and 0xD8). Two CPUs (one per each CPU) can use the two sets in a multi-CPU configuration.

For a CPU to activate a sync barrier, it first needs to write to the Trigger register and then perform read polling on the Virtual register. The trigger register is 4-bit wide. Each bit defines which buffers must be flushed. A write to the CPU Sync Barrier Trigger register triggers the sync barrier state machine. A subsequent read polling on the CPU Sync Barrier Virtual register results in value of 0xffff.ffff, until the sync action completes. As soon as the buffers are flushed, a read of the Virtual register results in value of 0x0. The user can set more then one bit in the trigger register, in this case the synchronization barrier mechanism will wait for the last resource to be flushed before returning data of 0x0on reads from the Sync Barrier Virtual register.

### CONFIDENTIAL

#### Figure 3: MV6436x Synchronization Barrier Implementation

Moreover, the GT6426x CPU synchronization barrier is not applicable when using cache coherency. This issue was solved in the MV6436x and the CPU synchronization barrier guarantees that the snoop queue is empty as well as the PCI slave buffer.

### 3.3 Multi-CPU and SMP (Symmetric Multi Processing) Support

### 3.3.1 SMP Boot-sequence

The GT-6426x Rev0 does not support SMP Boot-up sequence. To prevent a race between multiple CPU boot code executions, an external logic must be implemented.

The GT-6426x RevA and GT-6436x support SMP Boot-up sequence. After reset, the CPU1 arbitration is disabled, meaning that the arbiter will not grant the 60x bus CPU1. This allows CPU0 to boot first and initialize the system. Upon completing this operation, CPU0 enables the CPU1 arbitration by clearing the CPU Master Control register's MaskBR1 bit [9] (Offset 0x160).

#### Note

The SMP Boot sequence feature is only applicable when using the internal arbiter. To enable the internal arbiter, the CPU Master Control register's IntArb bit [8] to '1' must be set (by sampling at reset or serial ROM initialization).

Doc. No. MV-S100648-00, Rev. A

### CONFIDENTIAL

Copyright © 2002 Marvell February 6, 2002,

Page 12

### 3.3.2 Interrupts

Note

The GT-6426x devices support only one interrupt signal to the CPU interface that can be masked. The GT-6436x has two interrupt pins, one per each CPU. Each interrupt has its own mask register.

For more information, see "Interrupt Controller" on page 39.

Moreover, the GT-6436x has two 8-bit wide Doorbell registers (offsets 0x214 and 0x224), one per each CPU. The Doorbell registers can be used for CPU-to-CPU interrupt generation or for external PCI device to CPU interrupt generation, or even for the CPU to interrupt itself. When the corresponding bit in a Doorbell Mask registers (offsets 0x234 and 0x23C) is set to '1', set the corresponding bit in the CPU doorbell register (offsets 0x214 and 0x224). Additionally, there is a separate pair of Doorbell Clear registers (offsets 0x21C and 0x22C), one per each CPU, that are used by the CPUs to clear doorbell interrupts. A CPU writes a value of '1' to the Clear Doorbell register bit which clears the corresponding interrupt.

#### Notes

- Each CPU can only clear it's own Clear Doorbell register.

- The Doorbell Interrupt feature is applicable only when using the internal arbiter.

### 3.3.3 Semaphores

The GT-6436x supports eight Semaphore registers (offsets 0x244 - 0x27C). These semaphores can be used as a lock mechanism between the two CPUs and even between the CPUs and an external PCI agent. The first owner to read a Semaphore register receives it's own ID. This owner now controls this semaphore. Once locked by one of the three possible owners, a read of the Semaphore register by any of the other two possible owners returns the owner ID assigned to the current owner. To unlock a semaphore, the owner writes back a value of 0xff.

For example, communication interface in SMP system can only be accessed by only one CPU at a certain time. before any access to the descriprots list (ring) the CPU must read one of the semaphore registers that is reserved for this use. If this read's returned data is equals to its own ID (the CPU ID can be read from the "who am I" register, see section below), the CPU can access the descriptors list. If the data returned for the semaphore register is not equal to the CPU ID, it should poll the semaphore register until it gets it own ID from this register.

### Note

The semaphore feature is only applicable when using the internal arbiter. To enable the internal arbiter, the CPU Master Control register's IntArb bit [8] to '1' must be set (by sampling at reset or serial ROM initialization).

### CONFIDENTIAL

### 3.3.4 "Who am I" register

The GT-6436x includes an "Who Am I" register (offset 0x200). This is a read only register and it may help the software running on the CPU to identify itself.

- A CPU0 read from this register results in a value of 0x0.

- A CPU1 read results in a value of 0x1.

- An external PCI agent read results in a value of 0x2.

### Note

The "Who am I" feature is only applicable when using the internal arbiter. To enable the internal arbiter, the CPU Master Control register's IntArb bit [8] to '1'.

### 3.4 Cache Coherency Support

The GT-6426x supports up to four SDRAM address windows, not correlated to specific chip selects, in which cache coherency is maintained. A pair of base/top registers (Snoop Control Register offsets 0x380 to 0x3B8) defines each window. The IDMA unit uses these regions to maintain cache coherency between SDRAM and Cache memories (see "Cache Coherency Support" on page 34).

|--|

### Note

The cache coherency mechanism in the GT-6426x is restricted for the communication interface.

#### Note

The PCI cache mechanism uses different address windows (See "cache coherency support" subsection in the PCI interface section).

The GT-6436x does not implement these address windows in the CPU interface. Each unit (IDMA, Gigabit Ethernet, MPSCs, and PCI) has its own address windows that can be configured to cache coherency window.

#### Note

All the communication interfaces (Gigabit Ethernet and MPSCs) in the GT-6436x support cache coherency.

### CONFIDENTIAL

Copyright © 2002 Marvell February 6, 2002,

# 3.5 CPU Interface Register Settings

Use the following table to determine any differences in the GT6426x and MV6436x devices CPU registers.

| GT6426x                                            | MV6436x                                        | Comments                  |

|----------------------------------------------------|------------------------------------------------|---------------------------|

| CPU Configuration 0x000                            | CPU Configuration 0x000                        | Some changes.             |

| CPU Mode 0x120                                     | CPU Mode 0x120                                 | Some changes.             |

| CPU Master Control 0x160                           | CPU Master Control 0x160                       | Some changes.             |

| CPU Interface Cross Bar Control<br>(Low) 0x150     | CPU Interface Cross Bar Control<br>(Low) 0x150 | Some changes.             |

| CPU Interface Crossbar Control<br>(High) 0x158     | CPU Interface Crossbar Control<br>(High) 0x158 | Some changes.             |

| CPU Interface Crossbar Timeout<br>0x168            | CPU Interface Crossbar Timeout<br>0x168        | Some changes.             |

| CPU Read Response Crossbar<br>Control (Low) 0x170  | N/A                                            | Not supported in MV6436x. |

| CPU Read Response Crossbar<br>Control (High) 0x178 | N/A                                            | Not supported in MV6436x. |

| N/A                                                | Who Am I 0x200                                 | New register in GT-6436x. |

| N/A                                                | CPU0 Doorbell 0x214                            | New register in GT-6436x. |

| N/A                                                | CPU0 Doorbell Clear 0x21c                      | New register in GT-6436x. |

| N/A                                                | CPU1 Doorbell 0x224                            | New register in GT-6436x. |

| N/A                                                | CPU1 Doorbell Clear 0x22c                      | New register in GT-6436x. |

| N/A                                                | CPU0 Doorbell Mask 0x234                       | New register in GT-6436x. |

| N/A                                                | CPU1 Doorbell Mask 0x23c                       | New register in GT-6436x. |

| N/A                                                | Semaphor0 0x244                                | New register in GT-6436x. |

| N/A                                                | Semaphor1 0x24c                                | New register in GT-6436x. |

| N/A                                                | Semaphor2 0x254                                | New register in GT-6436x. |

| N/A                                                | Semaphor3 0x25c                                | New register in GT-6436x. |

| N/A                                                | Semaphor4 0x264                                | New register in GT-6436x. |

| N/A                                                | Semaphor5 0x26c                                | New register in GT-6436x. |

| N/A                                                | Semaphor6 0x274                                | New register in GT-6436x. |

| N/A                                                | Semaphor7 0x27c                                | New register in GT-6436x. |

| PCI_0 Sync Barrier Virtual Regis-<br>ter 0x0c0     | N/A                                            | Not supported in MV6436x. |

Copyright © 2002 Marvell

#### CONFIDENTIAL

February 6, 2002

Document Classification: Proprietary Information

Page 15

### Table 1:GT6426x Vs. MV6436x CPU Registers (Continued)

| GT6426x                                        | MV6436x                                      | Comments                           |

|------------------------------------------------|----------------------------------------------|------------------------------------|

| PCI_1 Sync Barrier Virtual Regis-<br>ter 0x0c8 | N/A                                          | Not supported in MV6436x.          |

| N/A                                            | CPU0 Sync Barrier Trigger<br>Register0 0x0c0 | New register in MV6436x.           |

| N/A                                            | CPU0 Sync Barrier Virtual<br>Register0 0x0c8 | New register in MV6436x.           |

| N/A                                            | CPU1 Sync Barrier Trigger<br>Register10x0d0  | New register in MV6436x.           |

| N/A                                            | CPU1 Sync Barrier Virtual<br>Register10x0d8  | New register in MV6436x.           |

| Snoop Base Address 0 0x380                     | N/A                                          | Not supported in MV6436x.          |

| Snoop Top Address 0 0x388                      | N/A                                          | Not supported in MV6436x.          |

| Snoop Base Address 1 0x390                     | N/A                                          | Not supported in MV6436x.          |

| Snoop Top Address 1 0x398                      | N/A                                          | Not supported in MV6436x.          |

| Snoop Base Address 2 0x3a0                     | N/A                                          | Not supported in MV6436x.          |

| Snoop Top Address 2 0x3a8                      | N/A                                          | Not supported in MV6436x.          |

| Snoop Base Address 3 0x3b0                     | N/A                                          | Not supported in MV6436x.          |

| Snoop Top Address 3 0x3b8                      | N/A                                          | Not supported in MV6436x.          |

| Protect Low Address 0 0x180                    | Protect base Address 0 0x180                 | Bit 31 functions as Window enable. |

| Protect High Address 0 0x188                   | Protect size 0 0x188                         | No changes.                        |

| Protect Low Address 10x190                     | Protect base Address 10x190                  | Bit 31 functions as Window enable. |

| Protect High Address 1 0x198                   | Protect size 10x198                          | No changes.                        |

| Protect Low Address 2 0x1A0                    | Protect base Address 2 0x1A0                 | Bit 31 functions as Window enable. |

| Protect High Address 2 0x1A8                   | Protect size 2 0x1A8                         | No changes.                        |

| Protect Low Address 3 0x1B0                    | Protect base Address 3 0x1B0                 | Bit 31 functions as Window enable. |

| Protect High Address 3 0x1B8                   | Protect size 3 0x1B8                         | No changes.                        |

| Protect Low Address 4 0x1D0                    | N/A                                          | Not supported in MV6436x.          |

| Protect High Address 4 0x1D8                   | N/A                                          | Not supported in MV6436x.          |

| Protect Low Address 5 0x1D0                    | N/A                                          | Not supported in MV6436x.          |

| Protect High Address 5 0x1D8                   | N/A                                          | Not supported in MV6436x.          |

### CONFIDENTIAL

| GT6426x                      | MV6436x | Comments                  |

|------------------------------|---------|---------------------------|

| Protect Low Address 6 0x1E0  | N/A     | Not supported in MV6436x. |

| Protect High Address 6 0x1E8 | N/A     | Not supported in MV6436x. |

| Protect Low Address 7 0x1F0  | N/A     | Not supported in MV6436x. |

| Protect High Address 7 0x1F8 | N/A     | Not supported in MV6436x. |

### Table 1:GT6426x Vs. MV6436x CPU Registers (Continued)

### CONFIDENTIAL

# Section 4. DDR SDRAM Interface

The GT6426x SDRAM controller has a 15-bit address bus (DAdr[12:0] and BankSel[1:0]) and a 64-bit data bus (SData[63:0]). The SDRAM controller supports 16, 64, 128, 256 or 512Mb SDRAMs.Up to 1 GB can be addressed by each SCS for a total SDRAM address space of 4 GB.

The MV6436x DRAM controller has a 16-bit address bus (DAdr[13:0] and BankSel[1:0]) and a 64-bit data bus (SData[63:0]). The SDRAM controller supports 16, 64, 128, 256, 512Mb and 1Gb SDRAMs. Up to 2 GB can be addressed by each SCS for a total SDRAM address space of 8 GB.

# 4.1 Operation Mode Register Setting

### 4.1.1 GT6426x SDRAM Operation Mode Register

In the GT6426x the SDRAM Operation Mode register is used to execute commands other than standard memory reads and writes to the SDRAM. These operations include:

- Normal SDRAM Mode

- NOP Commands

- Pre-charge All Banks

- Load DRAM Mode Register

- Force a Refresh Cycle

To execute one of the above commands on the SDRAM, the following procedure must occur:

- 1. Write to the SDRAM Operation Mode register the required command.

- 2. Read the SDRAM Operation Mode register. This read guarantees that the following step is executed after the register value is updated.

- 3. Dummy word (32-bit) writes to an SDRAM bank. This causes that the required cycle is driven to the selected DRAM bank.

- 4. Polling on SDRAM Operation Mode register until the activate bit is sampled '1'.

- 5. Write a 0x0 value to the SDRAM Operation Mode Register.

- 6. Read the SDRAM Operation Mode register. This read guarantees the execution of the following access to the DRAM, after the register value is updated.

### Note

No access to the SDRAM other then dummy write in the sequence above, is allowed in the middle of the above sequence execution. This means that the above sequence must not be executed from SDRAM since no instruction fetch is allowed.

### 4.1.2 MV6436x SDRAM Operation Mode Register

In the MV6436x, the SDRAM Operation Mode register is used to execute commands other than standard memory reads and writes to the SDRAM. These operations include:

- Normal SDRAM Mode (default mode)

- NOP Commands

- Pre-charge All Banks

- Load DRAM Mode Register

### CONFIDENTIAL

- Load DRAM Extended Mode Register

- Force a Refresh Cycle

Once the CPU changes the register default to one of the command types, The SDRAM controller:

- Executes the required command.

- Resets the register back to the default value.

- Returns to normal operation.

The CPU must poll on this register to identify when the DRAM controller is back in normal operation mode.

# Note

No access to the SDRAM is allowed in the middle of the above sequence execution. This means that the above sequence must not be executed from SDRAM since no instruction fetch is allowed

# 4.2 SDRAM Timing Parameters

The following table describes the differences between the GT6426x and MV6436x timing parameters:

| SDRAM Timing<br>Parameter    | Description                                                                                                                                                                                             | GT6426x                                                                                                                                             | MV6436x                                                                                                                                                     |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCAS* Latency (CL)           | The number of cycles<br>from CAS* assertion to<br>the sampling of the first<br>read data.                                                                                                               | This parameter can be<br>programmed for two or<br>three TClks cycles.<br>SDRAM Timing Parame-<br>ter's register CL bits [1:0]<br>(Offset:0x4b4).    | The SDRAM controller<br>supports a CL setting of<br>1.5, 2, 2.5, 3, 3.5 or 4<br>cycles. SDRAM Mode<br>register's CL bits [6:4]<br>(Offset 0x141c).          |

| SRAS to SCAS<br>Delay (Trcd) | specifies the number of<br>TClk cycles that the<br>DRAM controller inserts<br>between the assertion<br>of SRAS* with a valid<br>row address to the<br>assertion of SCAS* with<br>a valid column address | This parameter can be<br>programmed for two or<br>three TClks cycles.<br>SDRAM Timing Parame-<br>ter's register Trcd bits<br>[5:4] (Offset:0x4b4).  | The SDRAM controller<br>supports Trcd of 2, 3 or 4<br>cycles.<br>SDRAM Timing Parame-<br>ter's register Trcd bits<br>[7:4] (Offset:0x1408).                 |

| SRAS* Pre-charge<br>(Trp)    | Following a possible<br>pre-charge cycle, the<br>minimum number of<br>cycles within which a<br>new activate cycle can<br>occur.                                                                         | This parameter can be<br>programmed for two or<br>three TClks cycles.<br>SDRAM Timing Parame-<br>ters register's Trp bits<br>[3:2] (Offset: 0x4b4). | The SDRAM controller<br>supports a Trp setting of<br>2, 3 or 4 cycles. SDRAM<br>Timing (Low) register's<br>Trp bits [11:8] (Offset:<br>0x1408).             |

| Row Active Time<br>(Tras)    | The minimum number of<br>cycles between activate<br>cycle to pre-charge<br>cycle.                                                                                                                       | This parameter can be<br>programmed for two or<br>three TClks cycles.<br>SDRAM Timing Parame-<br>ters register Tras bits<br>[11:8] (Offset: 0x4b4). | The SDRAM controller<br>supports a Tras setting of<br>5, 6, 7, 8, or 9 cycles.<br>SDRAM Timing (Low) reg-<br>ister's Tras bits [23:20]<br>(Offset: 0x1408). |

Table 2:GT6426x Vs. MV6436x SDRAM Timing Parameters

Copyright © 2002 Marvell

### CONFIDENTIAL

February 6, 2002

| SDRAM Timing<br>Parameter                                | Description                                                                                           | GT6426x | MV6436x                                                                                                                                                                                                                        |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write to DQS<br>(Tdqss)<br><b>NOTE:</b> MV6436x<br>only. | The minimum number of cycles between write commands.                                                  | N/A     | Value '0' means one<br>cycle; value of '1' means<br>two cycles; and so on.<br>SDRAM Timing (Low) reg-<br>ister's Tdqss bits [3:0]<br>(Offset: 0x1408).<br><b>NOTE:</b> Must be '0'.                                            |

| Write to Pre-charge<br>(Twr)<br>NOTE: MV6436x<br>only.   | The minimum number of cycles between write command and pre-charge.                                    | N/A     | Value '0' means one<br>cycle; value of '1' means<br>two cycles; and so on.<br>SDRAM Timing (Low) reg-<br>ister's Twr bits [15:12]<br>(Offset: 0x1408).<br><b>NOTE:</b> Only the values of<br>'1', '2', or '3' are<br>allowed.  |

| Write to Read (Twtr)<br>NOTE: MV6436x<br>only.           | The minimum numbers<br>of cycles between write<br>command and read<br>command.                        | N/A     | Value '0' means one<br>cycle; value of '1' means<br>two cycles; and so on.<br>SDRAM Timing (Low) reg-<br>ister's Twtr bits [19:16]<br>(Offset: 0x1408).<br><b>NOTE:</b> Only the values of<br>'1', '2', or '3' are<br>allowed. |

| Active to Active<br>(Trrd)<br>NOTE: MV6436x<br>only.     | The minimum numbers<br>of cycles between acti-<br>vate bank A to activate<br>bank B.                  | N/A     | Value '0' means one<br>cycle; value of '1' means<br>two cycles; and so<br>on.SDRAM Timing (Low)<br>register's Trrd bits [27:24]<br>(Offset: 0x1408).<br><b>NOTE:</b> Only the values of<br>'1', '2', or '3' are<br>allowed.    |

| Load Mode Register<br>()<br>NOTE: MV6436x<br>only.       | The minimum number of<br>cycles between LMR<br>command and the next<br>LMR command or pre-<br>charge. | N/A     | SDRAM Timing (Low) reg-<br>ister's Tmrd bits [31:28]<br>(Offset: 0x1408).                                                                                                                                                      |

| Refresh Command<br>(Trfc)<br>NOTE: MV6436x<br>only.      | The minimum numbers<br>of cycles between<br>refresh command and<br>the new activate com-<br>mand.     | N/A     | Value '0' means one<br>cycle; value of '1' means<br>two cycles; and so on.<br>SDRAM Timing (High)<br>register's Trfc bits [3:0]<br>(Offset: 0x140c).                                                                           |

#### Table 2:GT6426x Vs. MV6436x SDRAM Timing Parameters (Continued)

### CONFIDENTIAL

February 6, 2002,

| SDRAM Timing<br>Parameter                                  | Description                                                          | GT6426x | MV6436x                                                                                                                                                                                                           |

|------------------------------------------------------------|----------------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read to Read<br>(Trd2rd)<br><b>NOTE:</b> MV6436x<br>only.  | The minimum number of cycles between consec-<br>utive read commands. | N/A     | Value '0' means one<br>cycle; value of '1' means<br>two cycles; and so on.<br>SDRAM Timing (High)<br>register's Trd2rd bits [5:4]<br>(Offset: 0x140c).<br><b>NOTE:</b> Only values of '0'<br>or '1' are allowed.  |

| Read to Write<br>(Trdtwr)<br><b>NOTE:</b> MV6436x<br>only. | The minimum number of cycles between read command to write command.  | N/A     | Value '0' means one<br>cycle; value of '1' means<br>two cycles; and so on.<br>SDRAM Timing (High)<br>register's Trdtwrn bits [7:6]<br>(Offset: 0x140c).<br><b>NOTE:</b> Only values of '0'<br>or '1' are allowed. |

#### Table 2:GT6426x Vs. MV6436x SDRAM Timing Parameters (Continued)

Note

In the GT6426x the SDRAM timing parameters CAS latency, RAS to CAS, and RAS Precharge must be set to the same value (2 or 3).

### 4.3 DDR SDRAM Interface Register Settings

Use the following table to determine any differences between the GT6426x and MV6436x devices SDRAM registers.

#### Table 3:GT6426x Vs. MV6436x SDRAM Registers

| GT6426x                                          | MV6436x                                               | Comments                                      |

|--------------------------------------------------|-------------------------------------------------------|-----------------------------------------------|

| SDRAM Configuration 0x448                        | SDRAM Configuration 0x1400                            | Some changes in MV6436x.                      |

| SDRAM Operation Mode 0x474                       | SDRAM Operation 0x1418                                | Some changes in MV6436x.                      |

| SDRAM Address Control 0x47c                      | SDRAM Address Control 0x1410                          | Some changes in MV6436x.                      |

| SDRAM Timing Parameters<br>0x4b4                 | SDRAM Timing Control (LOW and HIGH) 0x1408 and 0x140C | See "SDRAM Timing Parame-<br>ters" on page 19 |

| SDRAM UMA Control 0x4a4                          | N/A                                                   | Not supported.                                |

| SDRAM Interface Crossbar<br>Control (Low) 0x4a8  | SDRAM Interface Cross Bar<br>Control (Low) 0x1430     | No changes.                                   |

| SDRAM Interface Crossbar<br>Control (High) 0x4ac | SDRAM Interface Cross Bar<br>Control (High) 0x1434    | No changes.                                   |

| SDRAM Interface Crossbar Time-<br>out 0x4b0      | SDRAM Interface Cross Bar Tim-<br>eout 0x1438         | No changes.                                   |

Copyright © 2002 Marvell

#### CONFIDENTIAL

February 6, 2002

#### Table 3:GT6426x Vs. MV6436x SDRAM Registers (Continued)

| GT6426x                          | MV6436x                                  | Comments                                                                                      |

|----------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------|

| SDRAM Bank0 Parameters<br>0x44c  | N/A                                      | Not supported in MV6436x.                                                                     |

| SDRAM Bank1 Parameters<br>0x450  | N/A                                      | Not supported in MV6436x.                                                                     |

| SDRAM Bank2 Parameters<br>0x454  | N/A                                      | Not supported in MV6436x.                                                                     |

| SDRAM Bank3 Parameters<br>0x458  | N/A                                      | Not supported in MV6436x.                                                                     |

| N/A                              | SDRAM Open Pages Control<br>0x1414       | New register in MV6436x.                                                                      |

| N/A                              | SDRAM Mode 0x141c                        | New register in MV6436x.                                                                      |

| N/A                              | SDRAM Extended Mode 0x1420               | New register in MV6436x.                                                                      |

| N/A                              | Dunit Control (Low) 0x1404               | New register in MV6436x.                                                                      |

| N/A                              | Dunit Control (High) 0x1424              | New register in MV6436x.                                                                      |

| N/A                              | SDRAM Timing Control (Low)<br>0x1408     | New register in MV6436x.                                                                      |

| N/A                              | SDRAM Timing Control (High)<br>0x140c    | New register in MV6436x.                                                                      |

| SDRAM Error Data (Low) 0x484     | SDRAM Error Data (Low) 0x1444            | No changes.                                                                                   |

| SDRAM Error Data (High) 0x480    | SDRAM Error Data (High)<br>0x1440        | No changes.                                                                                   |

| SDRAM Error Address 0x490        | SDRAM and Device Error<br>Address 0x1450 | No changes.                                                                                   |

| SDRAM Received ECC 0x488         | SDRAM Received ECC 0x1448                | No changes.                                                                                   |

| SDRAM Calculated ECC 0x48c       | SDRAM Calculated ECC 0x144c              | No changes.                                                                                   |

| SDRAM ECC Control 0x494<br>SDRAM | ECC Control 0x1454                       | No changes.                                                                                   |

| SDRAM ECC Error Counter<br>0x498 | SDRAM ECC Error Counter<br>0x1458        | No changes.                                                                                   |

| N/A                              | MMASK 0x1B40                             | New register in MV6436x.<br>NOTE: Do not use this register. It<br>is reserved for future use. |

### CONFIDENTIAL Document Classification: Proprietary Information

# Section 5. Device Interface

# 5.1 Parity Support for Devices

There is no dedicated logic in the GT6426x devices to support parity on the device bus. If device parity checking is required, connect an external logic to the GPP inputs to generate an interrupt when a bad parity occurs.

The MV6436x device controller supports generating and checking of data parity on the device interface via the DevDP[3:0] pins. Enable/disable parity on a device chip select basis via the Device Bank Parameters registers' DPEn bit [30] (offsets 0x45C to 0x46C). Even or Odd parity is selectable via the Device Interface Control register's ParSel bit [20].

### 5.2 Device Interface Register Settings

Use the following table to determine any differences between the GT6426x and MV6436x devices device controller registers.

| GT6426x                           | MV6436x                 | Comments                            |

|-----------------------------------|-------------------------|-------------------------------------|

| Device Bank0 Parameters 0x45c     |                         | Add data parity support in MV6436x. |

| Device Bank1 Parameters 0x460     |                         | Add data parity support in MV6436x. |

| Device Bank2 Parameters 0x464     |                         | Add data parity support in MV6436x. |

| Device Bank3 Parameters 0x468     |                         | Add data parity support in MV6436x. |

| Boot Device Parameters 0x46c      |                         | Add data parity support in MV6436x. |

| Device Interface Control 0x4c0    |                         | Add data parity support in MV6436x. |

| Device Interface Crossbar Control | (Low) 0x4c8             | Some changes in MV6436x.            |

| Device Interface Crossbar Control | (High) 0x4cc            | Some changes in MV6436x.            |

| Device Interface Crossbar Timeout | 0x4c4                   | No changes.                         |

| Device Interrupt Cause 0x4d0      |                         | Some changes in MV6436x.            |

| Device Interrupt Mask 0x4d4       |                         | Some changes in MV6436x.            |

| Device Error Address 0x4d8        |                         | No changes.                         |

| N/A                               | Device Error Data 0x4dc | New register in MV6436x.            |

### Table 4:GT6426x Vs. MV6436x SDRAM Registers

### CONFIDENTIAL

#### Table 4:GT6426x Vs. MV6436x SDRAM Registers (Continued)

| GT6426x | MV6436x                   | Comments                                                                                          |

|---------|---------------------------|---------------------------------------------------------------------------------------------------|

| N/A     | Device Error Parity 0x4e0 | New register in MV6436x.                                                                          |

| N/A     | MMASK 0x4F0               | New register in MV6436x.<br><b>NOTE:</b> Do not use this register. It is reserved for future use. |

### CONFIDENTIAL

Copyright © 2002 Marvell February 6, 2002,

# Section 6. PCI Interface

The GT6426x implements PCI 2.2 compliant interfaces.

The MV6436x implements PCI-X compliant interfaces. This section will not discuss the PCI-X mode. For more information on the PCI-X mode see the MV6436x data sheet.

# 6.1 PCI Configuration Space Header

The GT6426x implements separate SAC BAR and DAC BAR for the same memory space.

Alternatively, the MV6436x BARs are 64-bit wide and support 32 or 64-bit addressing (SAC or DAC), depending on the setting of the upper 32-bit of the BAR.

### Note

For more information see the respective "PCI Configuration Space Header' figures in the GT6426x or MV6436x datasheet.

### CONFIDENTIAL

### Figure 4: GT6426xPCI Configuration Space Header

#### Function 0 Header

| Device ID Ve      |            | Vend        | Vendor ID |     |

|-------------------|------------|-------------|-----------|-----|

| Sta               | itus       | Com         | mand      | 04h |

| 0                 | Class Code | е           | Rev ID    | 08h |

| BIST              | Header     | Latency     | Line Size | 0Ch |

|                   | SCS[0      | )] BAR      |           | 10h |

|                   | SCS[1      | I] BAR      |           | 14h |

|                   | SCS[2      | 2] BAR      |           | 18h |

|                   | SCS[3      | BAR         |           | 1Ch |

| Mer               | m Mapped   | Internal E  | BAR       | 20h |

| 10                | Mapped     | Internal BA | ٨R        | 24h |

|                   | Rese       | erved       |           | 28h |

| Subsys            | stem ID    | Subsystem   | Vendor ID | 2Ch |

| Expansion ROM BAR |            |             |           | 30h |

| Reserved Cap. Ptr |            |             | 34h       |     |

| Reserved          |            |             | 38h       |     |

| Max_Lat           | Min_Gnt    | Int. Pin    | Int. Line | 3Ch |

|                   |            |             |           | 001 |

#### Function 3 Header

|                   |      | -     |          |      |

|-------------------|------|-------|----------|------|

|                   |      |       |          | 00h  |

|                   |      |       |          | 04h  |

|                   |      |       |          | 08h  |

|                   |      |       |          | loCh |

|                   | Rese | erved |          | 10h  |

|                   | Rese | erved |          | 14h  |

|                   | Rese | erved |          | 18h  |

|                   | Rese | erved |          | 1Ch  |

|                   | Rese | erved |          | 20h  |

|                   | Rese | erved |          | 24h  |

|                   |      | erved |          | 28h  |

|                   |      |       |          | 2Ch  |

|                   | Rese | erved |          | 30h  |

| Reserved Reserved |      |       |          |      |

|                   |      | erved | Rederved | 34h  |

|                   | Rese |       |          | 38h  |

|                   |      |       |          | ]3Ch |

#### Function 1 Header

|          |       |          | 00h |

|----------|-------|----------|-----|

|          |       |          | 04h |

|          |       |          | 08h |

|          |       |          | 0Ch |

| CS[0]    | BAR   |          | 10h |

| CS[1]    | BAR   |          | 14h |

| CS[2]    | BAR   |          | 18h |

| CS[3]    | BAR   |          | 1Ch |

| BootC    | S BAR |          | 20h |

| Rese     | erved |          | 24h |

| Rese     | erved |          | 28h |

|          |       |          | 2Ch |

| Rese     | erved |          | 30h |

| Reserved |       | Reserved | 34h |

| Rese     | erved |          | 38h |

|          |       |          | 3Ch |

Function 4 Header

SCS[0] 64-bit

BAR SCS[1] 64-bit BAR

P2P Mem0 64-bit BAR

Reserved Reserved

Reserved

#### Function 2 Header

|                   |          |        |  | 1          |  |

|-------------------|----------|--------|--|------------|--|

|                   |          |        |  | 00h        |  |

|                   |          |        |  | 04h        |  |

|                   |          |        |  | 08h        |  |

|                   |          |        |  | 0Ch        |  |

|                   | P2P Me   | m0 BAR |  | 10h        |  |

|                   | P2P Me   | m1 BAR |  | 14h        |  |

|                   | P2P I    | ) BAR  |  | 18h        |  |

|                   | CPU      | BAR    |  | 1Ch        |  |

|                   | Reserved |        |  |            |  |

|                   | Reserved |        |  | 20h<br>24h |  |

|                   | Rese     | erved  |  | 28h        |  |

|                   |          |        |  | 2Ch        |  |

| Reserved          |          |        |  |            |  |

| Reserved Reserved |          |        |  | 30h<br>34h |  |

| Reserved          |          |        |  |            |  |

|                   |          |        |  | 38h<br>3Ch |  |

|                   |          |        |  |            |  |

#### Function 5 Header

00h 04h 08h 0Ch

10h 14h 18h

1Ch 20h 24h

28h 2Ch

30h

34h

38h 3Ch

Reserved

|                   |          |            |     | 00h        |

|-------------------|----------|------------|-----|------------|

|                   |          |            |     | 04h        |

|                   |          |            |     | 08h        |

|                   |          |            |     | 0Ch        |

|                   | SCS[2] 6 | 64-bit BAR |     | 10h<br>14h |

| SCS[3] 64-bit BAR |          |            |     |            |

| P2P Mem1 64-bit   |          |            |     | 20h        |

| BAR               |          |            | 24h |            |

|                   | Res      | erved      |     | 28h        |

|                   |          |            |     | 2Ch        |

| Reserved          |          |            |     |            |

| Reserved Reserved |          |            | 34h |            |

|                   | Rese     | erved      |     | 38h        |

|                   |          |            |     | 3Ch        |

#### Function 6 Header

|                   |                  |           |     | 00h<br>04h<br>08h<br>0Ch |

|-------------------|------------------|-----------|-----|--------------------------|

|                   | CS[0] 64         | I-bit BAR |     | 10h<br>14h               |

| CS[1] 64-bit BAR  |                  |           |     |                          |

|                   | CS[2] 64-bit BAR |           |     |                          |

|                   | Rese             | erved     |     | 28h                      |

|                   |                  |           |     | 2Ch                      |

| Reserved          |                  |           |     |                          |

| Reserved Reserved |                  |           | 34h |                          |

| Reserved          |                  |           | 38h |                          |

|                   |                  |           |     | 3Ch                      |

# Function 7 Header

Reserved

|                   | -              |         |     |     |

|-------------------|----------------|---------|-----|-----|

|                   |                |         |     | 00h |

|                   |                |         |     | 04h |

|                   |                |         |     | 08h |

|                   |                |         |     | 0Ch |

| CSI316            | 1.k            | oit BAR |     | 10h |

|                   |                |         |     | 14h |

| Boo               | CS             | 64-bit  |     | 18h |

|                   | ΒA             | ٨R      |     | 1Ch |

| CPU               | CPU 64-bit BAR |         |     | 20h |

|                   | 04-            |         |     | 24h |

| Re                | se             | rved    |     | 28h |

|                   |                |         |     | 2Ch |

| Reserved          |                |         | 30h |     |

| Reserved Reserved |                |         |     |     |

| Reserved          |                |         | 38h |     |

|                   | T              |         |     | 3Ch |

### CONFIDENTIAL

Copyright © 2002 Marvell February 6, 2002,

| Function 0 Header                |                         |          |           |            |

|----------------------------------|-------------------------|----------|-----------|------------|

| Devi                             | ce ID                   | Venc     | lor ID    | 00h        |

| Sta                              | itus                    | Com      | mand      | 04h        |

| (                                | Class Code              | е        | Rev ID    | 08h        |

| BIST                             | Header                  | Latency  | Line Size | 0Ch        |

|                                  | SCS[0                   | ] BAR    |           | 10h<br>14h |

|                                  | SCS[1] BAR              |          |           | 18h<br>1Ch |

| Ме                               | Mem Mapped Internal BAR |          |           | 20h<br>24h |

|                                  | Reserved                |          |           | 28h        |

| Subsystem ID Subsystem Vendor ID |                         |          | 2Ch       |            |

| Expansion ROM BAR                |                         |          | 30h       |            |

| Reserved Cap. Ptr                |                         |          | 34h       |            |

| Reserved                         |                         |          | 38h       |            |

| Max_Lat                          | Min_Gnt                 | Int. Pin | Int. Line | 3Ch        |

### Figure 5: MV6436xPCI Configuration Space Header

| Function | 2 | Header |

|----------|---|--------|

|          |      |          | 00h<br>04h<br>08h<br>0Ch |

|----------|------|----------|--------------------------|

| CS[0]    | BAR  |          | 10h<br>14h               |

| CS[1]    | BAR  |          | 18h<br>1Ch               |

| CS[2]    | BAR  |          | 20h<br>24h               |

| Rese     | rved |          | 28h                      |

|          |      |          | 2Ch                      |

| Rese     | rved |          | 30h                      |

| Reserved |      | Reserved | 34h                      |

| Rese     | rved |          | 38h                      |

|          |      |          | 3Ch                      |

#### Function 1 Header 00h 04h 08h 0Ch 10h SCS[2] BAR 14h 18h SCS[3] BAR 1Ch 20h Int SRAM BAR 24h Reserved 28h 2Ch Reserved 30h Reserved Reserved 34h Reserved 38h 3Ch

#### Function 3 Header

|          |       |          | 00h<br>04h |

|----------|-------|----------|------------|

|          |       |          | 08h        |

|          |       |          | 0Ch        |

| CS[3]    | ] BAR |          | 10h<br>14h |

| BootC    | S BAR |          | 18h<br>1Ch |

| CPU      | BAR   |          | 20h<br>24h |

| Rese     | erved |          | 28h        |

|          |       |          | 2Ch        |

| Rese     | erved |          | 30h        |

| Reserved |       | Reserved | 34h        |

| Rese     | erved |          | 38h        |

|          |       |          | 3Ch        |

#### Function 4 Header

| <br>P2P Me                      | m0 BAR |          | 00h<br>04h<br>08h<br>0Ch<br>10h |

|---------------------------------|--------|----------|---------------------------------|

| P2P Me<br>P2P I/(<br>I/O Mapped | O BAR  | AR       | 14h<br>18h<br>1Ch<br>20h<br>24h |

| Reserved                        |        |          | 28h                             |

|                                 |        |          | 2Ch                             |

| Reserved                        |        |          | 30h                             |

| Reserved                        |        | Reserved | 34h                             |

| Rese                            | erved  |          | 38h                             |

|                                 |        |          | 3Ch                             |

### CONFIDENTIAL

# 6.2 PCI Synchronization Barrier

Within the GT6426x devices, the PCI slave "synchronization barrier" cycles are Configuration Reads. If there is no posted data within the CPU interface write buffer and PCI master write buffer, the cycle ends normally. If after a timeout0 period there is still posted data in the buffers, the cycle is terminated with the Retry signal. Until the original cycle ends, any new "synchronization barrier" cycles are terminated with Retry. The PCI slave only handles a single pending sync barrier transaction at a time.

The MV6436xPCI slave implements two registers:

- Sync Barrier Trigger register (0x1d18 or 0x1d98)

- Sync Barrier Virtual register (0x1d10 or 0x1d90)

A write to the Sync Barrier Trigger register, triggers the sync barrier's state machine. A subsequent read polling on the Sync Barrier Virtual register results in a value of 0xffff.ffff until the sync action completes. As soon as the PCI master write buffers are flushed, a read of the Virtual register results in value of 0x0.

The MV6436x also supports nesting of sync barriers. The PCI agent that triggers the sync barrier may decide to trigger a new sync barrier prior to the result of the previous one (new write to Sync Barrier Trigger register). The MV6436x sync barrier implementation guarantees that a subsequent read polling on the Sync Barrier Virtual register will result in a value of 0x0, only after the second sync barrier is resolved.

### 6.3 Cache Coherency Support

The GT-6426x and GT-6436x support PowerPC cache coherency. Any PCI access to SDRAM may generate a snoop transaction on the CPU bus, to maintain coherency between the CPU cache and SDRAM.

In the GT-6426x, it is possible to configure up to four address ranges in which cache coherency is maintained. PCI Snoop Base and Top Address registers define the address windows. Any PCI access that hits one of these address windows results in snoop transaction.

The GT-6436x does not implement separate cache coherency windows settings. Instead, the cache coherency windows are defined as part of the PCI Access Control windows (PCI Access Control Base register bits 3:2). See section "PCI Access Control Windows" on page 28.

### 6.4 PCI Access Control Windows

The GT6426x PCI slave interface supports configurable access control. It is possible to define up to eight address ranges to different configurations. Each region can be configured to:

- Read prefetch and aggressive prefetch

- PCI unit max burst to other units

- Delayed read

- Write protection

- Access protection

- Byte swapping

Three registers define each address window - Base (low and high) and Top. The MV6436x PCI slave interface also supports configurable access control. Yet, It is only possible to define up to six address ranges to different configurations. Each region can be configured to:

- Write and access protection

- Force REQ64

- Byte swapping

- Cache coherency

### CONFIDENTIAL

- Typical PCI unit to other units burst size

- Read prefetch

Г

Three registers define each address window - Base (low and high) and Size.

### 6.5 PCI Interface Register Settings

Since the PCI configuration space header in the MV6436x implements fewer BARs (see section "PCI Configuration Space Header"), there are fewer BAR size and remap registers in the MV6436x PCI interface.

| GT6426x                                                   | MV6436x                                                                                     | Comments                                                       |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| N/A                                                       | Integrated SRAM BAR Size<br>• PCI0: 0xE00<br>• PCI1: 0xE80                                  | New registers in MV6436x.                                      |

| N/A                                                       | Integrated SRAM Base Address<br>Remap<br>PCI0: 0xE00<br>PCI1: 0xE80                         | New registers in MV6436x.                                      |

| N/A                                                       | PCI Headers Retarget Control<br>• PCI0: 0xF40<br>• PCI1: 0xFC0                              | New registers in MV6436x.                                      |

| N/A                                                       | PCI Headers Retarget Base<br>• PCI0: 0xF44<br>• PCI1: 0xFC4                                 | New registers in MV6436x.                                      |

| N/A                                                       | PCI Headers Retarget (High)<br>• PCI0: 0xF48<br>• PCI1: 0xFC8                               | New registers in MV6436x.                                      |

| N/A                                                       | Status and Command<br>• DLL PCI0: 0x1d20<br>• PCI1: 0x1da0                                  | New registers in MV6436x.                                      |

| N/A                                                       | PCI/MPP Pads Drive Control<br>• PCI_0/MPP[31:16]:<br>0x1d1c<br>• PCI_1/MPP[15:0]:<br>0x1d9c | New registers in MV6436x.                                      |

| PCI Command<br>• PCI_0: 0xc00<br>• PCI_1: 0xc80           |                                                                                             | Some changes in MV6436x.                                       |

| PCI Mode<br>• PCI_0: 0xd00<br>• PCI_1: 0xd80              |                                                                                             | Some changes in MV6436x.                                       |

| PCI Timeout and Retry<br>• PCI_0: 0xc04<br>• PCI_1: 0xc84 |                                                                                             | Timeout0 and Timeout1 bits are not implemented in the MV6436x. |

#### Table 5:GT6426x Vs. MV6436x PCI Registers

Copyright © 2002 Marvell

### CONFIDENTIAL

#### Table 5:GT6426x Vs. MV6436x PCI Registers (Continued)

| GT6426x                                                                            | MV6436x                                                                 | Comments                                                           |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------|

| PCI Read Buffer Discard Timer<br>• PCI_0: 0xd04<br>• PCI_1: 0xd84                  |                                                                         | RdBuffEn bits are not imple-<br>mented in MV6436x.                 |

| PCI Arbiter Control<br>• PCI_0: 0x1d00<br>• PCI_1: 0x1d80                          |                                                                         | No changes.                                                        |

| PCI Interface Crossbar Control (Lo<br>PCI_0 Offset: 0x1d08<br>PCI_1 Offset: 0x1d88 | w)                                                                      | Some changes in MV6436x.                                           |

| PCI Interface Cross Bar Control (H<br>PCI_0: 0x1d0c<br>PCI_1: 0x1d8c               | igh)                                                                    | Some changes in MV6436x.                                           |

| PCI Interface Cross Bar Timeout<br>• PCI_0: 0x1d04<br>• PCI_1: 0x1d84              |                                                                         | No changes.                                                        |