#### **Preliminary Information**

This document contains information on a product under development. The parametric information contains target parameters that are subject to change.

# **CN8980**

### ZipWire2 HDSL2/SDSL Transceiver and Framer

The Conexant ZipWire2 chip set is a DSL transceiver which provides enhanced performance and better maximum reach at a given data rate than existing symmetric transport systems based on 2B1Q or CAP modulation. ZipWire2 is designed to be fully compliant with the OPTIS-based ANSI standard for HDSL2 T1 transport and meets all the current requirements of the emerging ETSI standards for SDSL E1 transport. In particular, flexible control of the transmitted signal power spectral density results in enhanced spectral compatibility with other services such as ADSL, T1. E1, HDSL, and ISDN.

The ZipWire2 chip set goes beyond providing modems for T1 or E1 transport by offering on-chip circuits to facilitate variable data rate operation. These circuits allow the user to trade off data rate for reach performance. In addition, ZipWire2 devices provide a mode of operation supporting legacy HDSL1 (2B1Q) transport and framing so that system OEMs can offer Central Office (CO) equipment capable of operation with 2B1Q-based (e.g., RS8973/8953B) remote terminals. These CO terminals can be later upgraded to OPTIS-based HDSL2 through software modifications.

The ZipWire2 device has a two- or three-chip architecture: analog-front-end and line driver in one chip, and all digital functions in one or two other chips. Major functional blocks in the digital chip include:

- A bypassable framer/mapper function

- A rate-adaptive bit pump DSP with Trellis coding

- A high performance microprocessor core

The framer/mapper features a highly flexible bit-processing engine capable of almost any frame format. In particular, it supports the ANSI HDSL2 and ETSI HDSL1 frame formats. It performs EOC, overhead and payload insertion and extraction, data scrambling, bit stuffing, and sync detection. The framer supports T1/E1 Primary Rate framed or unframed modes. synchronous or asynchronous payload mapping, and per-time-slot random or fixed data insertion. In addition, it has programmable external time slot add/drop controls, bit error metering, and programmable payload mapping which supports 1-, 2-, 4- or 8-bit time slots.

The rate-adaptive DSP is responsible for echo cancellation, line equalization, and data coding. It is capable of 2-, 4-, 8- and 16-PAM coding and contains an integrated software-controlled clock recovery and synthesis function. The on-chip 8051-compatible microprocessor core provides DSP control and sequencing, but can also be used as a general purpose controller for peripheral components such as codecs or T1/E1 framers and to host network management software. The functional block diagram illustrates an overview of the ZipWire2 architecture.

#### **Functional Block Diagram**

#### **Distinguishing Features**

- A highly integrated solution including framer, controller, DSP, AFE, and line driver in two or three small packages.

- Fully compliant with the OPTIS-based ANSI standard for HDSL2 T1 transport and ITU G.shdsl transport.

- An integrated, bypassable, HDSL2 framer/mapper function. The bypass function provides direct access to the DSP interface.

- An on-chip, high performance µP core which provides the internal DSP bit pump sequencing and control. This core can also be used as a general purpose controller for peripheral components, such as codecs or T1/E1 framers, and to host network management software.

- Data rates between 144 kbps and 4,640 kbps. The data rate is software-selectable via an on-board software programmable clock synthesizer.

- The ability to function as a 2B10 transceiver and interoperate with legacy HDSL 2B1Q terminals.

- A device architecture that supports multichannel line cards through the following features:

- Single boot ROM loading.

- Fully autonomous startup sequencing per channel.

- A high-speed PCM interface that allows a maximum of eight devices which can share a common PCM bus.

- Integrated framer for arbitrary time slot assignments per channel.

- Point-to-Multipoint support with signaling channel grooming.

#### **Applications**

- T1 or E1 transport systems

- Variable data rate access systems

- Internet connectivity

- Voice and/or data pair gain systems

- NX64 data transport

- Cellular base station data links

- Campus modems

Data Sheet 100605C

#### **Ordering Information**

| Model Number  | Package                                           | Ambient Temperature Range |

|---------------|---------------------------------------------------|---------------------------|

| DSNP-L300-001 | 80-pin TQFP<br>27 mm × 27 mm BGA                  | 0 °C to + 70 °C           |

| DSNP-L301-001 | 80-pin TQFP<br>27 mm × 27 mm BGA                  | −40 °C to + 85 °C         |

| DSNP-L301-011 | 80-pin TQFP<br>9 × 9 mm CABGA<br>15 × 15 mm CABGA | −40 °C to + 85 °C         |

#### **Revision History**

| Revision | Level    | Date       | Description |

|----------|----------|------------|-------------|

| А        | Advanced | April 1999 | Created     |

| В        | Advanced | April 1999 | _           |

| С        | Advanced | April 2000 | _           |

© 1999, 2000, Conexant Systems, Inc. All Rights Reserved.

Information in this document is provided in connection with Conexant Systems, Inc. ("Conexant") products. These materials are provided by Conexant as a service to its customers and may be used for informational purposes only. Conexant assumes no responsibility for errors or omissions in these materials. Conexant may make changes to specifications and product descriptions at any time, without notice. Conexant makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Conexant's Terms and Conditions of Sale for such products, Conexant assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF CONEXANT PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. CONEXANT FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. CONEXANT SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Conexant products are not intended for use in medical, lifesaving or life sustaining applications. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Conexant™, the Conexant C symbol, and "What's Next in Communications Technologies"™. Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Conexant's Legal Information posted at <a href="https://www.conexant.com">www.conexant.com</a>, which is incorporated by reference.

**Reader Response:** Conexant strives to produce quality documentation and welcomes your feedback. Please send comments and suggestions to tech.pubs@conexant.com. For technical questions, contact your local Conexant sales office or field applications engineer.

# **Table of Contents**

| List of | Figur | es xii                                                                                                                                           |  |  |  |  |

|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| List of | Table | <b>\$</b> xvi                                                                                                                                    |  |  |  |  |

| 1.0     | Intro | duction1-1                                                                                                                                       |  |  |  |  |

|         | 1.1   | References                                                                                                                                       |  |  |  |  |

| 2.0     | Syste | em Overview2-1                                                                                                                                   |  |  |  |  |

|         | 2.1   | ZipWire2 Transceiver/Framer Functional Summary                                                                                                   |  |  |  |  |

|         | 2.2   | ZipWire2 Transceiver/DSP Functional Summary                                                                                                      |  |  |  |  |

|         | 2.3   | ZipWire2 DSL Framer Functional Summary                                                                                                           |  |  |  |  |

|         | 2.4   | ZipWire2 AFE Functional Summary                                                                                                                  |  |  |  |  |

|         | 2.5   | ZipWire2 Transmit Path                                                                                                                           |  |  |  |  |

|         | 2.6   | ZipWire2 Receive Path                                                                                                                            |  |  |  |  |

| 3.0     | Appl  | Application Interfaces                                                                                                                           |  |  |  |  |

|         | 3.1   | Using Internal 8051 Processor Only                                                                                                               |  |  |  |  |

|         | 3.2   | Using an External Embedded Host Processor                                                                                                        |  |  |  |  |

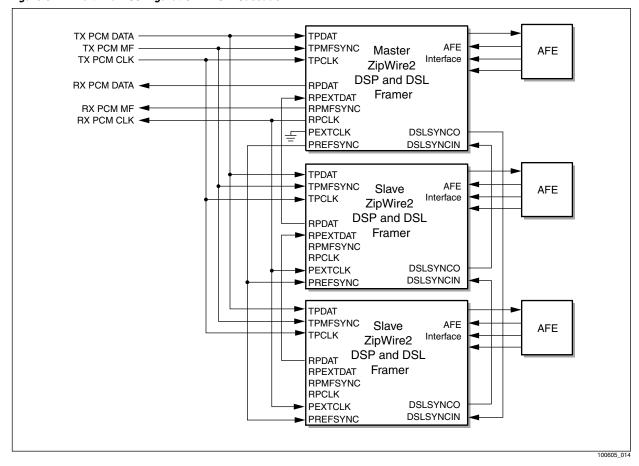

|         | 3.3   | Multi-Pair DSL Framer Configuration (Cascade Mode)                                                                                               |  |  |  |  |

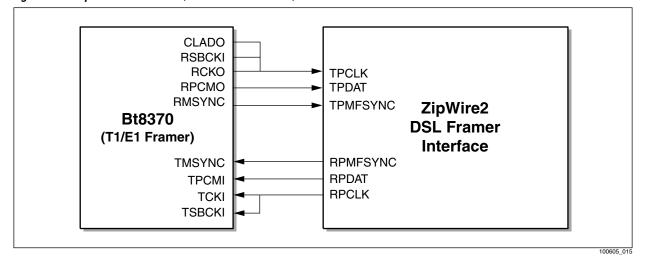

|         | 3.4   | ZipWire2 Transceiver/Framer to Bt8370 T1/E1 Interface                                                                                            |  |  |  |  |

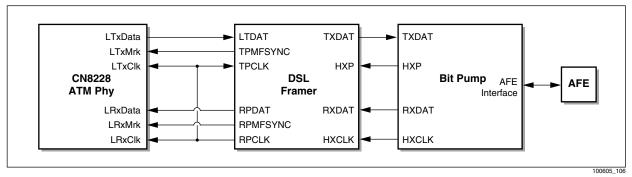

|         | 3.5   | DSL Framer to CN8228 (ATM Phy) Interface                                                                                                         |  |  |  |  |

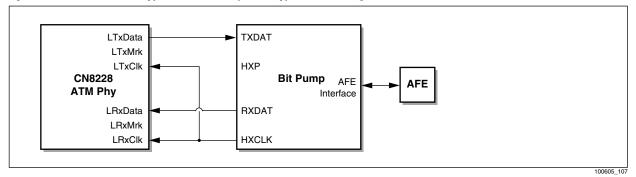

|         | 3.6   | DSL Framer Bypass to CN8228 (ATM Phy) Interface                                                                                                  |  |  |  |  |

|         | 3.7   | Dual Mode CN8228 (ATM Phy) Interface                                                                                                             |  |  |  |  |

|         | 3.8   | DSL Framer to MUSYCC Interface                                                                                                                   |  |  |  |  |

|         | 3.9   | DSL Framer Bypass to MUSYCC Interface                                                                                                            |  |  |  |  |

|         | 3.10  | Dual Mode MUSYCC Interface                                                                                                                       |  |  |  |  |

|         | 3.11  | Multiple ZipWire2 Devices to CN8228 or MUSYCC Interface                                                                                          |  |  |  |  |

|         | 3.12  | Deliverables3-183.12.1Customers who do not wish to modify 8051 code3-183.12.2Customers who wish to modify 8051 code to control other devices3-18 |  |  |  |  |

|         |       | 3.12.3 Customers who wish to modify low-level DSL Framer code                                                                                    |  |  |  |  |

| 4.0         | Buil | t-In 805 | 1 Core Detailed Description 4            | -1 |

|-------------|------|----------|------------------------------------------|----|

|             | 4.1  | Internal | 8051 Data Space Memory Map 4             | -2 |

|             | 4.2  | Internal | 8051 Interrupt Mapping                   | -3 |

|             | 4.3  | ZipWire  | 2 Transceiver Function Registers         | -4 |

|             | 4.4  | Configu  | ration Pins                              | -4 |

|             |      | 4.4.1    | 8051 Timer/Counter Description           | -5 |

|             | 4.5  | Internal | 8051 Communication Interfaces            | -6 |

|             |      | 4.5.1    | Master Bus Microprocessor Interface      |    |

|             |      | 4.5.2    | Host Port RAM Interface                  |    |

|             |      | 4.5.3    | RS232 Serial Interface                   |    |

|             |      | 4.5.4    | Group Talk Interface                     |    |

|             | 4.6  | Progran  | n RAM Download                           | -8 |

|             |      | 4.6.1    | Summary                                  |    |

|             |      | 4.6.2    | Download Description                     |    |

|             |      | 4.6.3    | Dip Switch #2—DEVADR and BOOTOP Pins     |    |

|             |      | 4.6.4    | Download Protocol Overview               |    |

|             |      | 4.6.5    | Download Times                           |    |

|             |      |          | 4.6.5.1 Host Port RAM Interface          |    |

|             |      |          | 4.6.5.2 Group Talk Interface             | 10 |

|             |      | 4.6.6    | Download and Device Validation           |    |

|             |      | 4.6.7    | Download Group Master Device             |    |

|             |      | 4.6.8    | Download Group Slave Device              | 11 |

|             |      | 4.6.9    | Download Single Processor Configuration  | 12 |

|             |      | 4.6.10   | Download Dual Processor Configuration    | 13 |

|             |      |          | 4.6.10.1 Redundant Download Group Master | 14 |

|             |      |          | 4.6.10.2 Device Uniqueness               | 14 |

|             |      |          | 4.6.10.3 Group Uniqueness                | 14 |

|             |      | 4.6.11   | Download API Commands                    | 15 |

|             |      |          | 4.6.11.1 Boot Code API Commands          | 15 |

|             |      |          | 4.6.11.2 Operational API Commands4-      | 15 |

|             |      |          | 4.6.11.3 Program RAM Checksum            | 15 |

|             |      | 4.6.12   | Download Examples                        | 16 |

| 5.0         | 7in\ | Nire2 DS | SP Detailed Description 5                | -1 |

| J. <b>J</b> | •    | 7inWire  | •                                        | _1 |

| Zip\ | Wire2 F | ramer De           | tailed Description                               | 6-1  |

|------|---------|--------------------|--------------------------------------------------|------|

| 6.1  | Disting | juishing Fe        | atures                                           | 6-1  |

| 6.2  | Comm    | on Function        | ıs                                               | 6-2  |

|      | 6.2.1   | DATA FIF           | 0                                                | 6-2  |

| 6.3  | HDSL S  | Section            |                                                  | 6-2  |

|      | 6.3.1   |                    | IDSL Functions.                                  |      |

|      | 0.0     | 6.3.1.1            | CRC Generator                                    |      |

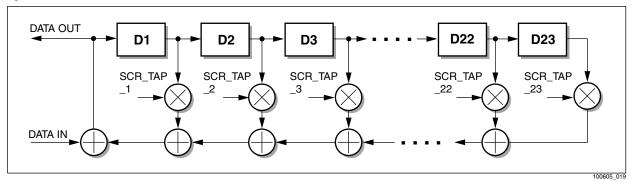

|      |         | 6.3.1.2            | Scrambler/ Descrambler                           |      |

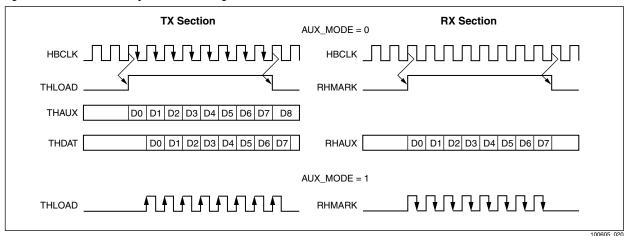

|      |         | 6.3.1.3            | Auxiliary Channel                                | 6-3  |

|      |         | 6.3.1.4            | RX DSL Reference Phase Measurement               | 6-3  |

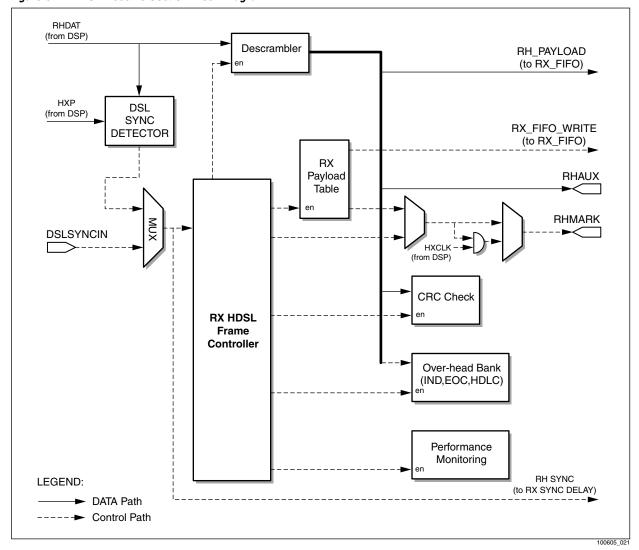

|      | 6.3.2   | HDSL Re            | ceiver Functionality                             | 6-4  |

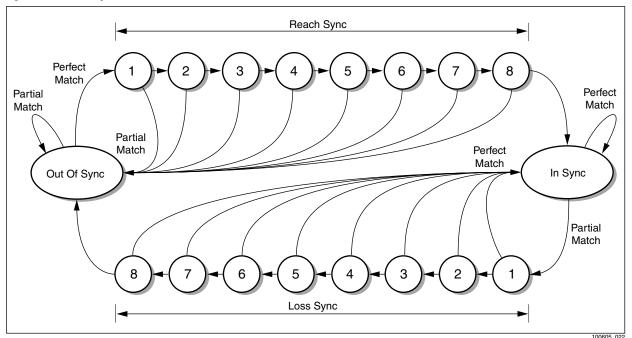

|      |         | 6.3.2.1            | DSL Sync Detector (DSD)                          |      |

|      |         | 6.3.2.2            | Tip/Ring Reversal Detection.                     |      |

|      |         | 6.3.2.3            | RX HDSL Payload Table                            |      |

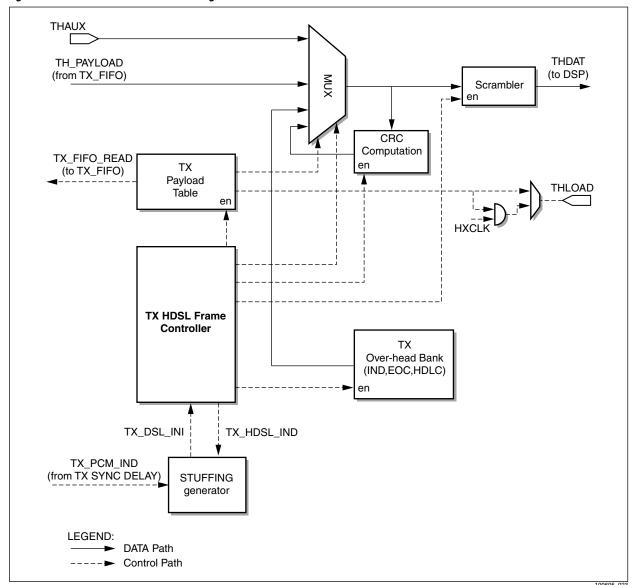

|      | 6.3.3   |                    | Insmitter Functionality.                         |      |

|      |         | 6.3.3.1            | Stuffing Generator                               | 6-6  |

| 6.4  | PCM S   | ection             |                                                  | 6-7  |

|      | 6.4.1   |                    | rface                                            |      |

|      | 6.4.2   | General F          | PCM Functions                                    |      |

|      |         | 6.4.2.1            | CRC Generator                                    |      |

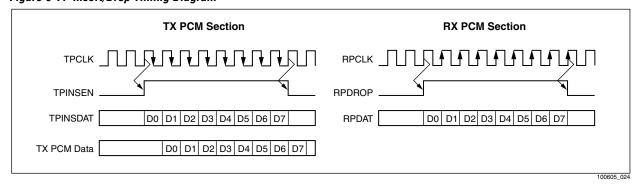

|      |         | 6.4.2.2            | Insert/Drop                                      |      |

|      |         | 6.4.2.3            | Overhead Handling                                |      |

|      |         | 6.4.2.4            | E1 Grooming                                      |      |

|      | 0.40    | 6.4.2.5            | MF Phase Measurement                             |      |

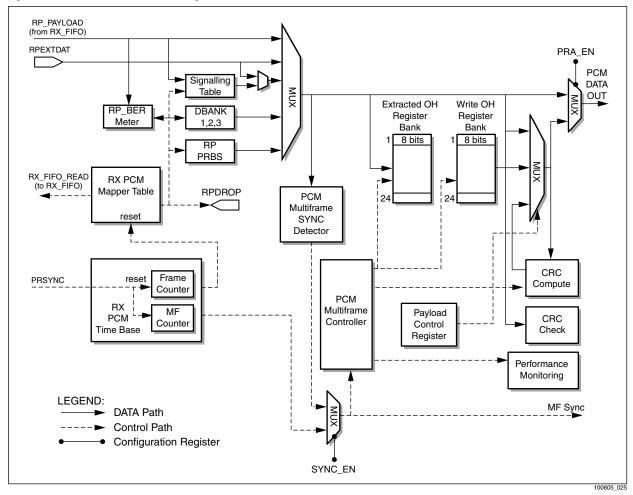

|      | 6.4.3   |                    | eiver                                            |      |

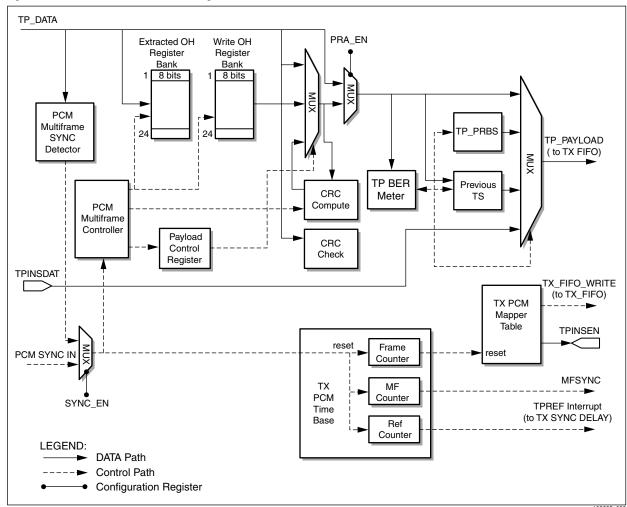

|      | 6.4.4   | 6.4.4.1            | nsmitter                                         |      |

|      |         |                    | •                                                |      |

| 6.5  |         | _                  | ics                                              |      |

|      | 6.5.1   |                    | nce Monitoring.                                  |      |

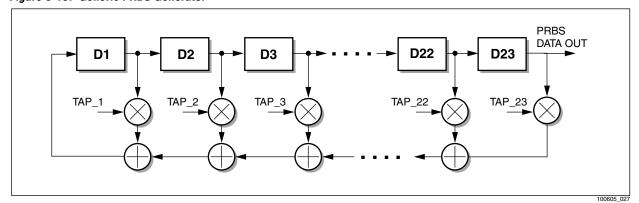

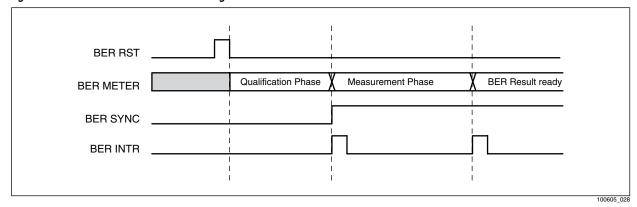

|      | 6.5.2   | PRBS and           | d BER Meter                                      | 6-11 |

| Har  | dware I | nterfaces          |                                                  | 7-1  |

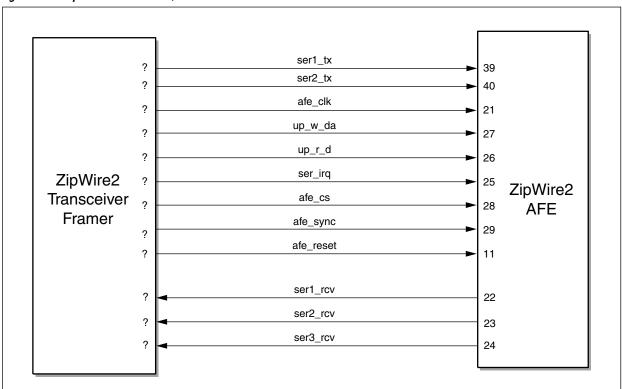

| 7.1  |         |                    | iver/Framer to AFE Interface                     |      |

|      |         |                    |                                                  |      |

| 7.2  |         |                    | e Interface                                      |      |

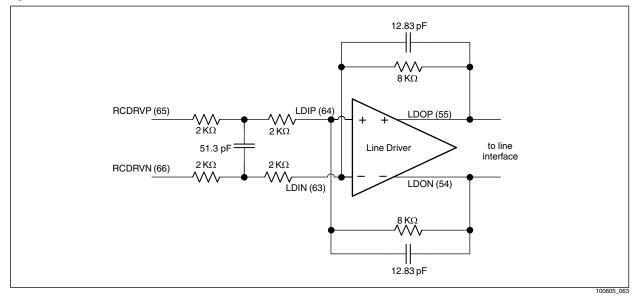

|      | 7.2.1   |                    | us Time Filter and Line Driver Control           |      |

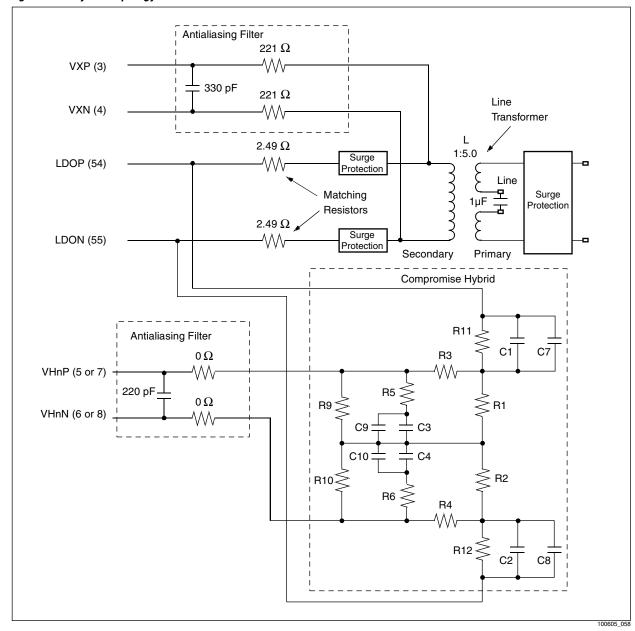

|      | 7.2.2   |                    | nise Hybrid, Matching Resistors, and Transformer |      |

|      |         | 7.2.2.1            | Compromise Hybrid                                |      |

|      |         | 7.2.2.2            | Impedance Matching Resistors                     |      |

|      |         | 7.2.2.3<br>7.2.2.4 | Transformer                                      |      |

|      | 7.2.3   |                    | otection                                         |      |

| 7.0  |         | •                  |                                                  |      |

| 7.3  | _       |                    | e and Compensation Circuitry                     |      |

| 7.4  |         |                    | terface (ZipWire2 Transceiver DSL Interface)     |      |

| 7.5  | Test ar | nd Diagnost        | ic Interface (JTAG)                              | 7-8  |

| 8.0  | Pin [ | Descriptions8-1                                                                                                                                                            |

|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

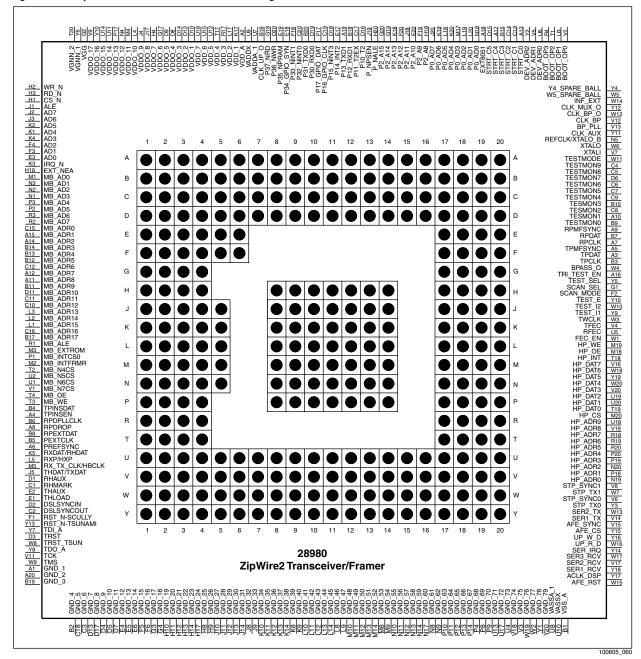

|      | 8.1   | ZipWire2 Pin Assignments       8-1         8.1.1 ZipWire2 Transceiver/Framer Pin Assignments       8-2         8.1.2 ZipWire2 Transceiver/Framer Pin Assignments       8-2 |

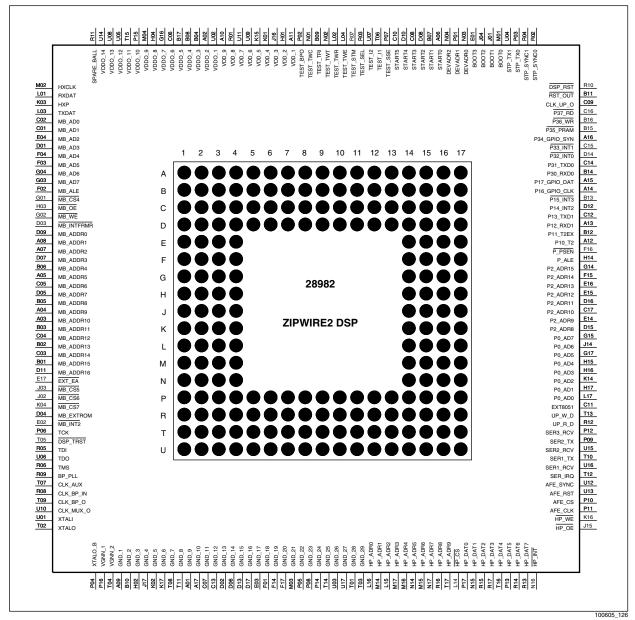

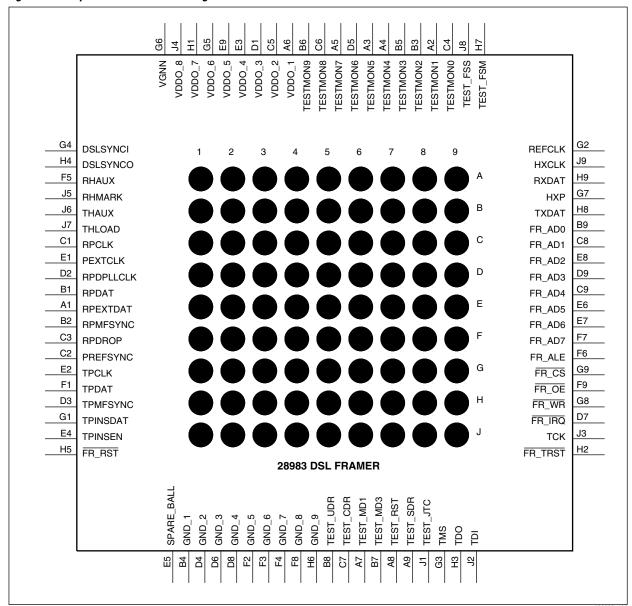

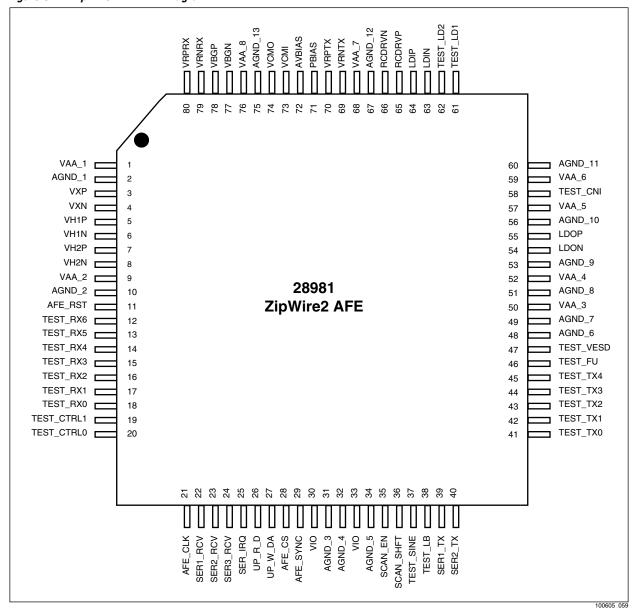

|      |       | 8.1.2ZipWire2 Transceiver Pin Assignments8-38.1.3ZipWire2 Framer Pin Assignments8-48.1.4ZipWire2 AFE Pin Assignments8-5                                                    |

|      | 8.2   | ZipWire2 Signal Descriptions8-68.2.1 ZipWire2 Transceiver/Framer Signal Descriptions8-68.2.2 ZipWire2 AFE Signal Descriptions8-15                                          |

| 9.0  | EVM   | <b>Specific</b>                                                                                                                                                            |

|      | 9.1   | <b>Bt8370 E1/T1 Framer</b> 9-2                                                                                                                                             |

|      | 9.2   | EVM LEDs and Miscellaneous Output                                                                                                                                          |

|      | 9.3   | EVM DIP Switches. 9-3                                                                                                                                                      |

| 10.0 | Soft  | vare Overview                                                                                                                                                              |

|      | 10.1  | Software Features 10-2                                                                                                                                                     |

| 11.0 | Emb   | edded 8051 Software Features                                                                                                                                               |

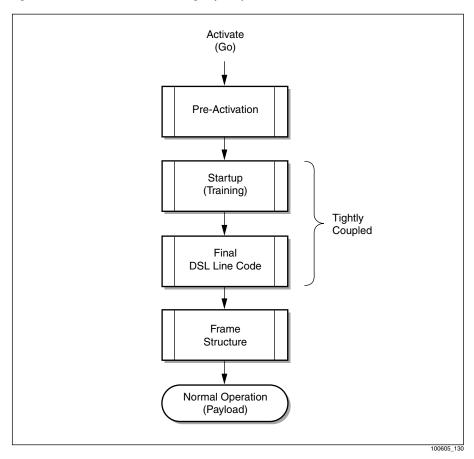

|      | 11.1  | Activating the ZipWire2 Modem                                                                                                                                              |

|      |       | 11.1.1 Activation State Manager (ASM)                                                                                                                                      |

|      |       | 11.1.2 Pre-Activation                                                                                                                                                      |

|      |       | 11.1.2.1 OPTIS (HDSL2 1T1) Pre-Activation                                                                                                                                  |

|      |       | 11.1.2.2 AutoBaud       11-2         11.1.2.3 G.hs       11-2                                                                                                              |

|      |       | 11.1.3 DSP Training                                                                                                                                                        |

|      |       | 11.1.4 DSL Line Coding                                                                                                                                                     |

|      |       | 11.1.5 Frame Format                                                                                                                                                        |

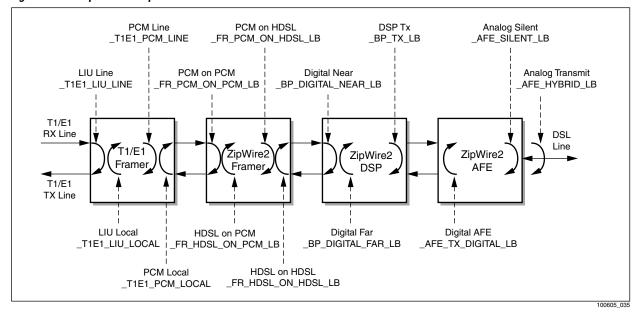

|      | 11.2  | <b>Loopbacks</b>                                                                                                                                                           |

|      | 11.3  | <b>BER Meters</b>                                                                                                                                                          |

|      |       | 11.3.1 DSL Framer Tx PCM BER Meter                                                                                                                                         |

|      |       | 11.3.2 DSL Framer Rx PCM BER Meter                                                                                                                                         |

|      |       | 11.3.3 Bit-Pump-Only BER Meter                                                                                                                                             |

|      | 11.4  | Performance Monitoring (Error History)                                                                                                                                     |

|      | 11.5  | DSL Framer Interrupt Handler                                                                                                                                               |

|      |       | 11.5.1 Sync Status       11-9         11.5.2 Error Status Reporting       11-9                                                                                             |

|      |       | 11.5.3 Tx/Rx FIFO Error Handling                                                                                                                                           |

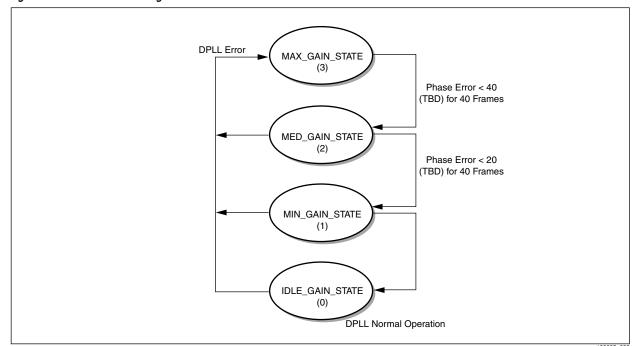

|      |       | 11.5.4 DPLL Error Handling                                                                                                                                                 |

|      |       | 11.5.5 Pair ID Termination (E1 Mode)                                                                                                                                       |

|      |       | 11.5.6 Indicator Bit Termination                                                                                                                                           |

|      | 11.6  | Dynamic Master Loop                                                                                                                                                        |

|      | 11.7  | Tip/Ring Reversal                                                                                                                                                          |

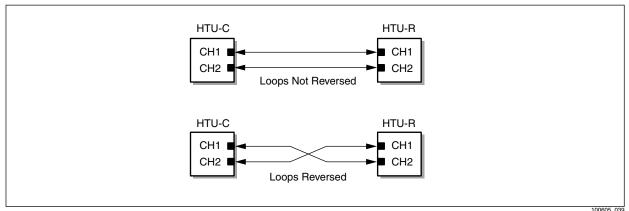

|      | 11.8  | Loop Reversal                                           | 1-12 |

|------|-------|---------------------------------------------------------|------|

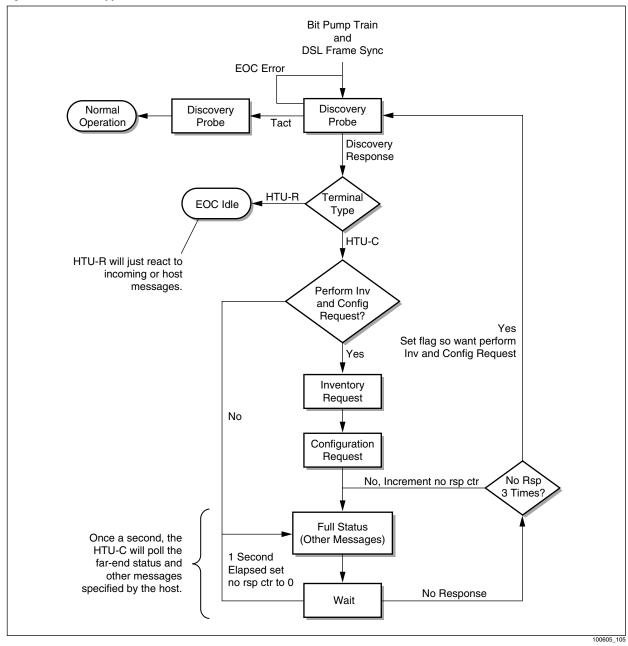

|      | 11.9  | Embedded Operation Channel (EOC) Operation              | 1-13 |

|      |       | 11.9.1 Feature Overview                                 | 1-13 |

|      |       | 11.9.2 Does Not Support                                 |      |

|      |       | 11.9.3 EOC General Overview                             |      |

|      |       | 11.9.4 EOC Frame Format                                 |      |

|      |       | 11.9.5 EOC Unit Addresses                               |      |

|      |       | 11.9.6 EOC Message IDs                                  |      |

|      | 11.10 | EOC Implementation Details                              |      |

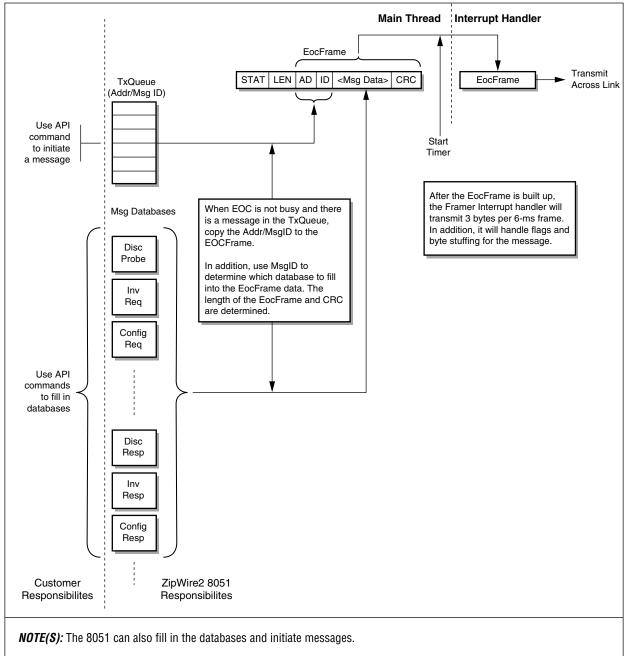

|      |       | 11.10.1 EOC Transmit                                    |      |

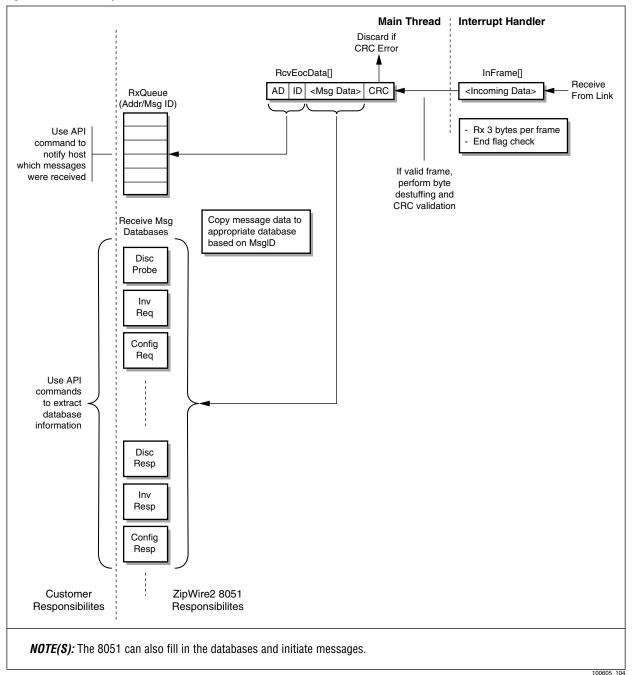

|      |       | 11.10.2 EOC Receive                                     |      |

|      |       | 11.10.3 EOC Transaction Time                            |      |

|      |       | 11.10.4 EOC Transaction Time-Out                        |      |

|      |       | 11.10.5.1 Auto-Response To Request Message              |      |

|      |       | 11.10.5.2 Auto-Trigger a Request Message                |      |

|      |       | 11.10.5.3 Notify Host That a Message Was Received       |      |

|      |       | 11.10.5.4 Notify Host When Error Is Detected            |      |

|      |       | 11.10.6 EOC Transmit Queue                              | 1-23 |

|      |       | 11.10.7 EOC Receive Queue                               |      |

|      |       | 11.10.8 EOC Proprietary Messages                        |      |

|      |       | 11.10.8.1 User-Defined Message Request – Message ID 112 |      |

|      |       | 11.10.8.2 User-Defined Message Response— Message ID 240 |      |

|      |       | 11.10.8.3 API Over EOC Request—Message ID 113           |      |

|      |       | 11.10.8.5 Redefining Proprietary Messages               |      |

|      |       | 11.10.9 EOC Application State Machine                   |      |

|      |       | 11.10.10 EOC API Commands                               |      |

|      | 11.11 | T1/E1 Framer and LIU Support                            | 1-28 |

|      |       |                                                         |      |

| 12.0 | Embe  | edded 8051 Code                                         | 12-1 |

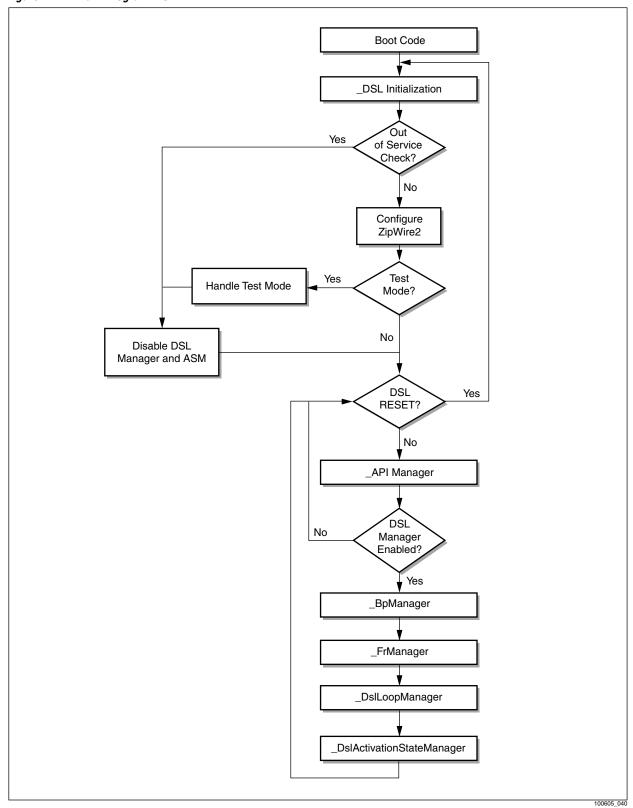

|      | 12.1  | Boot Code State                                         | 12-3 |

|      | 12.2  | DSL Initialization State                                | 12-3 |

|      | 12.3  | Out-Of-Service Check                                    | 12-3 |

|      | 12.4  |                                                         | 12-3 |

|      | 12.5  |                                                         | 12-4 |

|      | 12.6  |                                                         | 12-4 |

|      | 12.7  |                                                         | 12-4 |

|      |       | • • •                                                   | 12-4 |

|      | 12.8  |                                                         |      |

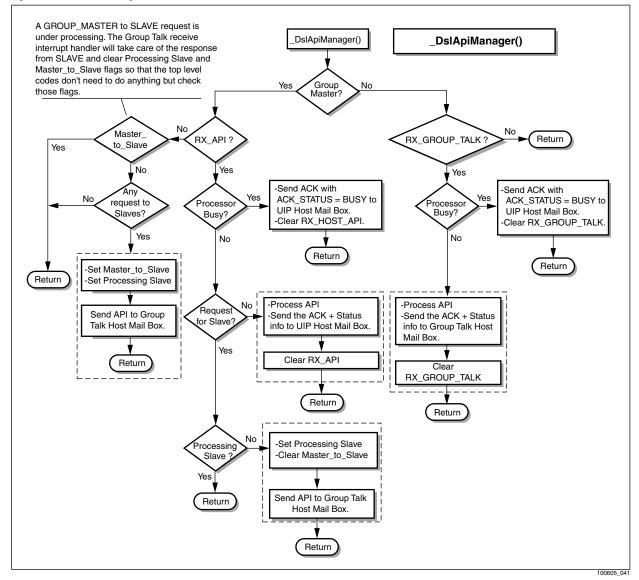

|      | 12.9  |                                                         | 12-7 |

|      |       |                                                         | 12-7 |

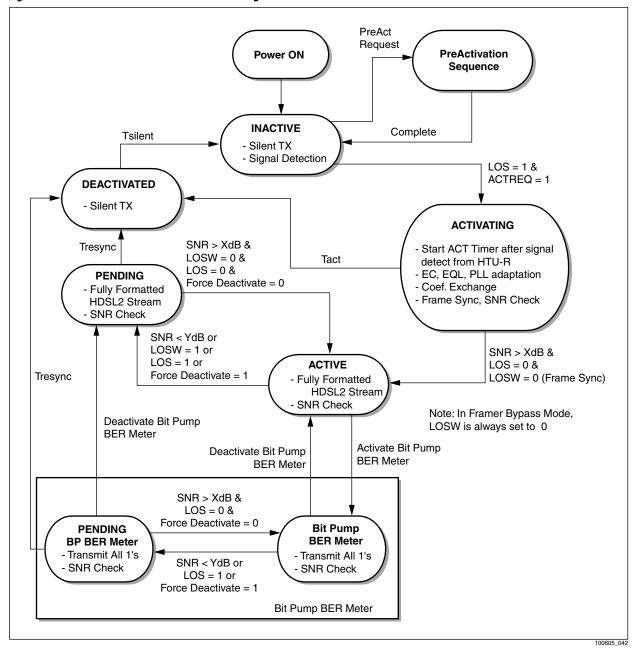

|      | 12.11 | HDSL2 Activation State Manager                          | 12-8 |

| 7. 117. 2 | TIDAT | 2/0D 01  | T .         | 1 🗖       |

|-----------|-------|----------|-------------|-----------|

| /inWire/  | HI)XI | 2/8/18/1 | Transceiver | and Frame |

|           |       |          |             |           |

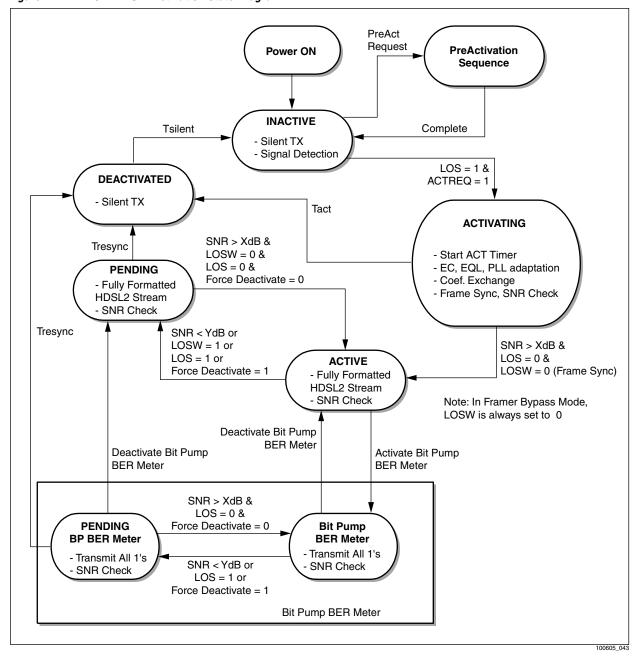

|      | 12.12 | 2 HDSL1 Activation State Manager  12.12.1 HTU-C Activation | 12-10 |

|------|-------|------------------------------------------------------------|-------|

| 13.0 | HDS   | SL2 Standards Compliance                                   | 13-1  |

|      | 13.1  | Bit-Level Mapping                                          | 13-1  |

|      |       | 13.1.1 Four-Level 2B1Q Mapping (HDSL1)                     |       |

|      |       | 13.1.2 Sixteen-Level Optis Mapping (HDSL2)                 |       |

| 14.0 | DSL   | Frame Structure                                            | 14-1  |

|      | 14.1  | Bypass DSL Frame Structure                                 |       |

|      | 14 2  | HDSL2 Configurations                                       | 14-1  |

|      |       | 14.2.1 HDSL2 1T1                                           |       |

|      |       | 14.2.2 HDSL2 _1E1                                          |       |

|      |       | 14.2.3 HDSL2—Single Pair.                                  |       |

|      | 14.3  | HDSL1 Configurations                                       | 14-5  |

|      |       | 14.3.1 HDSL1 _2T1                                          |       |

|      |       | 14.3.2 HDSL1_2E1                                           |       |

|      |       | 14.3.3 HDSL1_3E1                                           |       |

|      |       | 14.3.4 HDSL1_1T1                                           |       |

|      |       | 14.3.5 HDSL1_1E1                                           | 14-10 |

|      |       | 14.3.6 HDSL1_DSL_CUSTOM                                    | 14-10 |

| 15.0 | API:  | Microprocessor Communicator Channel Protocol               | 15-1  |

|      | 15.1  | API Message Time-Out                                       | 15-3  |

|      | 15.2  | API Master and Slave Implementation                        | 15-3  |

|      |       | 15.2.1 No Peer-to-Peer Protocol                            |       |

|      | 15.3  | API Message Structure                                      | 15-4  |

|      |       | 15.3.1 Incoming Message Structure                          | 15-4  |

|      |       | 15.3.2 Outgoing Message Structure                          | 15-4  |

|      |       | 15.3.3 Header Section–Destination Field                    | 15-5  |

|      |       | 15.3.3.1 Header Section-Opcode Field                       |       |

|      |       | 15.3.4 Header Section—Reserved Byte or ACK Status          |       |

|      |       | 15.3.4.1 Acknowledge Status Byte                           |       |

|      |       | 15.3.5 Header Section–Message Length Field                 |       |

|      |       | 15.3.6 Data Section–Data Parameter Field                   | 15-8  |

|      | 15.4  | Host Port RAM Interface Protocol                           | 15-9  |

|      |       | 15.4.1 INTR_HOST and INTR_8051 Registers                   |       |

|      |       | 15.4.2 Host Port Acknowledge Register                      |       |

|      |       | 15.4.3 Host Port Status Registers                          | 15-11 |

|      | 15.5  | •                                                          |       |

|      |       | 15.5.0.1 Host Processor Polling Method                     | 15-14 |

|      |       | 15.5.1 Multi Device System                                 |       |

|      | 15.6 | RS232 Serial Interface Protocol                 |                               |

|------|------|-------------------------------------------------|-------------------------------|

|      |      | 15.6.1 Host Processor to 8051 Processor Message | Structure                     |

|      |      |                                                 |                               |

|      |      | •                                               | Status Message Structure 15-1 |

|      |      | 15.6.4 RS232 Message Transfer Protocol          |                               |

|      | 15.7 | RS232 Checksum Function                         |                               |

|      |      | 15.7.1 RS232 Multi-Device System                |                               |

|      |      | 15.7.2 Group Talk Serial Interface Protocol     |                               |

|      |      | 15.7.3 Boot RAM Software Download               | 15-1                          |

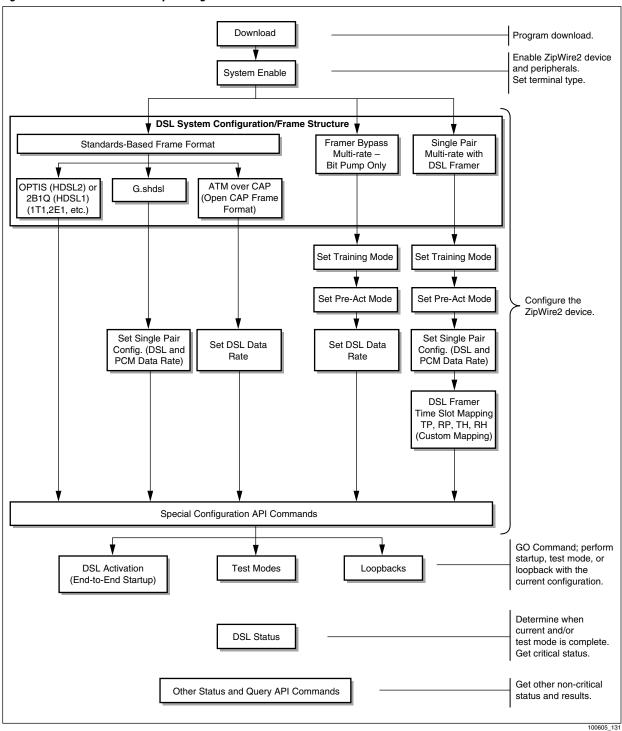

| 16.0 | ZipV | Vire2 API Configuration                         | 16-                           |

|      | 16.1 | API Command Sequencing                          | 16-                           |

|      | 16.2 | Indirect Configuration                          |                               |

|      | 10.2 |                                                 |                               |

|      |      |                                                 |                               |

|      |      |                                                 | 16-                           |

|      |      |                                                 |                               |

|      | 46.0 |                                                 |                               |

|      | 16.3 | Single Pair Configuration                       |                               |

| 17.0 | ZipV | Vire2 API Commands                              | 17-                           |

|      | 17.1 | API Commands: Quick Reference                   | 17-                           |

|      | 17.2 | API Command Set Documentation Convention        |                               |

|      |      | 17.2.1 API Command Names                        |                               |

|      | 17.3 | Level 1 API Commands                            | 17-                           |

|      |      |                                                 |                               |

|      |      | <del>-</del>                                    |                               |

|      |      | -                                               |                               |

|      |      |                                                 |                               |

|      |      | 17.3.5 DSL Pre-Activation Mode                  |                               |

|      |      | 17.3.6 DSL Startup Mode                         |                               |

|      |      | 17.3.6.1 Bit Pump Auto Tip/Ring Reversal.       |                               |

|      |      | 17.3.7 LOST Time (Tsilent) Period               |                               |

|      |      |                                                 |                               |

|      |      |                                                 |                               |

|      |      | 17.3.10 PCM Multi-Frame Length                  |                               |

|      |      | 17.3.11 Single Pair Configuration               |                               |

|      |      | 17.3.12 DSL Data Rate                           |                               |

|      |      | 17.3.13 DSL Status—Dynamic                      |                               |

|      |      | 17.3.14 DSL Status—Static                       |                               |

|      |      | 17.3.15 Versions                                |                               |

|      |      | 17.3.16 Line Attenuation.                       |                               |

|      |      | 17.3.17 Noise Margin                            |                               |

|      |      | 17.3.18 EOC Send Command                        |                               |

|      |      | 17.3.19 EOC Get Message Status                  |                               |

Х

|      | 17.3.20 | EOC Set Database Data                         | 17-32 |

|------|---------|-----------------------------------------------|-------|

|      |         | EOC Get Database Data                         |       |

|      | 17.3.22 | EOC Set Message Control                       | 17-33 |

|      |         | EOC Read Receive Queue                        |       |

|      | 17.3.24 | EOC Set Proprietary Length                    | 17-35 |

|      | 17.3.25 | Download Start (Length)                       | 17-35 |

|      | 17.3.26 | Download Data                                 | 17-36 |

|      | 17.3.27 | Download End (Checksum)                       | 17-36 |

|      | 17.3.28 | Download Slave                                | 17-37 |

| 17.4 | Level 2 | API Commands                                  | 17-38 |

|      | 17.4.1  | Read DSL Control Commands                     |       |

|      | 17.4.2  | Stage Number                                  |       |

|      | 17.4.3  | Read Configuration Pins                       |       |

|      | 17.4.4  | AFE Setting                                   |       |

|      | 17.4.5  | Analog Front End (AFE) Configuration          |       |

|      | 17.4.6  | DSL Force Deactivate                          |       |

|      | 17.4.7  | Transmit External Data                        |       |

|      | 17.4.8  | Test Modes                                    |       |

|      | 17.4.9  | Bit Pump Transmit Isolated Pulses Test Mode   |       |

|      | 17.4.10 | Bit Pump Transmit Fixed Pattern Test Mode     |       |

|      |         | Loopbacks                                     |       |

|      |         | Bit Pump BER Meter State                      |       |

|      | 17.4.13 | Bit Pump BER Meter Results                    | 17-50 |

|      | 17.4.14 | ERLE Test Mode                                | 17-52 |

|      | 17.4.15 | ERLE Results                                  | 17-53 |

|      | 17.4.16 | Auxiliary CLK Select                          | 17-54 |

|      | 17.4.17 | PCM Clock Configuration                       | 17-54 |

|      | 17.4.18 | DSL Framer Transmit PCM BER Meter Results     | 17-55 |

|      | 17.4.19 | DSL Framer Receive PCM BER Meter Results      | 17-57 |

|      | 17.4.20 | Transmit PCM BER State                        | 17-58 |

|      | 17.4.21 | Receive PCM BER State                         | 17-58 |

|      | 17.4.22 | PRBS Configure                                | 17-59 |

|      | 17.4.23 | Fill Pattern (CONST_FILL)                     | 17-60 |

|      | 17.4.24 | Data Bank Contents                            | 17-61 |

|      | 17.4.25 | Transmit PCM Mapper Value                     | 17-62 |

|      | 17.4.26 | Transmit PCM Mapper Write                     | 17-63 |

|      | 17.4.27 | Receive PCM Mapper Value                      | 17-63 |

|      | 17.4.28 | Receive PCM Mapper Write                      | 17-64 |

|      | 17.4.29 | Transmit HDSL Mapper Value                    | 17-65 |

|      | 17.4.30 | Transmit HDSL Mapper Write                    | 17-66 |

|      | 17.4.31 | Receive HDSL Mapper Value                     | 17-66 |

|      |         | 17.4.31.1 Number of Time Slots                | 17-67 |

|      | 17.4.32 | Receive HDSL Mapper Write                     | 17-67 |

|      | 17.4.33 | Clear ZipWire2 Error Counters                 | 17-68 |

|      | 17.4.34 | Read ZipWire2 Operational Error Counters      | 17-69 |

|      | 17.4.35 | Read ZipWire2 HDSL Performance Error Counters | 17-70 |

|      | 17.4.36  | Read ZipWire2 PCM Performance Error Counters    | . 17-7 |

|------|----------|-------------------------------------------------|--------|

|      |          | Read ZipWire2 System Performance Error Counters |        |

|      |          | Available Seconds and Total Seconds             |        |

|      |          | Inject DSL CRC Error                            |        |

|      |          | Set CRC/FEBE Error History State                |        |

|      |          | Query CRC/FEBE History Interval In-Progress     |        |

|      |          | CRC Error History at Interval 1                 |        |

|      |          | CRC Error History at Interval 2                 |        |

|      |          | CRC Error History at Interval 3                 |        |

|      |          | FEBE Error History at Interval 1                |        |

|      |          | FEBE Error History at Interval 2                |        |

|      |          | FEBE Error History at Interval 3                |        |

| 17.5 |          | API Commands                                    |        |

| 17.3 | 17.5.1   | Signal Level Meter                              |        |

|      | 17.5.1   | Timing Recovery Offset                          |        |

|      | 17.5.2   | Bit Pump Reverse Tip/Ring                       |        |

|      | 17.5.3   | Scrambler/Descrambler Configuration.            |        |

|      | 17.5.4   | Write AFE Transmit Gain.                        |        |

|      | 17.5.6   | Read AFE Transmit Gain                          |        |

|      | 17.5.7   | DSL Framer Transmit Path Reset                  |        |

|      | 17.5.7   | DSL Framer Receive Path Reset                   |        |

|      | 17.5.9   | DSL Framer—HDSL Configuration                   |        |

|      |          | Mask Host Port Interrupt (INTR_HOST)            |        |

|      |          | DSL Framer Auto Water Level                     |        |

|      |          | DSL Framer Transmit Water Level                 |        |

|      |          | DSL Framer Receive Water Level                  |        |

|      |          |                                                 |        |

|      |          | DSL Framer DPLL Clock Generator                 |        |

| 17.6 |          | rite Register Commands                          |        |

|      | 17.6.1   | Write Register                                  |        |

|      | 17.6.2   | Read Register                                   |        |

|      | 17.6.3   | Write AFE Register                              |        |

|      | 17.6.4   | Read AFE Register                               | . 17-9 |

| 17.7 | T1/E1 Fi | ramer Commands                                  | 17-10  |

|      | 17.7.1   | T1/E1 Framer Configure                          | 17-10  |

|      | 17.7.2   | T1/E1 Framer Frame Format                       | 17-10  |

|      | 17.7.3   | T1/E1 Framer Transmit AIS                       | 17-10  |

|      | 17.7.4   | T1/E1 Framer Output Mode                        | 17-10  |

|      | 17.7.5   | T1/E1 Framer Receive Termination                | 17-10  |

|      | 17.7.6   | T1/E1 Framer Loopbacks                          | 17-10  |

|      | 17.7.7   | T1/E1 Read Framer Control Commands              | 17-10  |

|      | 17.7.8   | T1/E1 Framer Versions                           | 17-10  |

| 17.8 | EVM Sn   | ecific Commands                                 | 17-10  |

|      | 17.8.1   | EVM Set LED Bank                                |        |

|      | 17.8.2   | EVM Set Miscellaneous Output                    |        |

|      | 17.8.3   | EVM LED Update State                            |        |

|      | 17.8.4   | EVM LED and DIP Switch Status.                  |        |

|      |          |                                                 |        |

| 18.0  | Elect   | trical an | d Mechanical Specifications                                 | 18-1  |

|-------|---------|-----------|-------------------------------------------------------------|-------|

|       | 18.1    | Specific  | ations for the ZipWire2 Transceiver/Framer and ZipWire2 AFE | 18-1  |

|       |         | 18.1.1    | Recommended Operating Conditions                            |       |

|       |         | 18.1.2    | Absolute Maximum Ratings                                    | 18-2  |

|       | 18.2    | Thermal   | Characteristics                                             | 18-3  |

|       |         | 18.2.1    | ZipWire2 AFE                                                | 18-3  |

|       |         | 18.2.2    | ZipWire2 Transceiver                                        | 18-3  |

|       |         | 18.2.3    | ZipWire2 Framer                                             | 18-3  |

|       |         | 18.2.4    | ZipWire2 Transceiver/Framer                                 |       |

|       | 18.3    | Specific  | ations for ZipWire2 Transceiver/Framer Only                 | 18-4  |

|       |         | 18.3.1    | Power Dissipation                                           | 18-4  |

|       |         | 18.3.2    | DC Characteristics                                          | 18-4  |

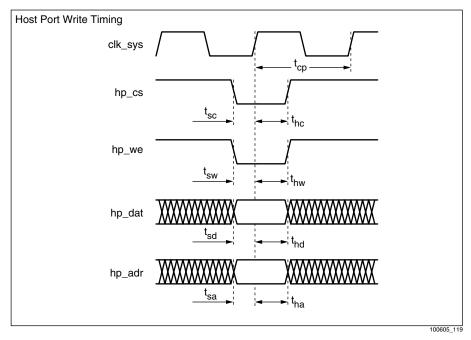

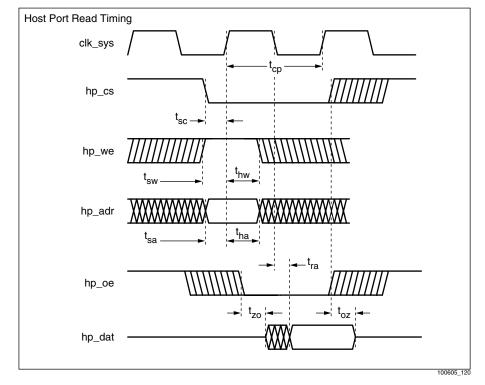

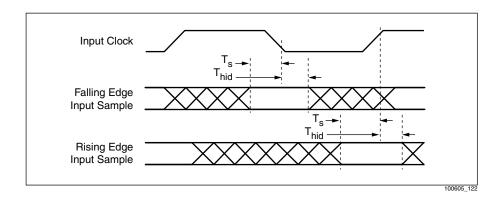

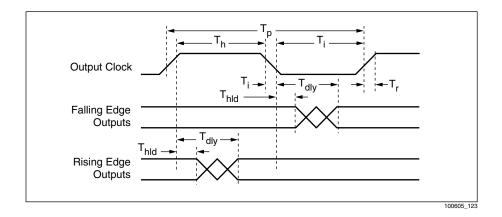

|       |         | 18.3.3    | Host Port RAM Interface Timing                              | 18-5  |

|       |         | 18.3.4    | Master Bus Interface Timing                                 |       |

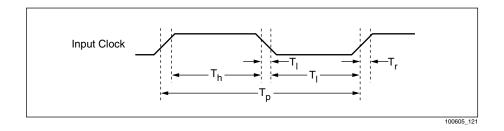

|       |         | 18.3.5    | DSL Framer Timing Requirements                              | 18-7  |

|       |         | 18.3.6    | DSL Framer Switching Characteristics                        |       |

|       | 18.4    | Specific  | ations for ZipWire2 AFE Only                                | 18-9  |

|       |         | 18.4.1    | Power Dissipation                                           |       |

|       |         | 18.4.2    | DC Characteristics                                          | 18-9  |

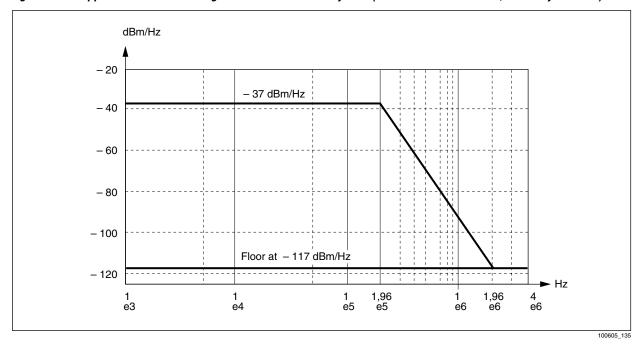

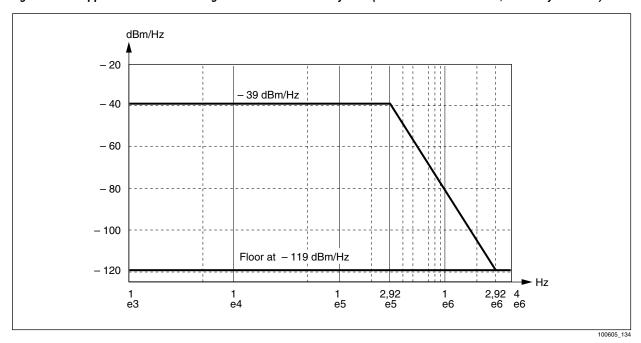

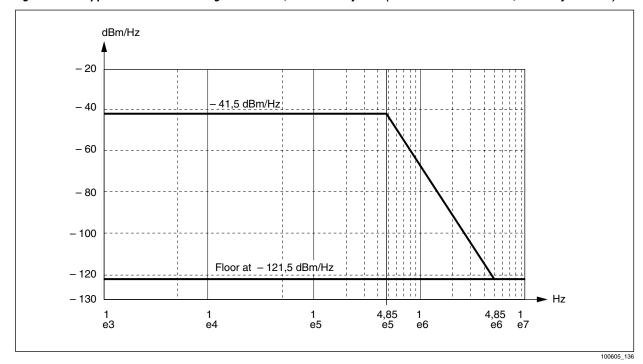

|       |         | 18.4.3    | PSD Specifications                                          | 18-10 |

|       |         |           | 18.4.3.1                                                    | 18-10 |

|       |         |           | 18.4.3.2                                                    | 18-11 |

|       |         |           | 18.4.3.3                                                    | 18-11 |

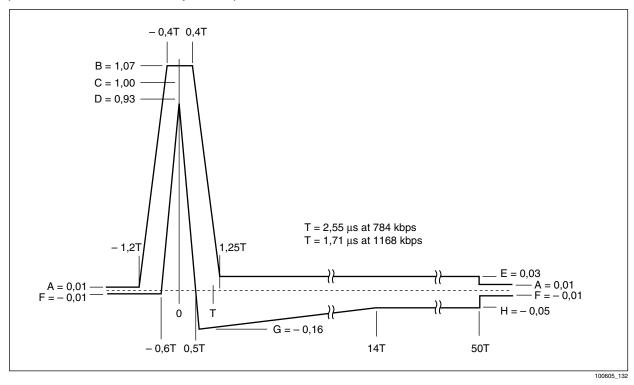

|       |         | 18.4.4    | Pulse Template Specifications                               | 18-12 |

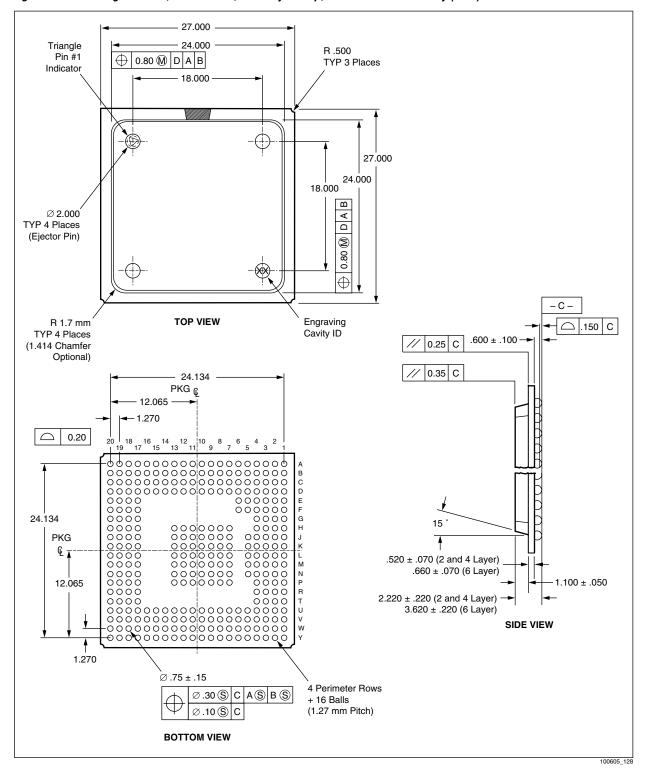

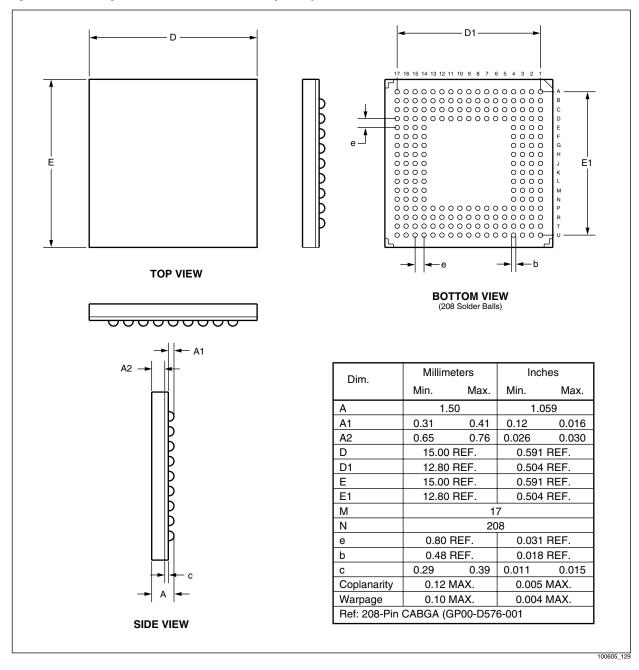

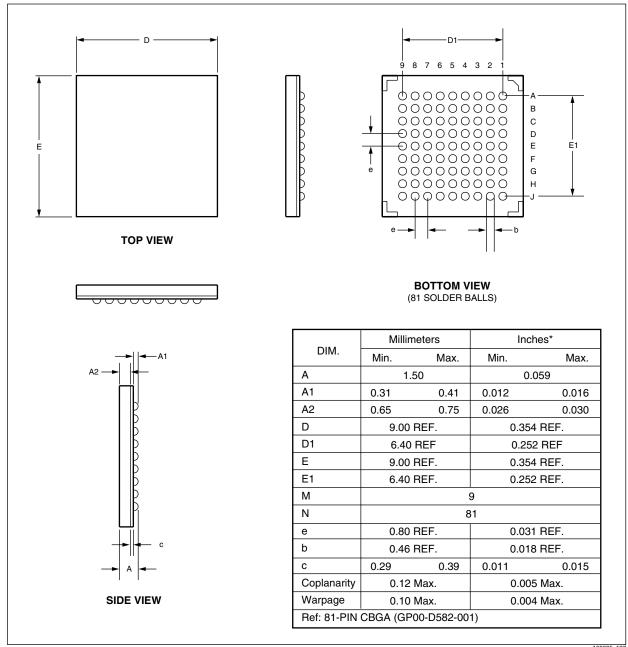

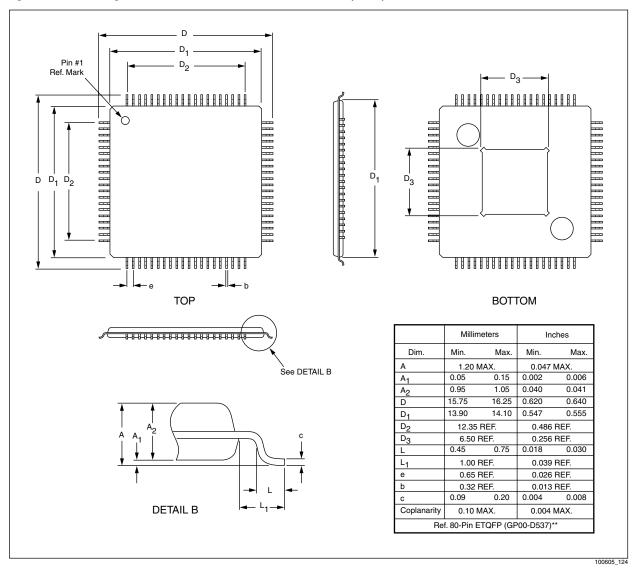

|       | 18.5    | Mechani   | ical Specifications                                         | 18-14 |

| Annen | ıdix Δ· | Acronvi   | ms and Ahhreviations                                        | Δ-1   |

# **List of Figures**

| Figure 2-1.  | High-Level Functional Diagram                                   | 2-1  |

|--------------|-----------------------------------------------------------------|------|

| Figure 2-2.  | ZipWire2 Transceiver/Framer Detailed Block Diagram              | 2-3  |

| Figure 2-3.  | ZipWire2 Transceiver/DSP Detailed Block Diagram                 | 2-4  |

| Figure 2-4.  | DSL Framer Detailed Block Diagram                               | 2-6  |

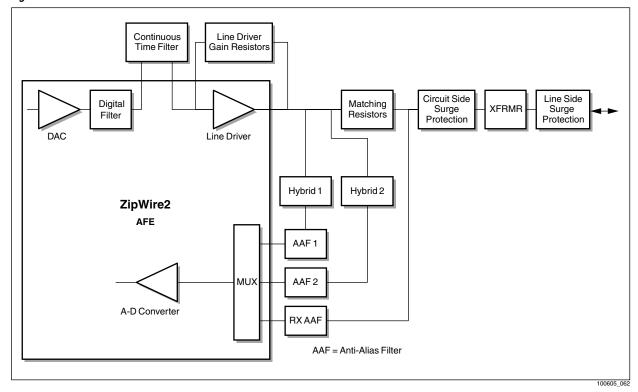

| Figure 2-5.  | ZipWire2 AFE Block Diagram                                      | 2-7  |

| Figure 2-6.  | Detailed Transmit Data Path Block Diagram                       | 2-8  |

| Figure 2-7.  | Detailed Receive Data Path Block Diagram                        | 2-9  |

| Figure 3-1.  | Single Pair Hardware Configuration                              | 3-1  |

| Figure 3-2.  | Multi-Pair Hardware Configuration                               | 3-2  |

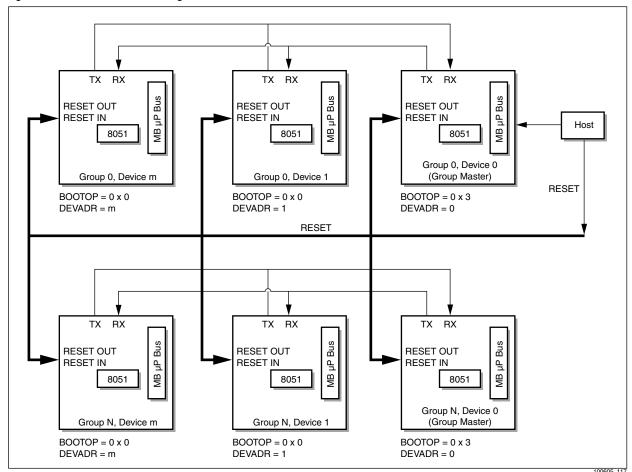

| Figure 3-3.  | Group Master/Group Slave Multi-Pair Hardware Configuration      | 3-3  |

| Figure 3-4.  | Master Multi-Pair Hardware Configuration                        | 3-4  |

| Figure 3-5.  | Redundant Group Master Multi-Pair Hardware Configuration        | 3-5  |

| Figure 3-6.  | Multi-Pair Configuration—PCM Bused                              | 3-7  |

| Figure 3-7.  | Multi-Pair Configuration—PCM Cascade                            | 3-8  |

| Figure 3-8.  | ZipWire2 Transceiver/Framer to Bt8370 T1/E1 Interface           | 3-9  |

| Figure 3-9.  | DSL Framer to CN8228 (ATM Phy) Interface Diagram                | 3-10 |

| Figure 3-10. | DSL Framer Bypass to CN8228 (ATM Phy) Interface Diagram         | 3-11 |

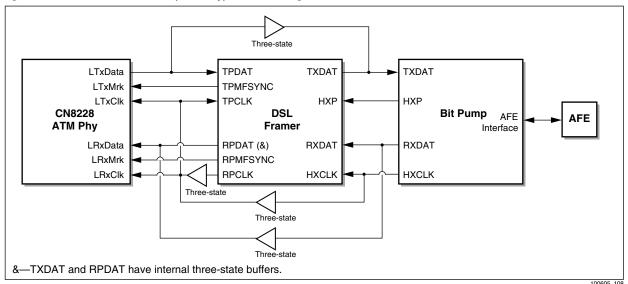

| Figure 3-11. | Dual Mode CN8228 (ATM Phy) Interface Diagram                    | 3-12 |

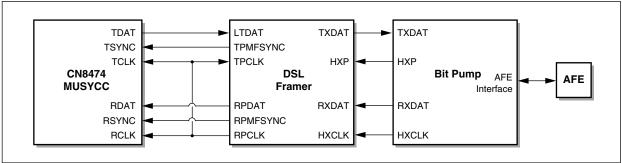

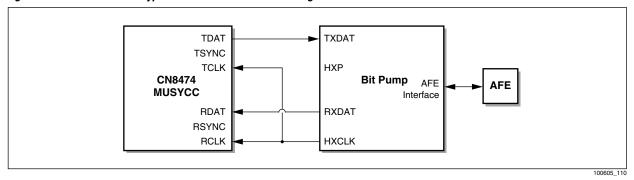

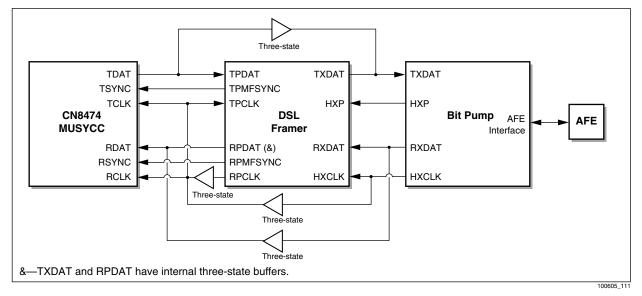

| Figure 3-12. | DSL Framer to MUSYCC Interface Diagram                          | 3-13 |

| Figure 3-13. | DSL Framer Bypass to MUSYCC Interface Diagram                   | 3-14 |

| Figure 3-14. | Dual Mode MUSYCC Interface Diagram                              | 3-15 |

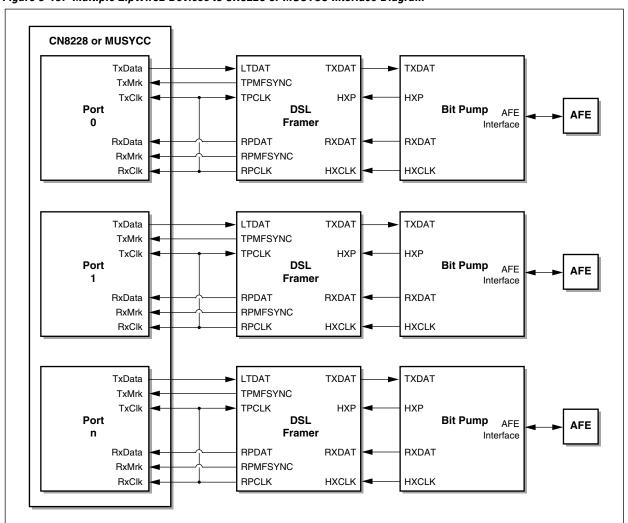

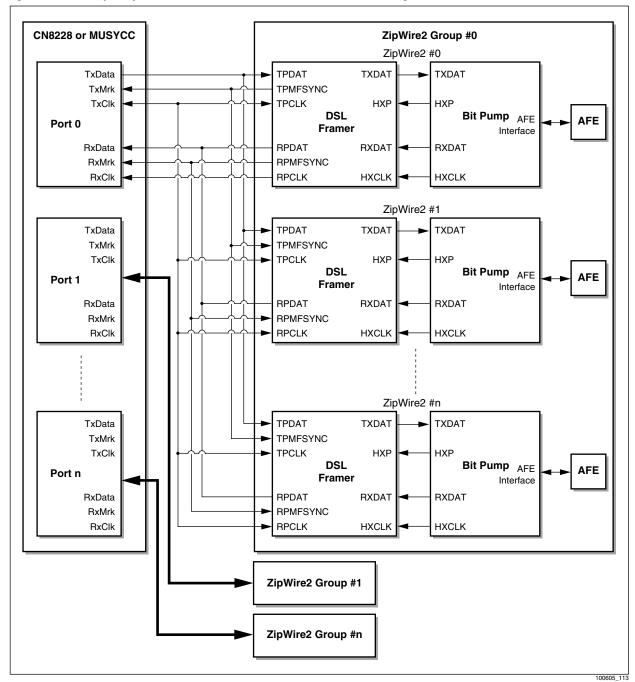

| Figure 3-15. | Multiple ZipWire2 Devices to CN8228 or MUSYCC Interface Diagram | 3-16 |

| Figure 3-16. | Multiple ZipWire2 Devices to CN8228 or MUSYCC Interface Diagram | 3-17 |

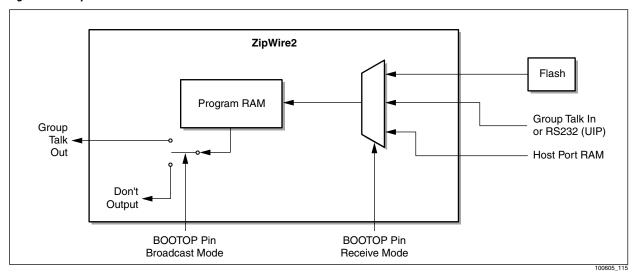

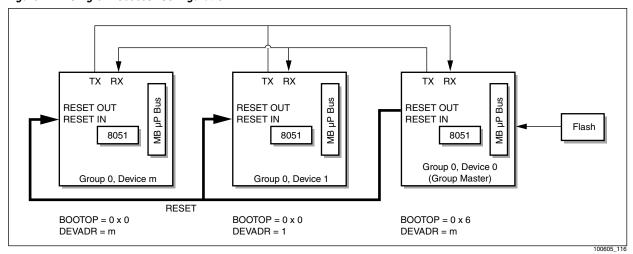

| Figure 4-1.  | ZipWire2 PRAM Download Overview                                 | 4-9  |

| Figure 4-2.  | Single Processor Configuration                                  | 4-12 |

| Figure 4-3.  | Host Processor Configuration                                    | 4-13 |

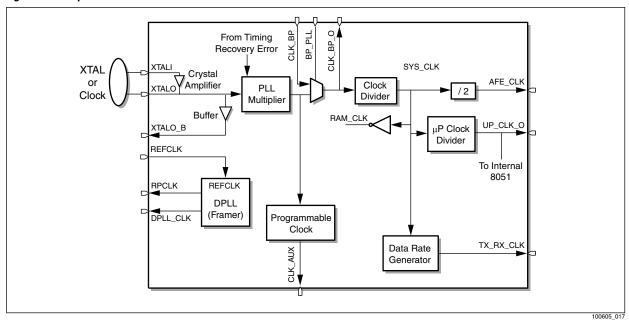

| Figure 5-1.  | ZipWire2 Clocks                                                 | 5-1  |

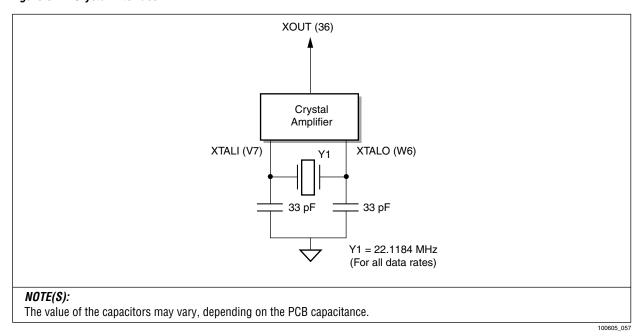

| Figure 5-2.  | Crystal Interface                                               | 5-2  |

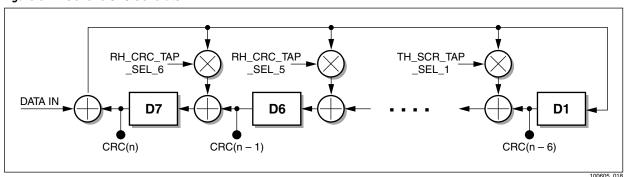

| Figure 6-1.  | Generic CRC Generator                                           | 6-2  |

| Figure 6-2.  | Generic Scrambler Generator                                     | 6-3  |

| Figure 6-3.  | HDSL Auxiliary Channel Timing.                                  | 6-3  |

| Figure 6-4.  | HDSL Receive Section Block Diagram                              | 6-4  |

| Figure 6-5.  | DSD Synchronization State Machine                               | 6-5  |

| Figure 6-6.  | HDSL TX Section Block Diagram                                   | 6-6  |

| Figure 6-7.  | Insert/Drop Timing Diagram                                      | 6-7  |

| Figure 6-8.  | PCM Receiver Block Diagram                                      | 6-9  |

| Figure 6-9.  | PCM Transmitter Block Diagram                                   | 6-10 |

| Figure 6-10. | Generic PRBS Generator                                          | 6-11 |

| Figure 6-11. | PRBS and BER Meter Timing                                       | 6-12 |

| Figure 7-1.  | ZipWire2 Transceiver/Framer to AFE Interface                                                                              | 7-1     |

|--------------|---------------------------------------------------------------------------------------------------------------------------|---------|

| Figure 7-2.  | DSL Transmission Line Interface                                                                                           | 7-2     |

| Figure 7-3.  | Continuous Time Filter and Line Driver Control                                                                            | 7-3     |

| Figure 7-4.  | Hybrid Topology                                                                                                           | 7-4     |

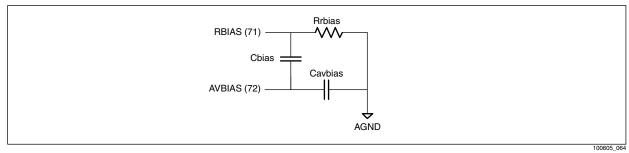

| Figure 7-5.  | ZipWire2 AFE Bias Current Network                                                                                         | 7-6     |

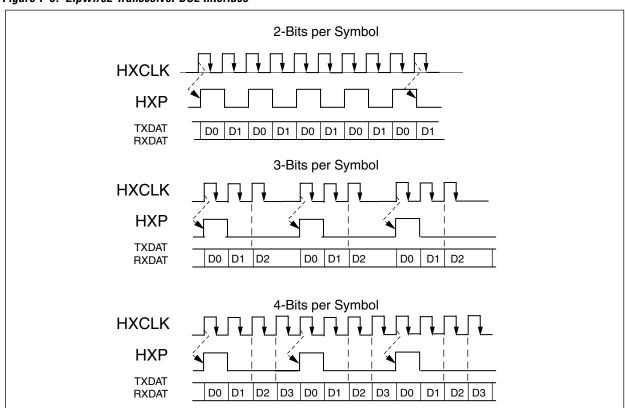

| Figure 7-6.  | ZipWire2 Transceiver DSL Interface                                                                                        | 7-7     |

| Figure 8-1.  | ZipWire2 Transceiver/Framer Pin Assignments                                                                               | 8-2     |

| Figure 8-2.  | ZipWire2 Transceiver Pin Assignments                                                                                      | 8-3     |

| Figure 8-3.  | ZipWire2 Framer Pin Assignments                                                                                           | 8-4     |

| Figure 8-4.  | ZipWire2 AFE Pin Diagram                                                                                                  | 8-5     |

| Figure 9-1.  | EVM Block Diagram                                                                                                         | 9-1     |

| Figure 10-1. | Software Overview                                                                                                         | 10-1    |

| Figure 11-1. | Activation State Manager (ASM) Overview                                                                                   | 11-2    |

| Figure 11-2. | ZipWire2 Loopbacks                                                                                                        | 11-4    |

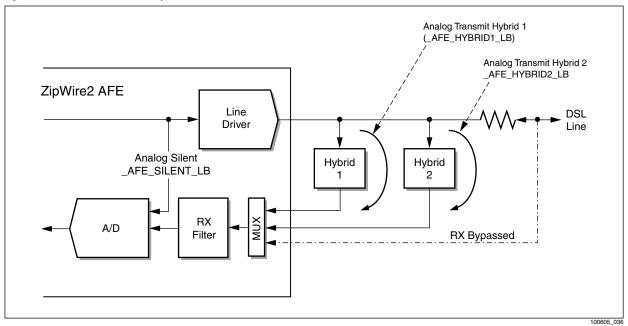

| Figure 11-3. | Detailed AFE Loopbacks                                                                                                    | 11-5    |

| Figure 11-4. | CRC and FEBE Error Records at Three Time Intervals                                                                        | 11-7    |

| Figure 11-5. | DPLL State Diagram                                                                                                        | . 11-10 |

| Figure 11-6. | Loop Reversal Definition                                                                                                  | . 11-12 |

| Figure 11-7. | EOC Implementation Details—Transmit                                                                                       | . 11-19 |

| Figure 11-8. | EOC Implementation Details—Receive                                                                                        | . 11-21 |

| Figure 11-9. | EOC Application State Machine                                                                                             | . 11-27 |

| Figure 12-1. | Main Program Flow                                                                                                         | 12-2    |

| Figure 12-2. | API Manager Flow                                                                                                          | 12-6    |

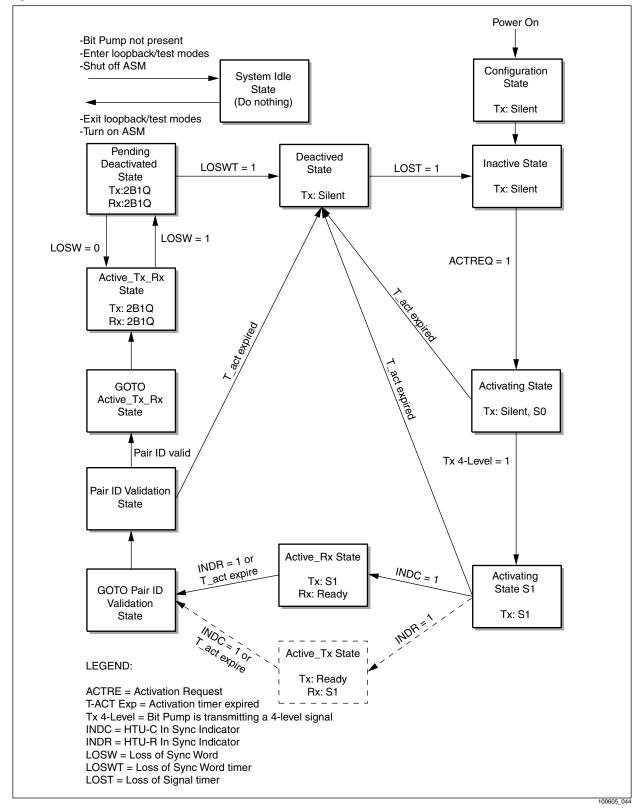

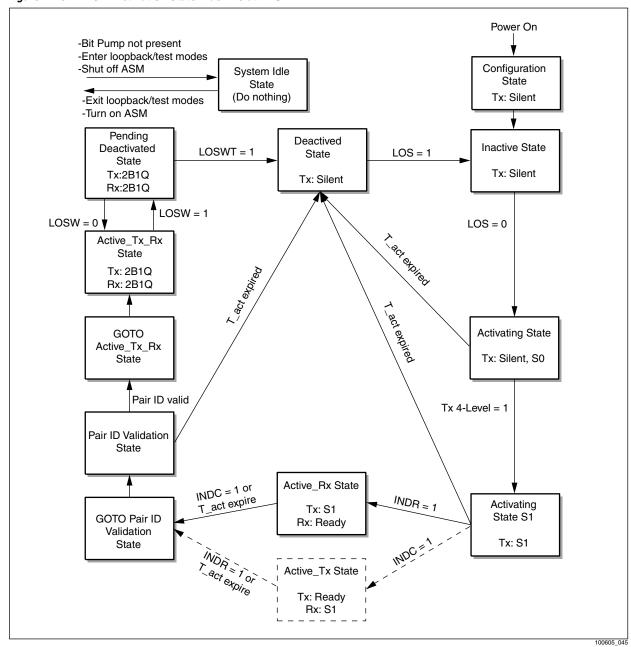

| Figure 12-3. | HDSL2 HTU-C Activation State Diagram                                                                                      | 12-8    |

| Figure 12-4. | HDSL2 HTU-R Activation State Diagram                                                                                      | 12-9    |

| Figure 12-5. | HDSL1 Activation State Machine at HTU-C                                                                                   | . 12-11 |

| Figure 12-6. | HDSL1 Activation State Machine at HTU-R                                                                                   | . 12-12 |

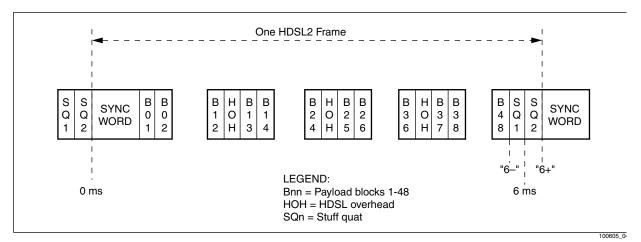

| Figure 14-1. | HDSL2 Frame Structure                                                                                                     | 14-3    |

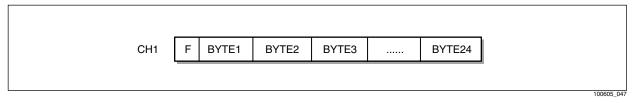

| Figure 14-2. | Payload Block Structure for 1T1 Application                                                                               | 14-3    |

| Figure 14-3. | Payload Block Structure for 1E1 Application                                                                               | 14-4    |

| Figure 14-4. | HDSL1 Frame Structure                                                                                                     | 14-6    |

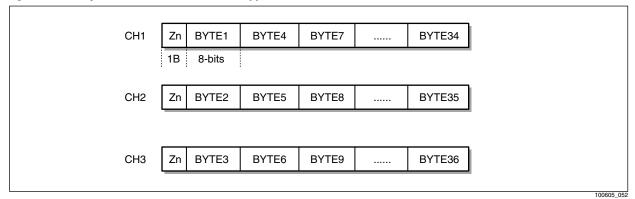

| Figure 14-5. | Payload Block Structure for 2T1 Application                                                                               | 14-7    |

| Figure 14-6. | Payload Block Structure for 2E1 Application                                                                               | 14-8    |

| Figure 14-7. | Payload Block Structure for 3E1 Application                                                                               | 14-9    |

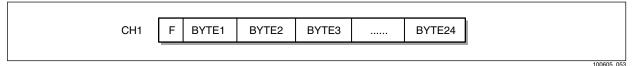

| Figure 14-8. | Payload Block Structure for 1T1 Application                                                                               | . 14-10 |

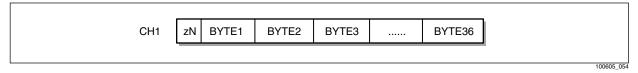

| Figure 14-9. | Payload Block Structure for 1E1 Application                                                                               | . 14-10 |

| Figure 15-1. | Communication Channel Protocols                                                                                           | 15-2    |

| Figure 16-1. | API Command Sequencing                                                                                                    | 16-2    |

| Figure 18-1. | Host Port Interface Timing Diagrams                                                                                       | 18-5    |

| Figure 18-2. | Transmit Pulse Template for Two- and Three-Pair Systems; Normalized Pulse Mask (Source ETSI TS 101 135, Formerly ETR 152) | 18-10   |

| Figure 18-3. | Transmit Pulse Template for One-Pair Systems (Source ETSI TS 101 135,                                                     | . 10-10 |

| riguio 10 0. | Formerly ETR 152)                                                                                                         | . 18-11 |

| Figure 18-4. | Upper Bound of the Average PSD of a 392 kbaud System (Source ETSI TS 101 135,                                             |         |

|              | Formerly ETR 152)                                                                                                         | . 18-12 |

| Figure 18-5. | Upper Bound of the Average PSD of a 584 kbaud System (Source ETSI TS 101 135, Formerly ETR 152)                           | . 18-12 |

CN8980 List of Figures

| ZipWire2 HDSL. | 2/SDSL Trans | sceiver an | d Framer |

|----------------|--------------|------------|----------|

|----------------|--------------|------------|----------|

| Figure 18-6.  | Upper Bound of the Average PSD of a 1,160 kbaud System (Source ETSI TS 101 135,  |  |  |

|---------------|----------------------------------------------------------------------------------|--|--|

|               | Formerly ETR 152)                                                                |  |  |

| Figure 18-7.  | Package Outline, 27 x 27 mm, Two-Layer Chip, 314-Pin Ball Grid Array (BGA) 18-14 |  |  |

| Figure 18-8.  | Package Outline, 15 x 15 mm, Two-Layer Chip, 208-Pin CABGA                       |  |  |

| Figure 18-9.  | Package Outline, 9 x 9 mm Two-Layer Chip, 81-Pin CABGA                           |  |  |

| Figure 18-10. | Package Outline for the 80-Pin Thin Quad Flat Pack (TQFP)                        |  |  |

List of Figures CN8980

# **List of Tables**

| Table 4-1.   | Internal 8051 Memory Map                          | 4-2         |

|--------------|---------------------------------------------------|-------------|

| Table 4-2.   | Internal 8051 Interrupt Mapping                   | 4-3         |

| Table 4-3.   | START Bit Definitions                             | 4-4         |

| Table 4-4.   | Internal 8051 Timers/Counters                     | 4-5         |

| Table 4-5.   | 8051 Communication Interfaces                     | <b>4-6</b>  |

| Table 4-6.   | Dip Switch #2 Definition                          | 4-9         |

| Table 4-7.   | DEVADR Bit Definitions                            | 4-9         |

| Table 4-8.   | BOOTOP Bit Definitions                            | -10         |

| Table 4-9.   | Boot Code API Commands                            | -15         |

| Table 4-10.  | Operational API Commands                          | -15         |

| Table 5-1.   | ZipWire2 Clocks                                   | 5-2         |

| Table 7-1.   | ZipWire2 AFE Compensation Capacitor Values        | 7-6         |

| Table 7-2.   | ZipWire2 AFE Bias Current Network Values          | 7 <b>-6</b> |

| Table 8-1.   | ZipWire2 Transceiver/Framer Signal Definitions    | <b>8-6</b>  |

| Table 8-2.   | ZipWire2 AFE Signal Descriptions                  | -15         |

| Table 9-1.   | Generic Chip Select CS7 Memory Map                | 9-1         |

| Table 9-2.   | DSL Status LED #1 Register—Write Only             | 9-2         |

| Table 9-3.   | T1/E1 Framer Output / LED #2 Register—Write Only  | 9-2         |

| Table 9-4.   | DIP Switch 3 Bit Definitions                      | 9-3         |

| Table 9-5.   | DIP Switch 4 Bit Definitions                      | 9-3         |

| Table 11-1.  | Activation Phases                                 | 1-1         |

| Table 11-2.  | EOC Message Types                                 | -14         |

| Table 11-3.  | Frame Format for HDSL2 EOC                        | -14         |

| Table 11-4.  | EOC Device Address                                | -15         |

| Table 11-5.  | Summary of EOC Request Message IDs                | -16         |

| Table 11-6.  | EOC TxQueue Status Bits                           | -24         |

| Table 11-7.  | User-Defined Message Request Information Field    | -24         |

| Table 11-8.  | User-Defined Message Response Information Field   | -25         |

| Table 11-9.  | API Over EOC Request Information Field            | -25         |

| Table 11-10. | API Over EOC Response Information Field           | -26         |

| Table 11-11. | EOC API Commands Summary                          | -28         |

| Table 12-1.  | API Manager Flag Description                      | 2-5         |

| Table 13-1.  | 2B1Q PAM4 Bit-to-Level Mapping                    | 3-1         |

| Table 13-2.  | Optis PAM16 Bit-to-Level Mapping                  | 3-2         |

| Table 14-1.  | HDSL2 Frame Structure and Overhead Bit Allocation | 4-2         |

| Table 14-2.  | 1T1 Framing                                       | 4-3         |

| Table 14-3.  | 1E1 Framing                                       | 4-4         |

| Table 14-4.  | HDSL1 Frame Structure and Overhead Bit Allocation | 4-5         |

| Table 14-5.  | 2T1 Framing                                       | 4-7         |

| Table 14-6.  | 2E1 Framing                                              | 14-8     |

|--------------|----------------------------------------------------------|----------|

| Table 14-7.  | 3E1 Framing                                              | 14-9     |

| Table 14-8.  | 1T1 Framing                                              | 14-10    |

| Table 14-9.  | 1E1 Framing                                              | 14-10    |

| Table 15-1.  | Incoming Messages from the Host Processor                | 15-4     |

| Table 15-2.  | Outgoing Messages from the 8051 Processor                | 15-4     |

| Table 15-3.  | Destination Field Specification                          | 15-5     |

| Table 15-4.  | API Opcode Type                                          | 15-5     |

| Table 15-5.  | Acknowledge Status Codes                                 | 15-6     |

| Table 15-6.  | Host Port RAM Mapping                                    | 15-9     |

| Table 15-7.  | Acknowledge Status Register (Interrupt Source Register)  | 15-11    |

| Table 15-8.  | Host Port RAM Status Mapping                             | 15-12    |

| Table 15-9.  | Host Port RAM Message Protocol Events                    | 15-13    |

| Table 15-10. | Host Processor to 8051 Processor RS232 Message Structure | 15-15    |

| Table 15-11. | RS232 Acknowledge Response Message Structure             | 15-16    |

| Table 15-12. | 8051 Processor to Host Processor RS232 Message Structure | 15-16    |

| Table 15-13. | Example 1—Incoming RS232 Message                         | 15-17    |

| Table 15-14. | Example 1—Outgoing RS232 Message                         | 15-17    |

| Table 15-15. | Example 2—Incoming RS232 Message                         | 15-17    |

| Table 15-16. | Example 2—Outgoing RS232 Message                         | 15-17    |

| Table 15-17. | Example 3—Incoming RS232 Message                         | 15-18    |

| Table 15-18. | Example 3—Outgoing RS232 Message                         | 15-18    |

| Table 16-1.  | Scrambler/Descrambler Taps                               | 16-3     |

| Table 16-2.  | CRC Tap                                                  | 16-3     |

| Table 16-3.  | Sync Word—HDSL2                                          | 16-4     |

| Table 16-4.  | Sync Word—HDSL1                                          | 16-4     |

| Table 16-5.  | Pair ID of the Z-bit Field                               | 16-4     |

| Table 16-6.  | Single Pair Configuration API Commands                   | 16-5     |

| Table 17-1.  | API Command Summary                                      | 17-2     |

| Table 17-2.  | HDSL1 Variable Rate Startup Times                        | 17-12    |

| Table 17-3.  | STATUS_1: DSL Status Bit Definitions                     | 17-23    |

| Table 17-4.  | STATUS_3: Startup Failure Status Bit Definitions         | 17-23    |

| Table 17-5.  | STATUS_4: DSL Framer Status Bit Definitions              | 17-24    |

| Table 17-6.  | STATUS_8: Acknowledge Status (ISR) Bit Definitions       | 17-24    |

| Table 17-7.  | Fatal Error Bit Definitions                              | 17-25    |

| Table 17-8.  | Tx State Bit Definitions                                 | 17-25    |

| Table 17-9.  | DEVADR / BOOPOP Bit Definitions                          | 17-40    |

| Table 17-10. | AFE Bit Definitions                                      | 17-41    |

| Table 17-11. | Test Mode Options                                        | 17-44    |

| Table 17-12. | Loopback Options                                         | 17-47    |

| Table 17-13. | DSL Framer BER Status Bits                               | 17-56    |

| Table 17-14. | PRBS Data Pattern                                        | 17-60    |

| Table 17-15. | Clear Error Counter Options                              | 17-68    |

| Table 17-16. | Inject CRC Error Options                                 | 17-74    |

| Table 17-17. | T1/E1 Framer Loopback Options                            | . 17-103 |

| Table 17-18. | Framer Silicon Types                                     | . 17-105 |

| Table 18-1. | Recommended Operating Conditions                                                                   | 18-1    |

|-------------|----------------------------------------------------------------------------------------------------|---------|

| Table 18-2. | Absolute Maximum Ratings                                                                           | 18-2    |

| Table 18-3. | ZipWire2 Transceiver/Framer Power Dissipation                                                      | 18-4    |

| Table 18-4. | Transceiver/Framer DC Characteristics                                                              | 18-4    |

| Table 18-5. | Host Port Ram Interface Timing Table                                                               | 18-6    |

| Table 18-6. | ZipWire2 AFE Power Dissipation                                                                     | 18-9    |

| Table 18-7. | AFE DC Characteristics                                                                             | 18-9    |

| Table 18-8. | Transmit Pulse Template for Two- and Three-Pair Systems (Source ETSI TS 101 135, Formerly ETR 152) | . 18-10 |

| Table 18-9. | Transmit Pulse Template for One-Pair Systems (Source ETSI TS 101 135, Formerly FTR 152)            | . 18-11 |

List of Tables CN8980

# 1.0 Introduction

This data sheet provides information for using the Conexant CN8980 ZipWire2 HDSL2/SDSL Transceiver and Framer, and ZipWire2 Analog Front-End (AFE) devices. This document discusses application and hardware interfaces. It provides detailed descriptions of the devices and pins, software information, configuration information, implementation of communication protocols, commands, and electrical and mechanical specifications.

Due to the flexibility of the ZipWire2 chip set, not all applications are addressed in this data sheet. Please contact the local sales office or technical support to determine how the ZipWire2 device can be used in your DSL application.

#### 1.1 References

*T1/E1.4 (T1E1.4/99-006)*—Draft for HDSL2 Standard *RE/TM-06011-1*—Draft for SDSL

1.1 References

# 2.0 System Overview

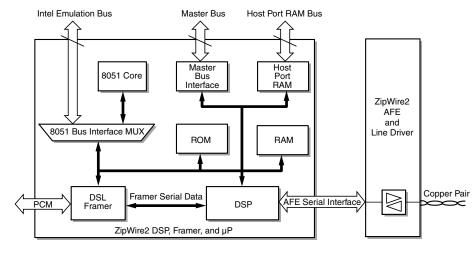

For most applications, the ZipWire2 chip set can be viewed as a pair of wires: What comes in on one terminal unit will go out the far-end terminal unit. Figure 2-1 illustrates the ZipWire2 data interfaces. The Framer Bypass and HDSL auxiliary interfaces operate at the DSL line rate. The PCM and Insert/Drop operate at the PCM clock rate. The DSL line interfaces to the physical twisted pairs.

Figure 2-1. High-Level Functional Diagram

# 2.1 ZipWire2 Transceiver/Framer Functional Summary

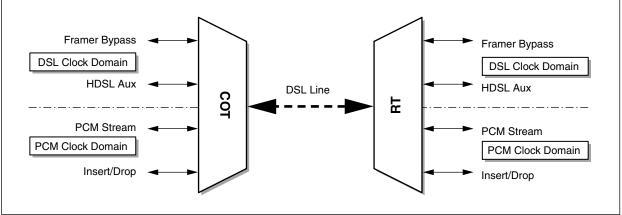

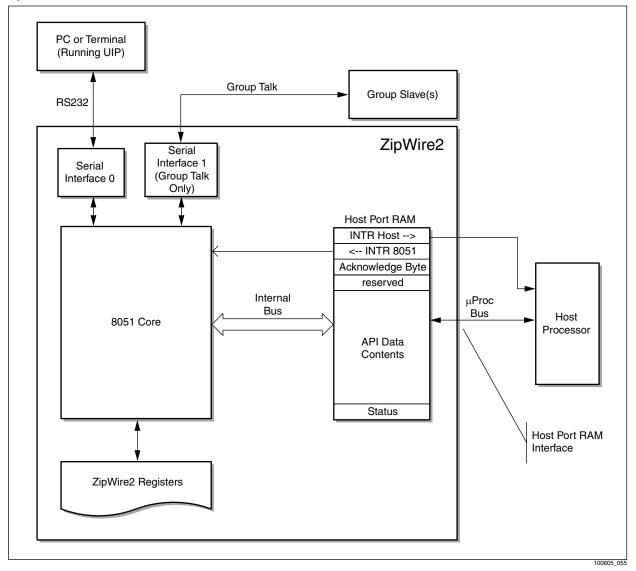

Figure 2-2 illustrates a detailed block diagram of the ZipWire2 Transceiver/Framer. The 8051 microprocessor sections contain an internal boot-up ROM, execution Program RAM (PRAM), Data Storage RAM, and address decoding. The internal 8051 is responsible for performing the transceiver startup, DSL Framer overhead management, interrupt handling, etc.

A full-featured API command set allows the user to configure the ZipWire2 system, query for status, execute loopbacks and test modes, and to dictate the program flow.

In addition to controlling the internal sections of the ZipWire2 device, the internal 8051 can be used to control other external devices, i.e., T1/E1 Framer, LEDs, and so on.

The CN8980 is available in a 2- or 3-package option. In both options, the AFE is the same. In the 2-package option the Transceiver and Framer are in a single package. In the 3-package option, the Transceiver and Framer are in separate packages.

Figure 2-2. ZipWire2 Transceiver/Framer Detailed Block Diagram

100605C **Conexant** 2-3

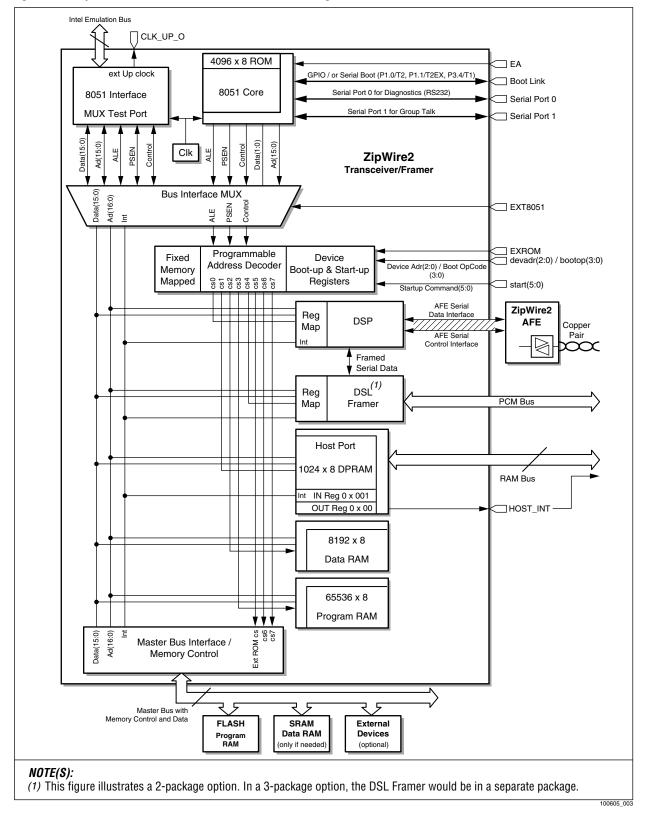

# 2.2 ZipWire2 Transceiver/DSP Functional Summary

Figure 2-3 illustrates a detailed block diagram of the ZipWire2 Transceiver/DSP section. The transmitter receives a bit stream from the DSL Framer and maps the data bits to the appropriate PAM symbols. An optional precoding block which supports both Tomlinson-Harashima precoding as well as Tomlinson-Harashima precoding combined with Trellis shaping follows the PAM mapper. The signal is then processed by the transmit filter to achieve the desired time and/or frequency domain characteristics before being forwarded to the Analog Front-End (AFE).

The receiver receives serialized data from the AFE device and from the precoded symbols from the bit pump transmitter. The precoded symbols are fed into an Echo Canceler (EC) which estimates the echo response and subtracts it from the AFE samples. The signal is then equalized using a Feed Forward Equalizer (FFE) and a Decision Feedback Equalizer (DFE). Finally, a TCM decoder is used to recover the information bits. The DFE is used only during startup. An error predictor is also used as a part of the startup algorithm and as a precoder coefficient adaptation machine during normal operation.

ZipWire2 Transceiver/DSP Section TRANSMITTER THP Precode Analog Output TX Whitening Symbol Trellis Digital D/A Filter From Encode Transmit Symbol ZipWire2 RECEIVER AFE Echo TCM .ogge To Analog Detecto DLY Input Digital A/D Frontend FELM SLM DAC & A/D Timing Clock DFF (only for

Figure 2-3. ZipWire2 Transceiver/DSP Detailed Block Diagram

acquisition)

Meters

Control

Timers

CONTROL

Test

Bus

Interface

Interface

100605 004

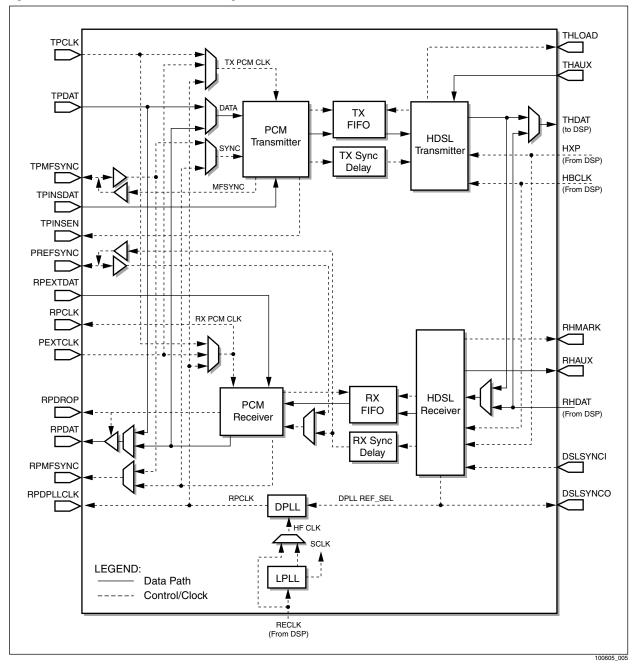

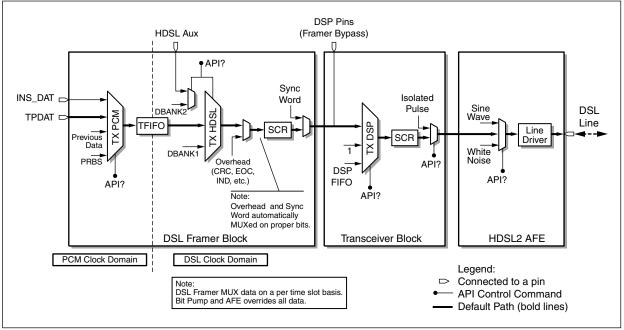

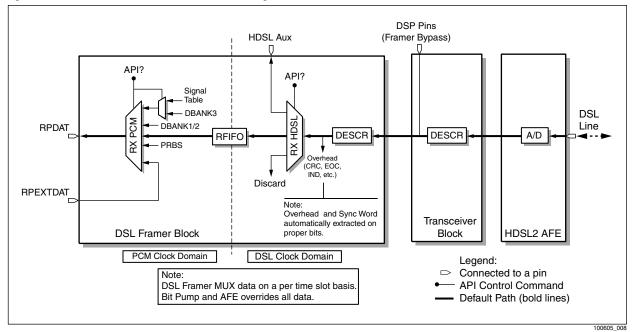

### 2.3 ZipWire2 DSL Framer Functional Summary

Figure 2-4 illustrates a detailed block diagram of the ZipWire2 DSL Framer section. The DSL Framer supports HDSL1, HDSL2, and custom frame structure applications. The DSL Framer provides clock, data, and frame format conversion from various PCM frame formats to various DSL applications. The DSL Framer supports Multi-Pair configuration such as T1 two loops, E1 two and three loops, or any Point-to-Multipoint (P2MP) application by cascading several DSL Framers. The DSL Framer provides full PCM termination capabilities, which include synchronization and management of E1 PRA and T1. The DSL rate can vary from 144 kbps up to 4,640 kbps ( $2 \times E1 + Overhead$ ), and the PCM rate can vary from 64 kbps up to 8,192 kbps ( $4 \times E1$ ) and any custom PCM rate and frame format within this range. The details of the DSL Framer section are described in Chapter 6.0.

The ZipWire2 DSL Framer can also be configured to provide T1 path termination capabilities and thereby eliminate the need for an external T1 Framer in some applications. In particular, the ZipWire2 DSL Framer is capable of generation and insertion of the T1 overhead in the transmit direction as well as alignment and checking of T1 overhead in the receive direction.

Figure 2-4. DSL Framer Detailed Block Diagram

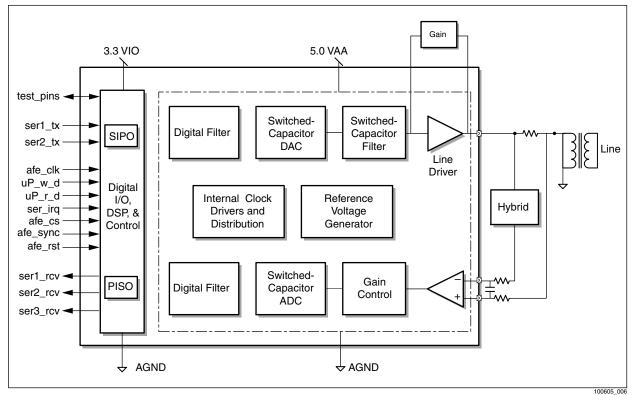

## 2.4 ZipWire2 AFE Functional Summary

Figure 2-5 illustrates a detailed block diagram of the ZipWire2 AFE. The ZipWire2 AFE performs the analog functions for transmission and reception of HDSL2 OPTIS or HDSL1 2B1Q line-code signals. ZipWire2 AFE includes the Digital-to-Analog (D/A) and Analog-to-Digital (A/D) conversion, data converter anti-aliasing and post filtering, gain control, and line driving.

The ZipWire2 AFE serial digital interface connects to the ZipWire2 Transceiver/Framer device. The serial interface protocol is proprietary. The AFE is controlled indirectly via the DSP transceiver. The analog interface consists of the line driver feedback resistors, impedance matching resistors, external hybrid, and transformer.

Figure 2-5. ZipWire2 AFE Block Diagram

## 2.5 ZipWire2 Transmit Path

Figure 2-6 illustrates the various input data sources that can be sent out the ZipWire2 link. This drawing includes all external inputs as well as internally generated data sources. This figure does not illustrate loopbacks.

Figure 2-6. Detailed Transmit Data Path Block Diagram

100605\_007

## 2.6 ZipWire2 Receive Path

Figure 2-7 illustrates the various output destinations received from the ZipWire2 link. This drawing includes all external inputs, as well as internally generated data sources. This figure does not illustrate loopbacks.

Figure 2-7. Detailed Receive Data Path Block Diagram

2.0 System Overview CN8980

2.6 ZipWire2 Receive Path

# 3.0 Application Interfaces

This section illustrates various application configurations. Each figure will illustrate different interface configurations.

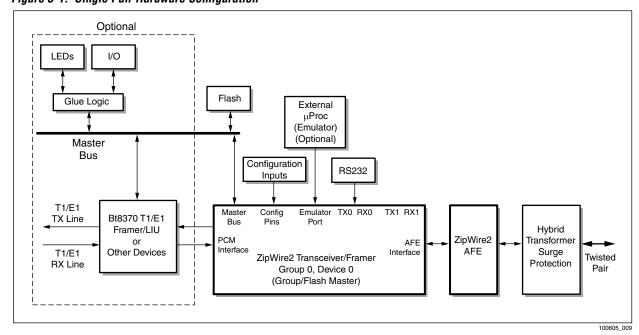

## 3.1 Using Internal 8051 Processor Only

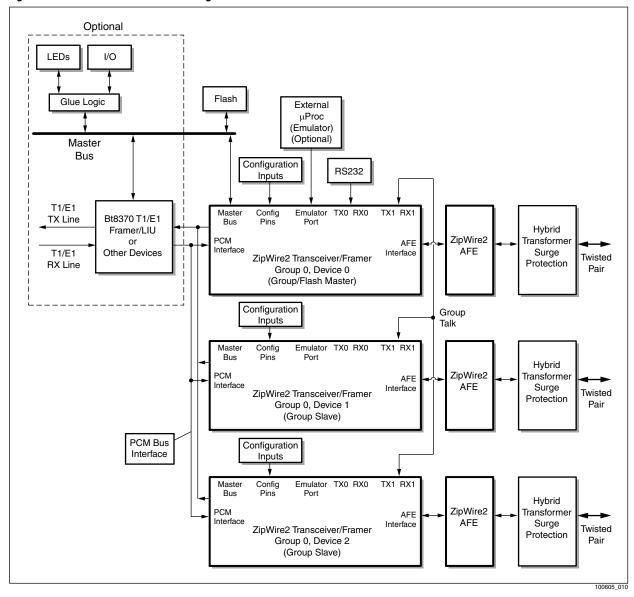

Figure 3-1 illustrates the block diagram of a single device ZipWire2 system. In this application, the ZipWire2 8051 Processor can be used to control other external devices, i.e., T1/E1 Framer. There are no other microprocessors in the system.

For applications that need to modify the 8051 Processor code, refer to the (TBD) Document. The default Flash can support the Bt8370 T1/E1 Framer, DIP Switches, LEDs, and so on. The Bt8370 would be configured for a simple transparent mode. Refer to Chapter 9.0 for more detail.

Figure 3-1. Single Pair Hardware Configuration

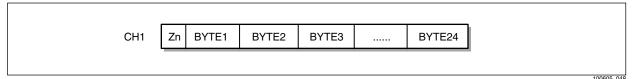

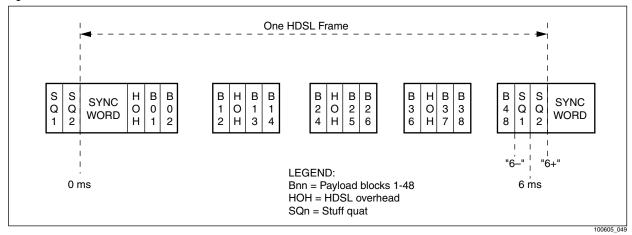

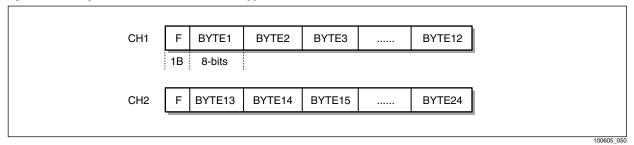

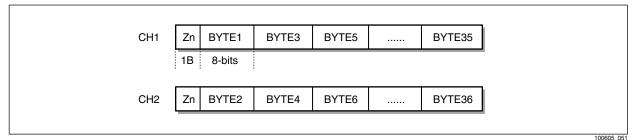

100605C **Conexant** 3-1